© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

User manual Rev. 01 — 24 June 2005 190

Philips Semiconductors

UM10120

Volume 1 Chapter 15: PWM

15.4.8 PWM Control Register (PWMPCR - 0xE001 404C)

The PWM Control Register is used to enable and select the type of each PWM channel.

The function of each of the bits are shown in

Tabl e 159.

11 PWMMR3S 1 Stop on PWMMR3: The PWMTC and PWMPC will be stopped and PWMTCR[0] will

be set to 0 if PWMMR3 matches the PWMTC.

0

0 This feature is disabled

12 PWMMR4I 1 Interrupt on PWMMR4: An interrupt is generated when PWMMR4 matches the value

in the PWMTC.

0

0 This interrupt is disabled.

13 PWMMR4R 1 Reset on PWMMR4: the PWMTC will be reset if PWMMR4 matches it. 0

0 This feature is disabled.

14 PWMMR4S 1 Stop on PWMMR4: the PWMTC and PWMPC will be stopped and PWMTCR[0] will

be set to 0 if PWMMR4 matches the PWMTC.

0

0 This feature is disabled

15 PWMMR5I 1 Interrupt on PWMMR5: An interrupt is generated when PWMMR5 matches the value

in the PWMTC.

0

0 This interrupt is disabled.

16 PWMMR5R 1 Reset on PWMMR5: the PWMTC will be reset if PWMMR5 matches it. 0

0 This feature is disabled.

17 PWMMR5S 1 Stop on PWMMR5: the PWMTC and PWMPC will be stopped and PWMTCR[0] will

be set to 0 if PWMMR5 matches the PWMTC.

0

0 This feature is disabled

18 PWMMR6I 1 Interrupt on PWMMR6: an interrupt is generated when PWMMR6 matches the value

in the PWMTC.

0

0 This interrupt is disabled.

19 PWMMR6R 1 Reset on PWMMR6: the PWMTC will be reset if PWMMR6 matches it. 0

0 This feature is disabled.

20 PWMMR6S 1 Stop on PWMMR6: the PWMTC and PWMPC will be stopped and PWMTCR[0] will

be set to 0 if PWMMR6 matches the PWMTC.

0

0 This feature is disabled

31:21 - Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

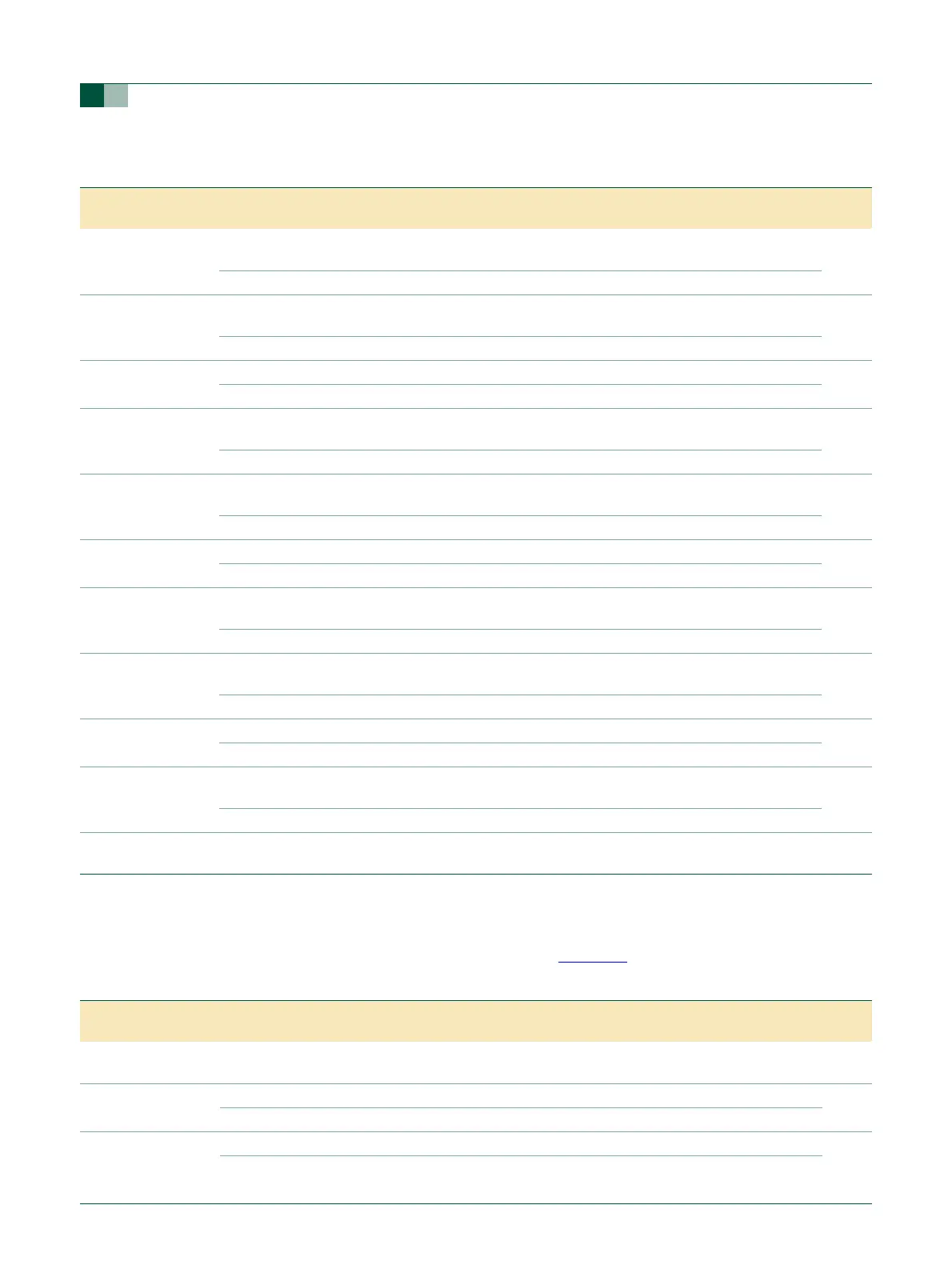

Table 158: Match Control Register (MCR, TIMER0: T0MCR - address 0xE000 4014 and TIMER1: T1MCR - address

0xE000 8014) bit description

Bit Symbol Value Description Reset

value

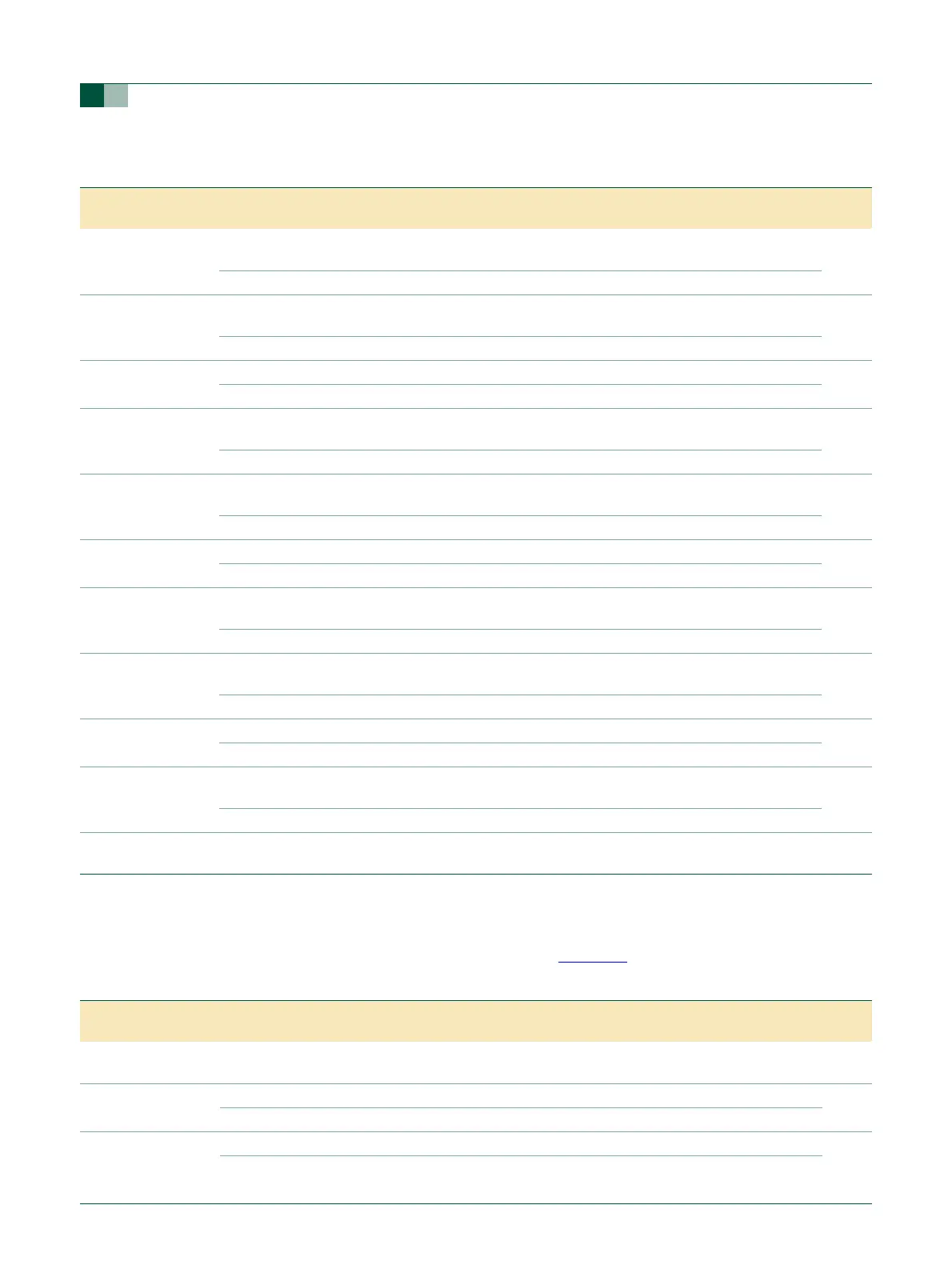

Table 159: PWM Control Register (PWMPCR - address 0xE001 404C) bit description

Bit Symbol Value Description Reset

value

1:0 - Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

2 PWMSEL2 1 Selects double edge controlled mode for the PWM2 output. 0

0 Selects single edge controlled mode for PWM2.

3 PWMSEL3 1 Selects double edge controlled mode for the PWM3 output. 0

0 Selects single edge controlled mode for PWM3.

Loading...

Loading...