CIRCUIT DESCRIPTION

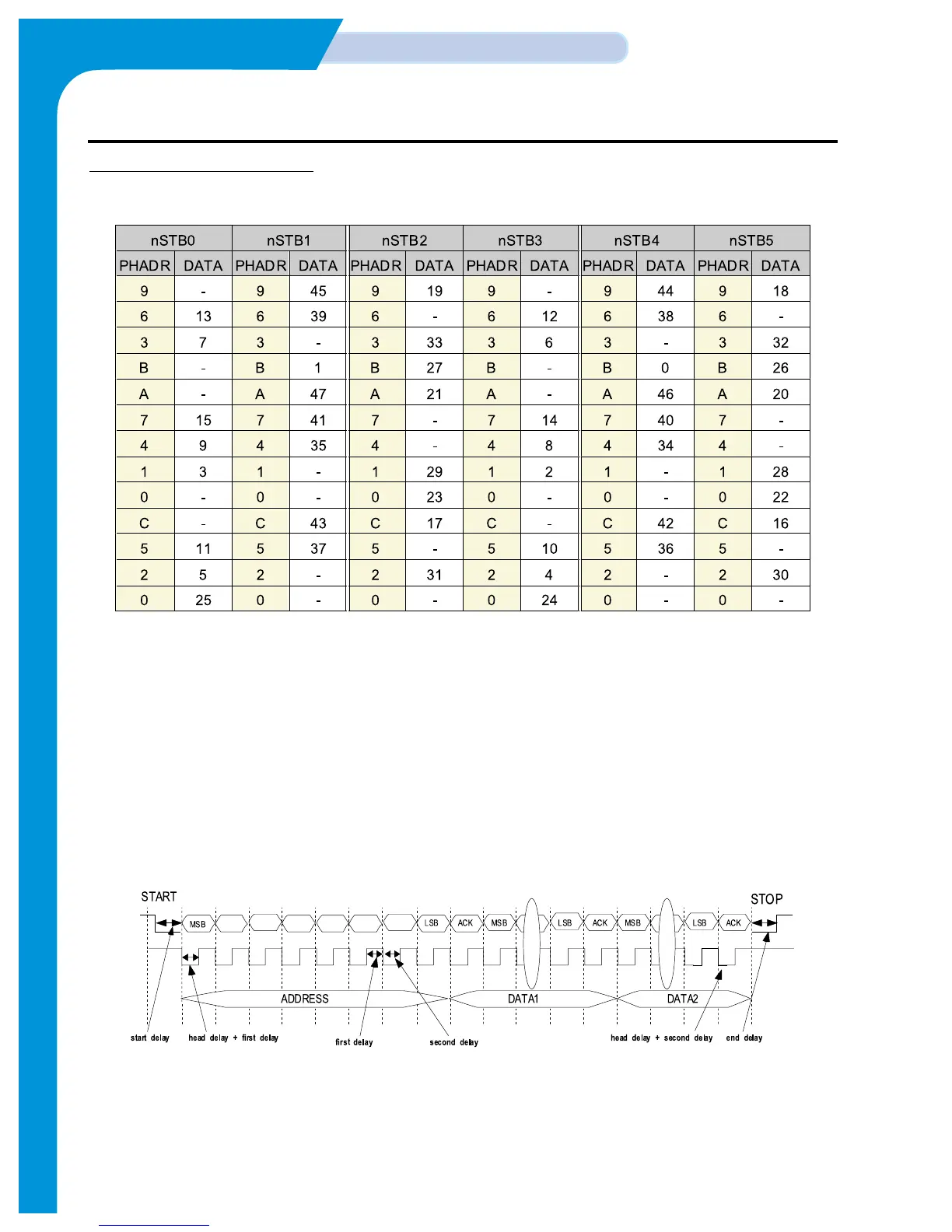

2. HEAD DATA OUTPUT FORMAT

The 1 slice data [47:0] from the HDMA is outputted with the PHADR in order as below.

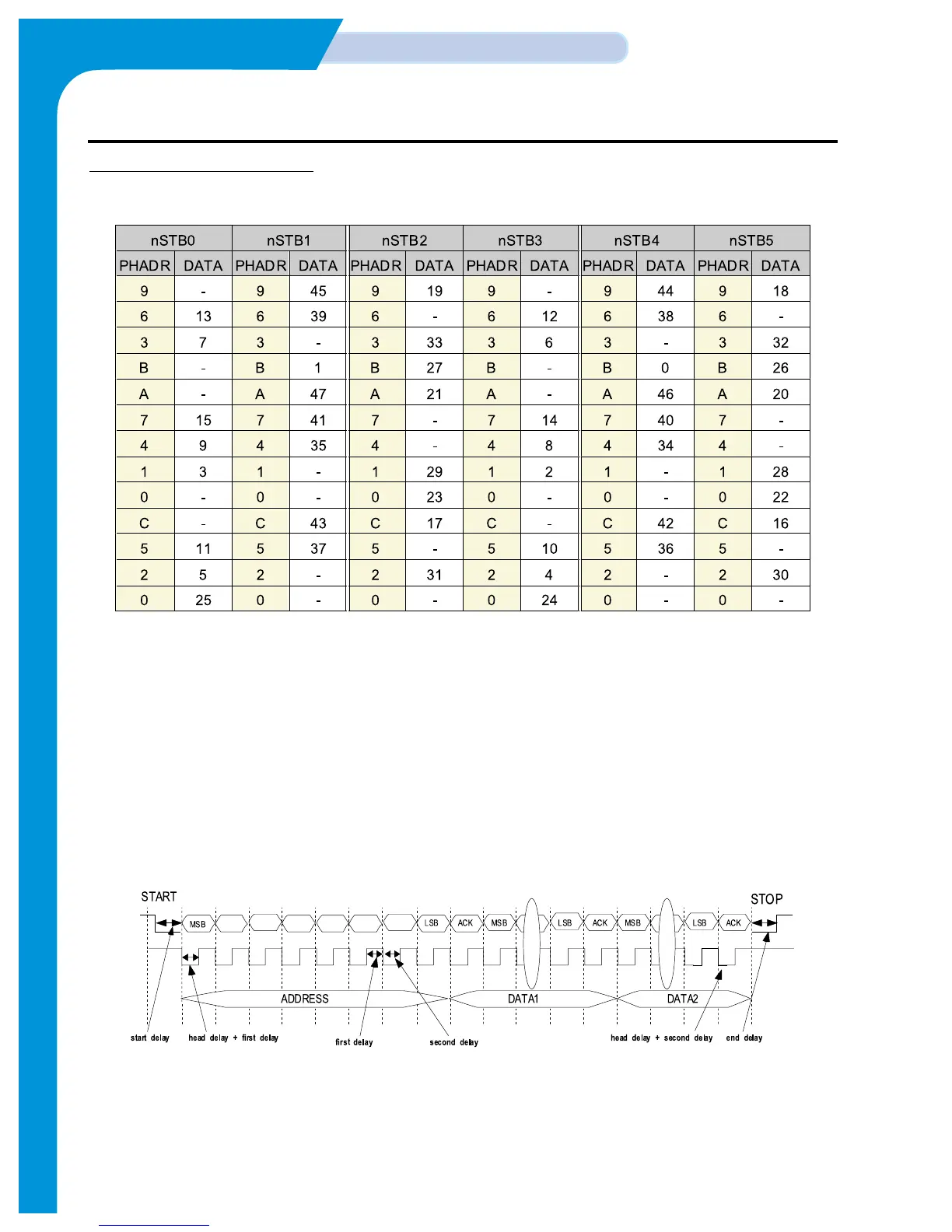

<9> SYNCHRONOUS SERIAL INTERFACE PART

It interfaces with Quarter-horse ASIC and consists of SMIC, SMID, PWM, and _RST. The Quarter-horse is the

Motor Driver IC. The Quarter-horse interface Logic makes the data as a serial for transmitting the data to the

Quarter-horse, and transmits the serial to the Quarter-horse IC by controlling it with the arranged Protocol. The

Quarter-horse uses two signals, SMIC (clock) and SMID (data) to transmit the data. It transmits 3 bytes at once,

and the 3 bytes mean the Device Address, Data 1, and Data 2. It is transmitted from MSB to LSB. The Quarter-

horse sends the ACK signal at the end of the each byte to confirm the transmitted data. In case of no receiving

ACK signal, the Quarter-horse_interface Logic sends the 3 bytes again. Depending on the level of the SMIC and

SMID signals, the different messages are shown.

If it is high (SMIC) and high (SMID), it means the IDLE condition which means no data is received, if it is high

(SMIC) and high-to-low-transition (SMID), it means the data transfer is started, and if it is high (SMIC) and low-to-

high-transition (SMID), it means the last data transfer.

Loading...

Loading...