- 189 -

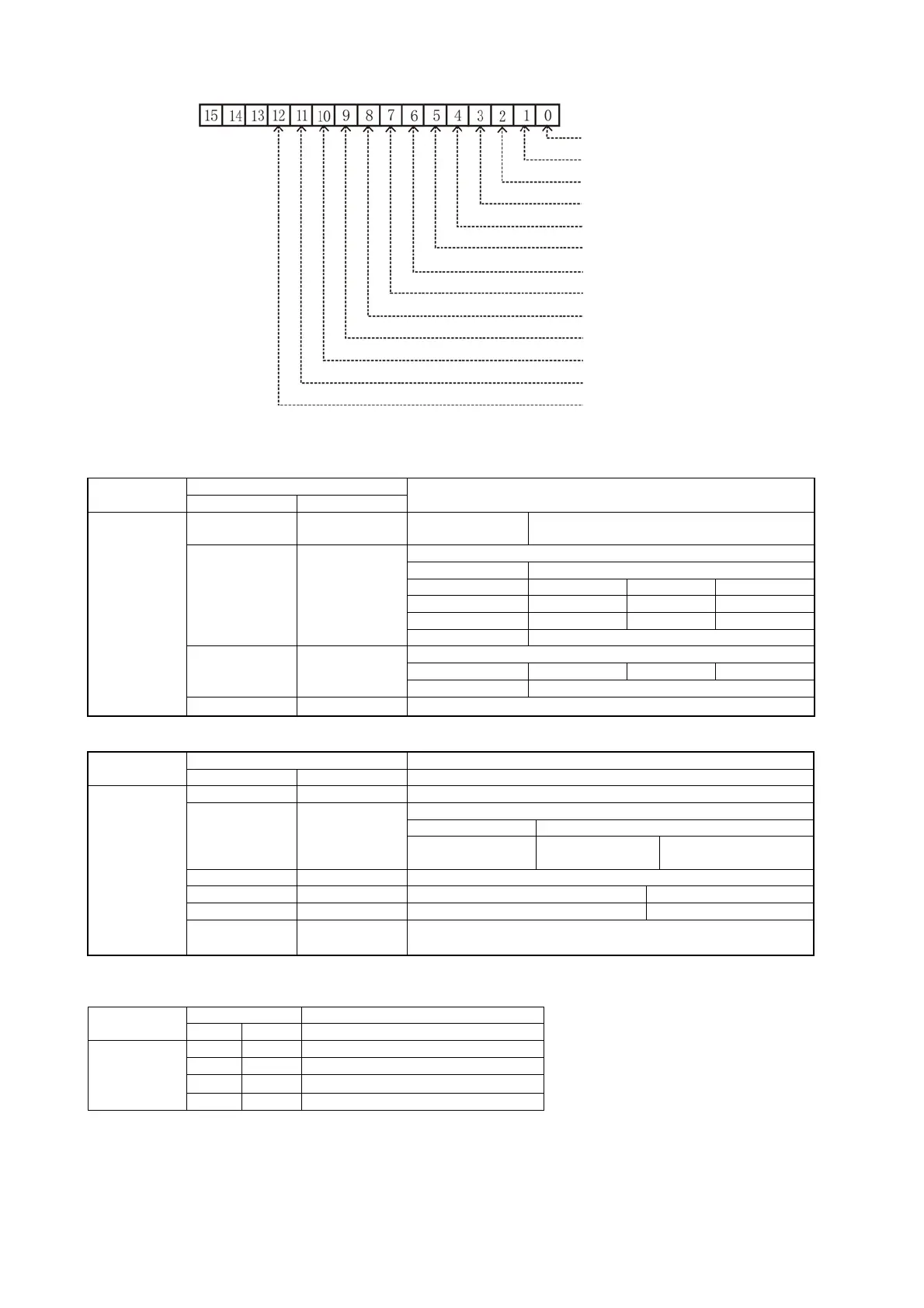

FL-STFLG bit formation

Vslow JOG

DC braking

Braking excitation (only vector mode)

Starting excitation (only vector mode)

Stop deceleration

Raising frequency

Lowering frequency

Matching frequency

Matching speed (only vector mode)

Reverse run

Gate ON (during operation)

Frequency locked

Standby

※ b13-b31 is system reserved.

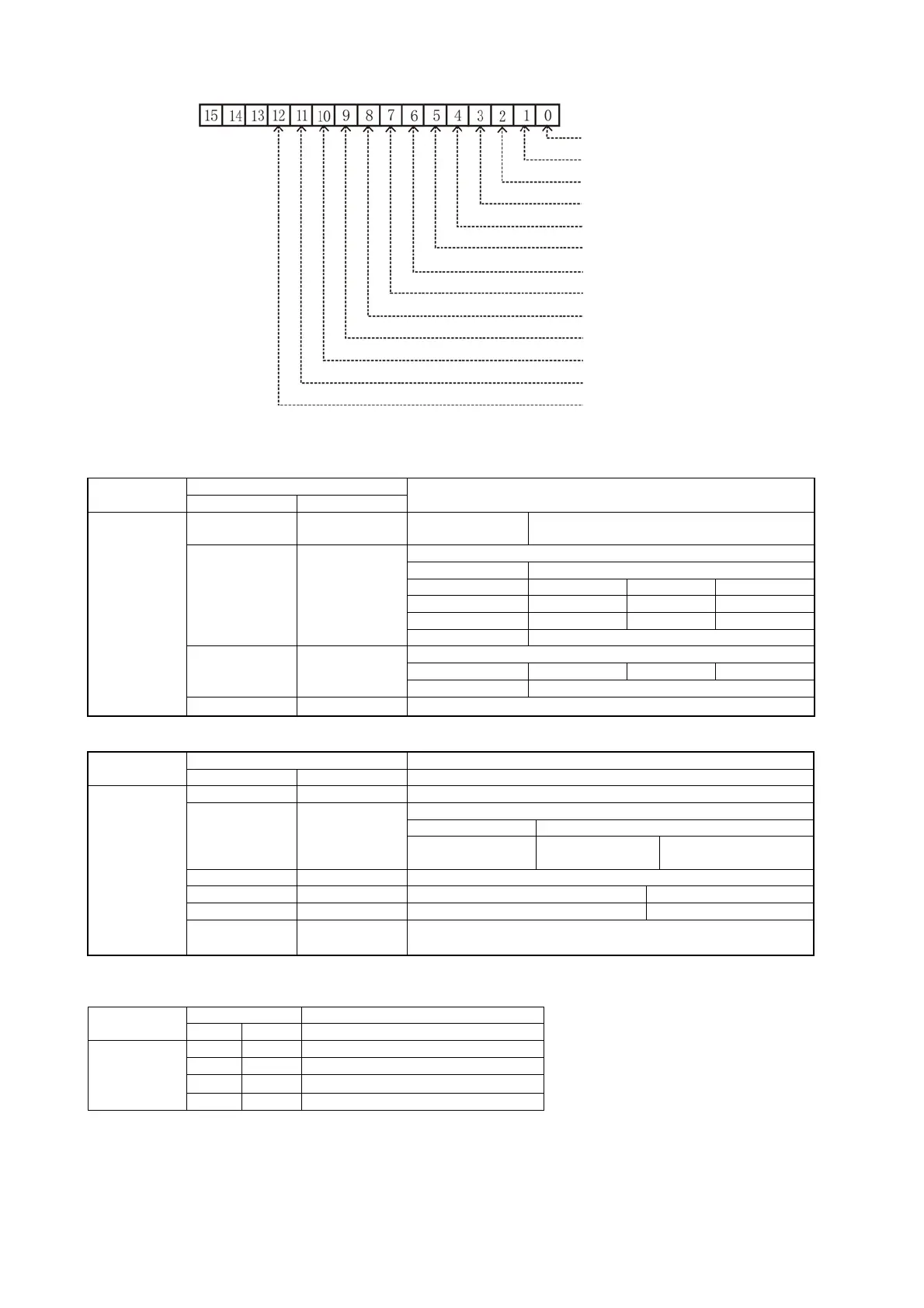

■Writing register address (F4103=2: register number is B)

Register No.

Processing

method

DEC HEX

Description

9500 251CH

Frequency

command

Setting of target frequency (1

st

speed)

Operation command

BIT 0 Not used

BIT 1 Forward run 1=Enabled 0=Disabled

BIT 2 Reverse run 1=Enabled 0=Disabled

BIT 3 Stop 1=Enabled 0=Disabled

9501 251DH

BIT4 and above Not used

Reset command

BIT 0 Alarm reset 1=Enabled 0=Disabled

9502 251EH

BIT1 and above Not used

Writing

9503~9509 251FH~2525H

System reserved

■Batch operation register address (F4103=2: register number is B)

Register No. Description Processing

method

DEC HEX

9700 25E4H Selecting inverters for batch operation

Specifying direction of rotation for inverters in batch control

9701 Selecting inverters for batch control

9701~9702 25E5H~25E6H

9702

Direction of

rotation

1=Forward; 2=Reverse

9703 25E7H Releasing inverters in batch operation

9704 25E8H Batch start 1=Start

9705 25E9H Batch stop 1=Stop

Batch

operation

9706~9709

25EAH~

25EDH

System reserved

■Function code register address (F4103=2: register number is B)

Register number is used to set the value of “function code number”.

Register No. Description

Processing

method

DEC HEX

1001 03E9H Function code F1001

1002 03EAH Function code F1002

… … …

Reading

Writing

8999 2327H Function code F8999

Loading...

Loading...