CPUs

1-47

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

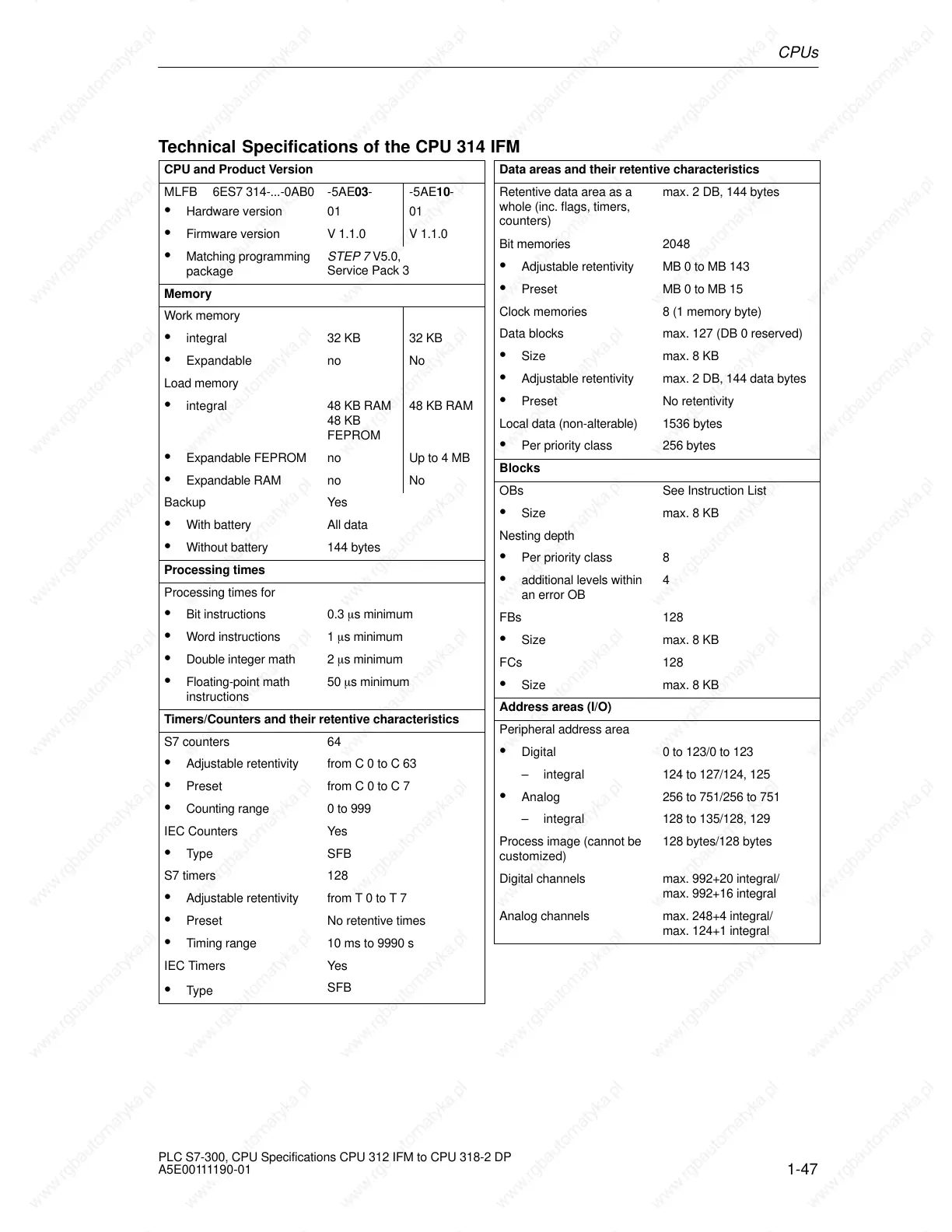

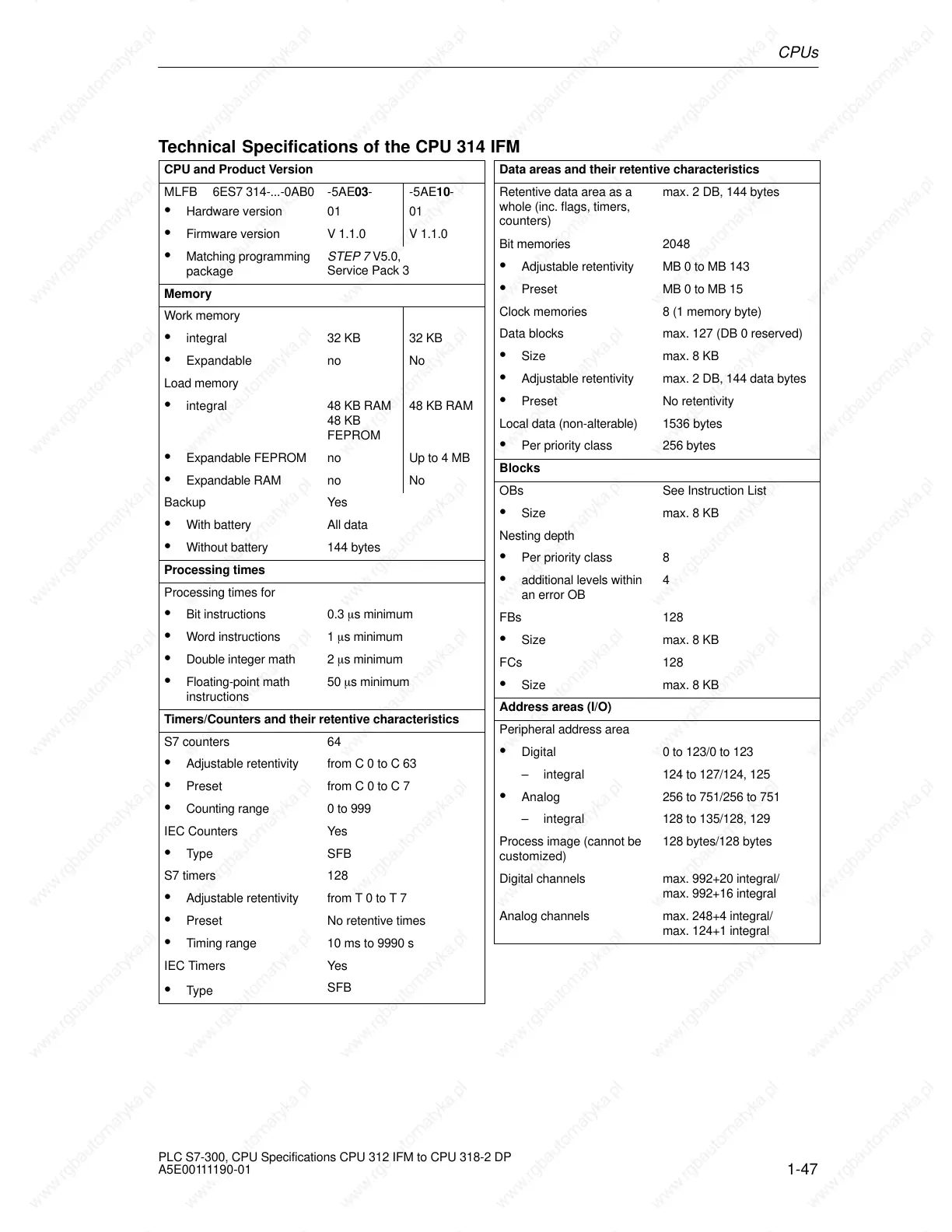

Technical Specifications of the CPU 314 IFM

CPU and Product Version

MLFB 6ES7 314-...-0AB0

Hardware version

-5AE03-

01

-5AE10-

01

Firmware version V 1.1.0 V 1.1.0

Matching programming

package

STEP 7 V5.0,

Service Pack 3

Memory

Work memory

integral 32 KB 32 KB

Expandable no No

Load memory

integral 48 KB RAM

48 KB

FEPROM

48 KB RAM

Expandable FEPROM no Up to 4 MB

Expandable RAM no No

Backup Yes

With battery All data

Without battery 144 bytes

Processing times

Processing times for

Bit instructions 0.3 s minimum

Word instructions 1 s minimum

Double integer math 2 s minimum

Floating-point math

instructions

50 s minimum

Timers/Counters and their retentive characteristics

S7 counters 64

Adjustable retentivity from C 0 to C 63

Preset from C 0 to C 7

Counting range 0 to 999

IEC Counters Yes

Type SFB

S7 timers 128

Adjustable retentivity from T 0 to T 7

Preset No retentive times

Timing range 10 ms to 9990 s

IEC Timers Yes

Type

SFB

Data areas and their retentive characteristics

Retentive data area as a

whole (inc. flags, timers,

counters)

max. 2 DB, 144 bytes

Bit memories 2048

Adjustable retentivity MB 0 to MB 143

Preset MB 0 to MB 15

Clock memories 8 (1 memory byte)

Data blocks max. 127 (DB 0 reserved)

Size max. 8 KB

Adjustable retentivity max. 2 DB, 144 data bytes

Preset No retentivity

Local data (non-alterable) 1536 bytes

Per priority class 256 bytes

Blocks

OBs See Instruction List

Size max. 8 KB

Nesting depth

Per priority class 8

additional levels within

an error OB

4

FBs 128

Size max. 8 KB

FCs 128

Size max. 8 KB

Address areas (I/O)

Peripheral address area

Digital 0 to 123/0 to 123

– integral 124 to 127/124, 125

Analog 256 to 751/256 to 751

– integral 128 to 135/128, 129

Process image (cannot be

customized)

128 bytes/128 bytes

Digital channels max. 992+20 integral/

max. 992+16 integral

Analog channels max. 248+4 integral/

max. 124+1 integral

Loading...

Loading...