CPUs

1-28

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

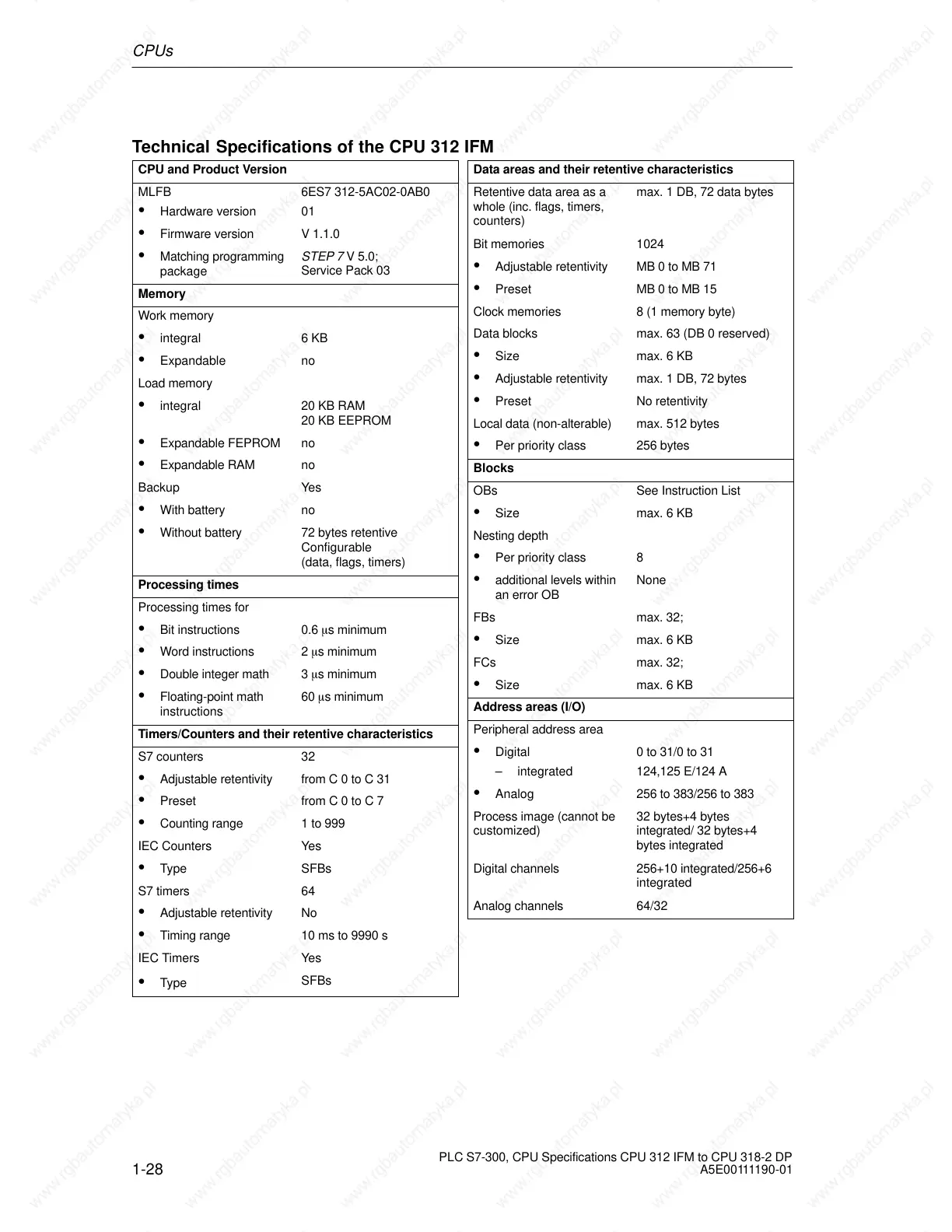

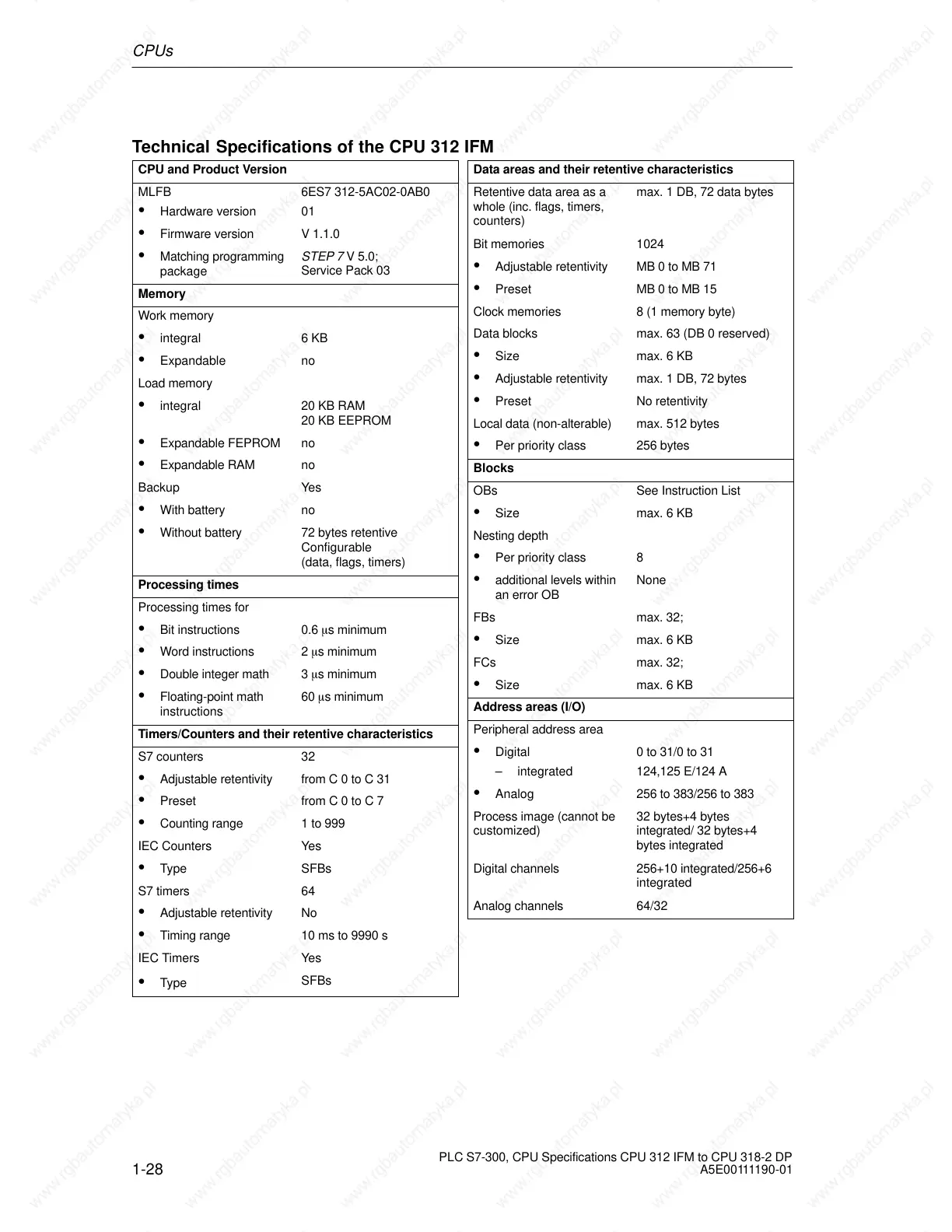

Technical Specifications of the CPU 312 IFM

CPU and Product Version

MLFB

Hardware version

6ES7 312-5AC02-0AB0

01

Firmware version V 1.1.0

Matching programming

package

STEP 7 V 5.0;

Service Pack 03

Memory

Work memory

integral 6 KB

Expandable no

Load memory

integral 20 KB RAM

20 KB EEPROM

Expandable FEPROM no

Expandable RAM no

Backup Yes

With battery no

Without battery 72 bytes retentive

Configurable

(data, flags, timers)

Processing times

Processing times for

Bit instructions 0.6 s minimum

Word instructions 2 s minimum

Double integer math 3 s minimum

Floating-point math

instructions

60 s minimum

Timers/Counters and their retentive characteristics

S7 counters 32

Adjustable retentivity from C 0 to C 31

Preset from C 0 to C 7

Counting range 1 to 999

IEC Counters Yes

Type SFBs

S7 timers 64

Adjustable retentivity No

Timing range 10 ms to 9990 s

IEC Timers Yes

Type

SFBs

Data areas and their retentive characteristics

Retentive data area as a

whole (inc. flags, timers,

counters)

max. 1 DB, 72 data bytes

Bit memories 1024

Adjustable retentivity MB 0 to MB 71

Preset MB 0 to MB 15

Clock memories 8 (1 memory byte)

Data blocks max. 63 (DB 0 reserved)

Size max. 6 KB

Adjustable retentivity max. 1 DB, 72 bytes

Preset No retentivity

Local data (non-alterable) max. 512 bytes

Per priority class 256 bytes

Blocks

OBs See Instruction List

Size max. 6 KB

Nesting depth

Per priority class 8

additional levels within

an error OB

None

FBs max. 32;

Size max. 6 KB

FCs max. 32;

Size max. 6 KB

Address areas (I/O)

Peripheral address area

Digital

– integrated

0 to 31/0 to 31

124,125 E/124 A

Analog 256 to 383/256 to 383

Process image (cannot be

customized)

32 bytes+4 bytes

integrated/ 32 bytes+4

bytes integrated

Digital channels 256+10 integrated/256+6

integrated

Analog channels 64/32

Loading...

Loading...