TANDY

COMPUTER PRODUCTS

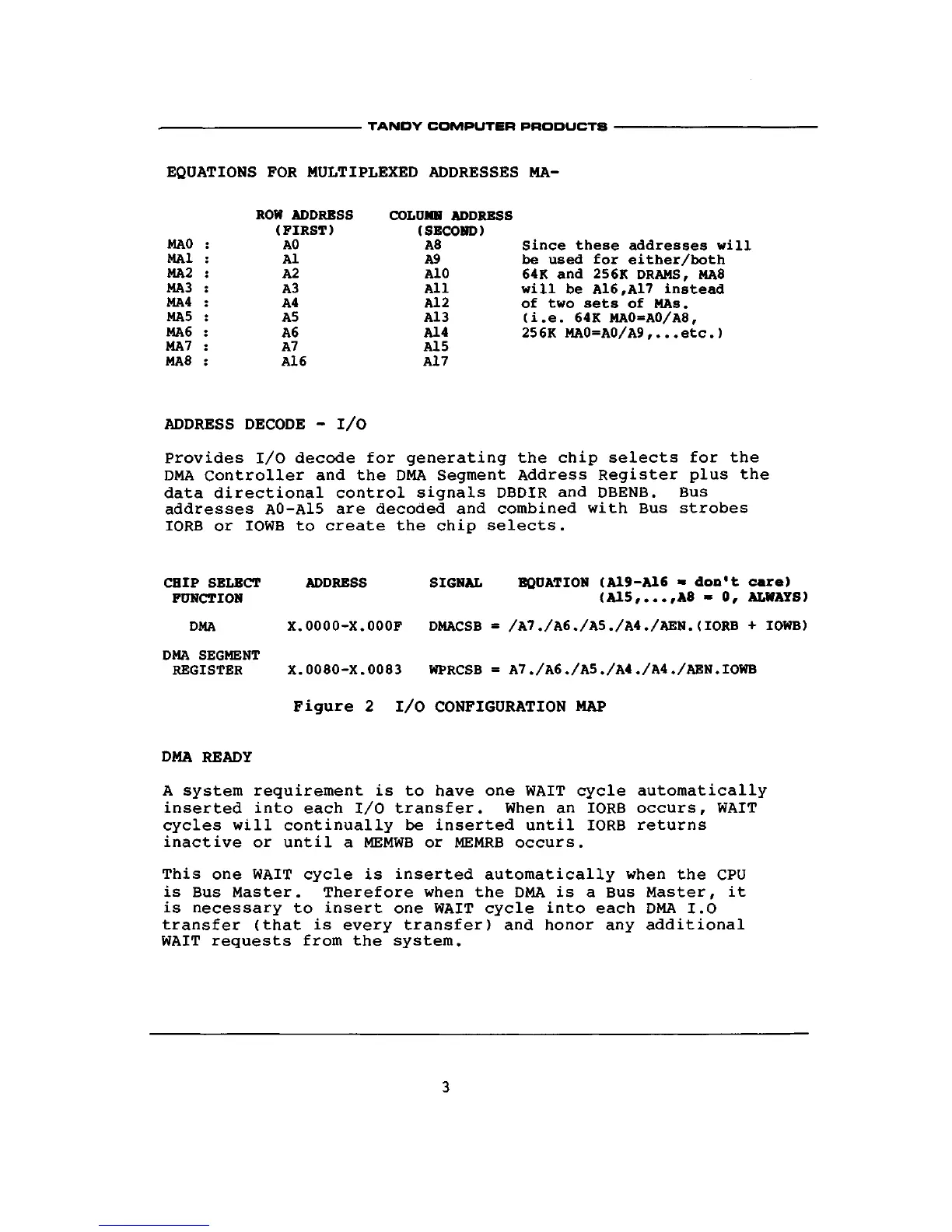

EQUATIONS FOR MULTIPLEXED ADDRESSES MA-

MAO

:

MAI

:

MA2

:

MA3

:

MA4

:

MA5

:

MA6

:

MA7

:

MA8

:

ROW ADDRESS

(FIRST)

AO

Al

A2

A3

A4

A5

A6

A7

A16

COLUMN ADDRESS

(SECOND)

A8

A9

A10

All

A12

A13

A14

A15

A17

Since these addresses will

be used

for

either/both

64K and 256K DRAMS, MA8

will

be

A16,A17 instead

of two sets

of

MAs.

(i.e.

64K MA0=A0/A8,

256K MA0=A0/A9,...etc.)

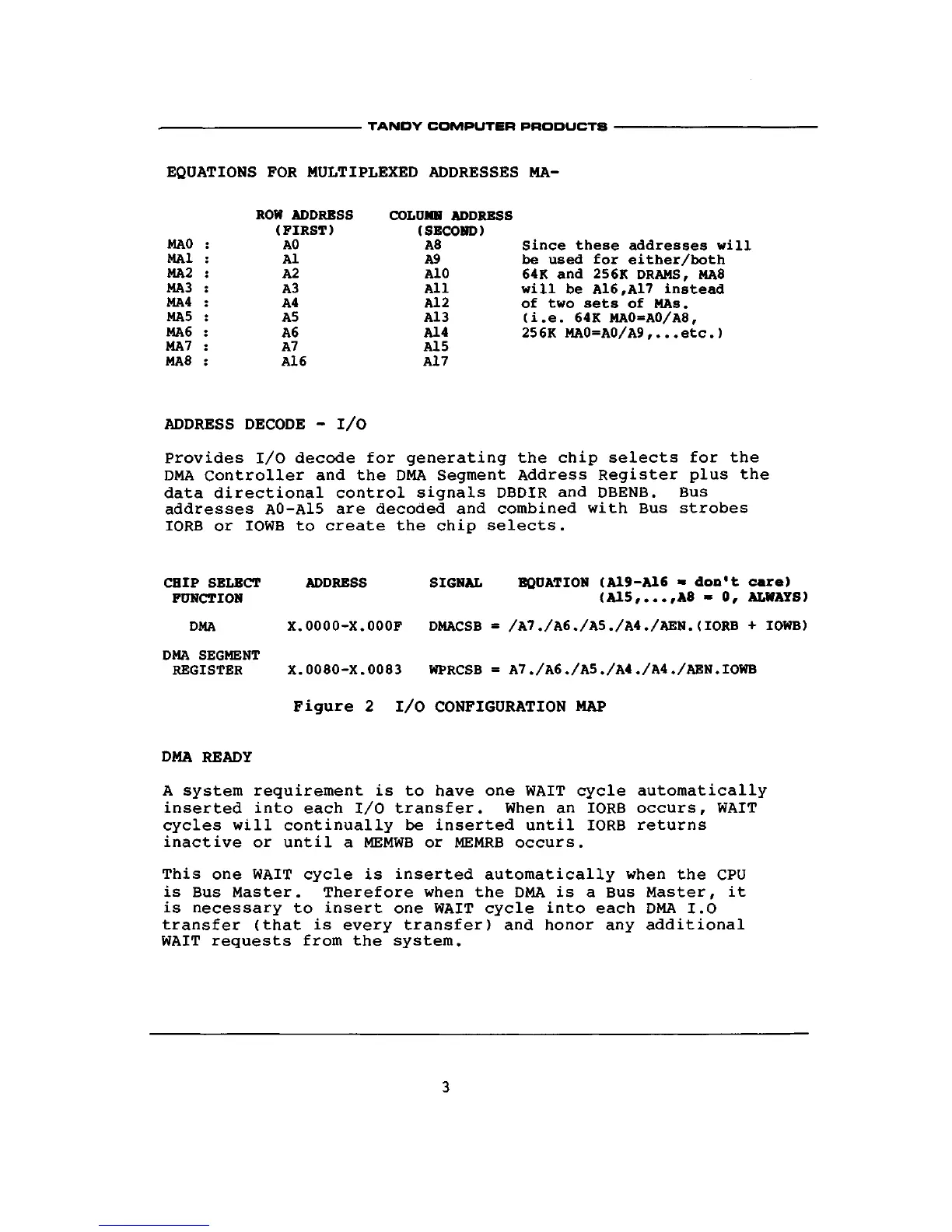

ADDRESS DECODE

- I/O

Provides I/O decode for generating the chip selects for the

DMA Controller and the DMA Segment Address Register plus the

data directional control signals DBDIR and DBENB. Bus

addresses A0-A15 are decoded and combined with Bus strobes

IORB or IOWB to create the chip selects.

CHIP SELECT

FUNCTION

DMA

DMA SEGMENT

REGISTER

ADDRESS SIGNAL EQUATION (A19-A16

»

don't care)

(A15,...,A8

-

0, ALWAYS)

X.0000-X.000F DMACSB

=

/A7./A6./A5./A4./AEN.(IORB

+

IOWB)

X.0080-X.0083 WPRCSB

=

A7,/A6./A5,/A4./A4./AEN.IOWB

Figure

2 I/O

CONFIGURATION MAP

DMA READY

A system requirement

is to

have one WAIT cycle automatically

inserted into each

I/O

transfer. When

an

IORB occurs, WAIT

cycles will continually

be

inserted until IORB returns

inactive

or

until

a

MEMWB

or

MEMRB occurs.

This one WAIT cycle

is

inserted automatically when the CPU

is Bus Master. Therefore when the DMA

is a

Bus Master,

it

is necessary

to

insert one WAIT cycle into each DMA

1.0

transfer (that

is

every transfer) and honor any additional

WAIT requests from the system.

Loading...

Loading...