Command Groups

2–26

TDS Family Oscilloscope Programmer Manual

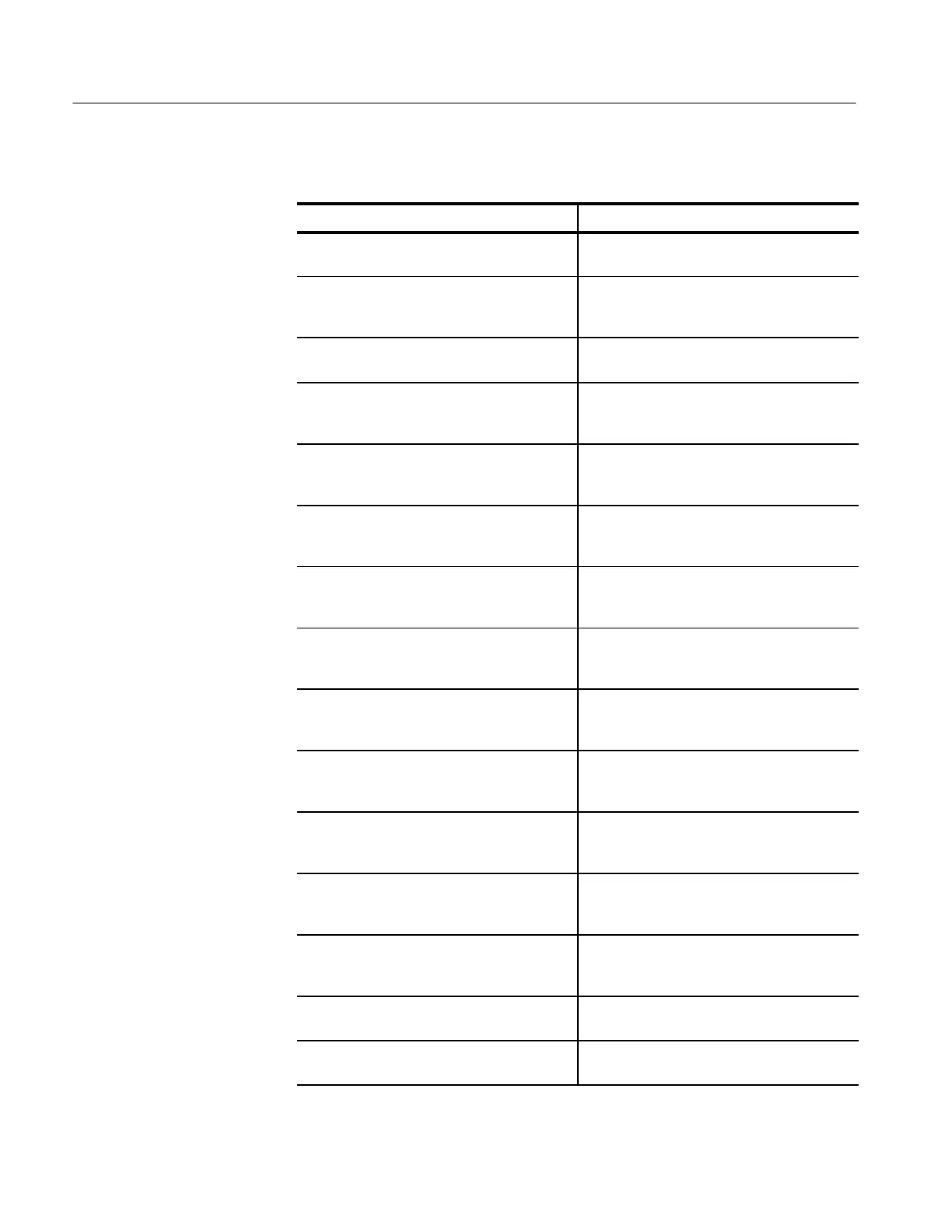

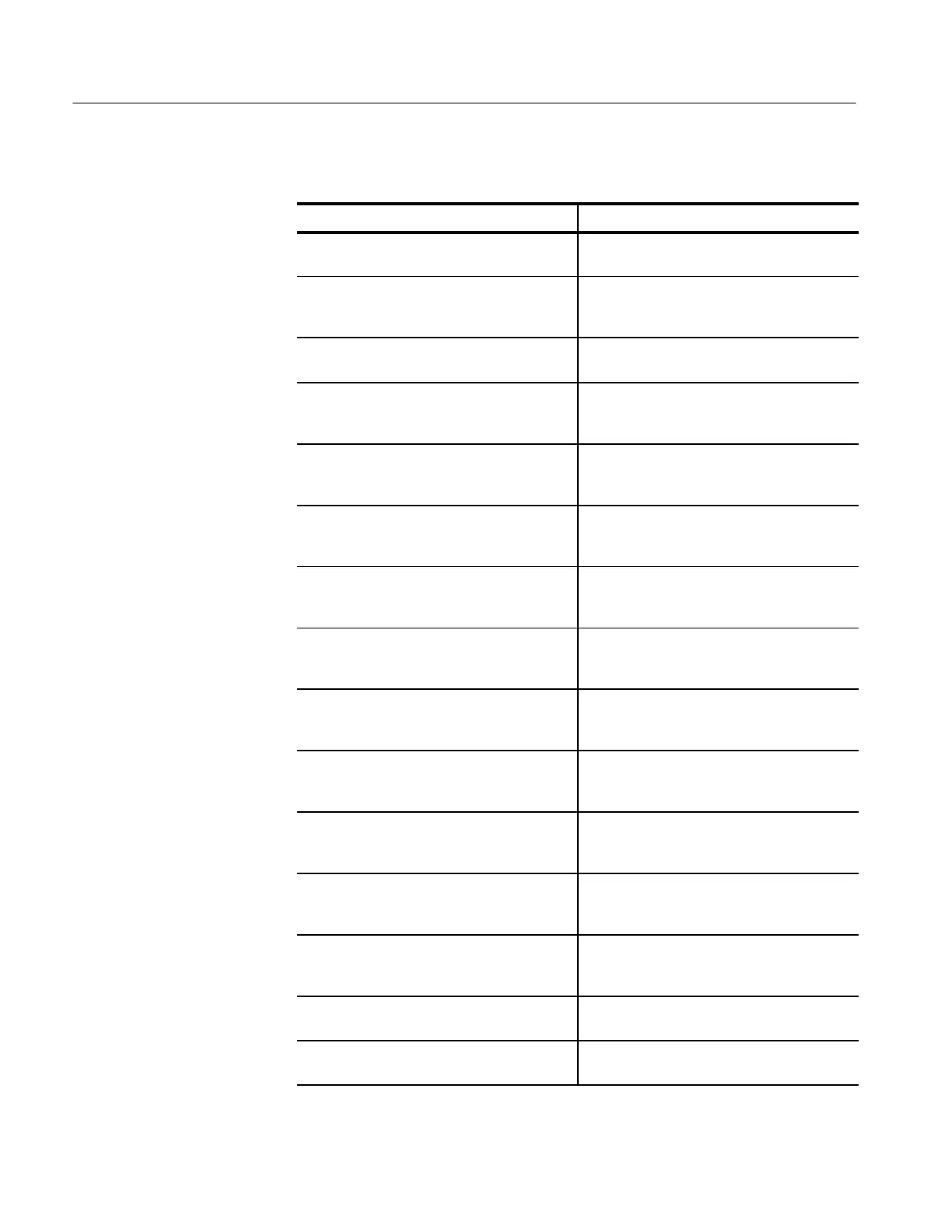

Table 2–19: Trigger Commands (Cont.)

Header Description

TRIGger:MAIn:LOGIc:INPut:CH<x>

(TDS 5XXA, 6XXA, & 7XXA)

Logic trigger expected channel state

TRIGger:MAIn:LOGIc:PATtern:

INPut:CH4

(TDS 5XXA, 6XXA, & 7XXA)

Logic trigger expected for channel 4 pattern

class

TRIGger:MAIn:LOGIc:PATtern:WHEn

(TDS 5XXA, 6XXA, & 7XXA)

Main logic pattern trigger condition

TRIGger:MAIn:LOGIc:PATtern

:WHEn:LESSLimit

(TDS 5XXA, 6XXA, & 7XXA)

Maximum time the selected pattern may be

true and still generate main logic pattern

trigger

TRIGger:MAIn:LOGIc:PATtern

:WHEn:MORELimit

(TDS 5XXA, 6XXA, & 7XXA)

Minimum time the selected pattern may be

true and still generate main logic pattern

trigger

TRIGger:MAIn:LOGIc:SETHold:

CLOCk:EDGE

(TDS 684A & 7XXA)

Clock edge polarity for setup and hold violation

triggering

TRIGger:MAIn:LOGIc:SETHold:

CLOCk:LEVel

(TDS 684A & 7XXA)

Setup/Hold clock voltage trigger level.

TRIGger:MAIn:LOGIc:SETHold:

CLOCk:SOUrce

(TDS 684A & 7XXA)

Setup/Hold clock input source

TRIGger:MAIn:LOGIc:SETHold:

DATa:LEVel

(TDS 684A & 7XXA)

Setup/Hold data level

TRIGger:MAIn:LOGIc:SETHold:

DATa:SOUrce

(TDS 684A & 7XXA)

Setup/Hold data input data channel

TRIGger:MAIn:LOGIc:SETHold:

HOLDTime

(TDS 684A & 7XXA)

Setup/Hold trigger hold time

TRIGger:MAIn:LOGIc:SETHold:

SETTime

(TDS 684A & 7XXA)

Setup/Hold trigger set time

TRIGger:MAIn:LOGIc:STATE:INPut:

CH4

(TDS 5XXA, 6XXA, & 7XXA)

Logic trigger expected for channel 4 state

class

TRIGger:MAIn:LOGIc:STATE:WHEn

(TDS 5XXA, 6XXA, & 7XXA)

When the logic trigger occurs (on true or false)

TRIGger:MAIn:LOGIc:THReshold?

(TDS 5XXA, 6XXA, & 7XXA)

Return main logic thresholds

Loading...

Loading...