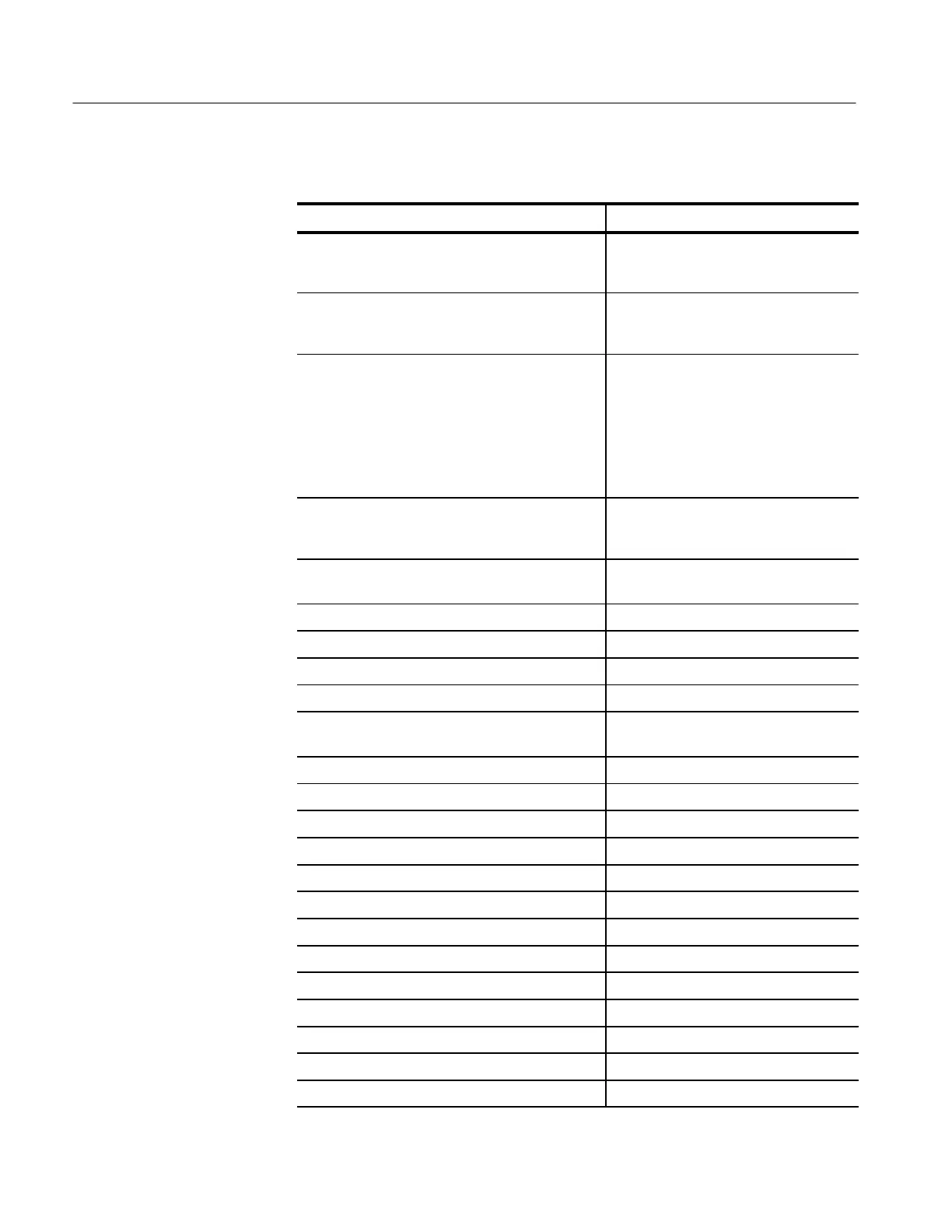

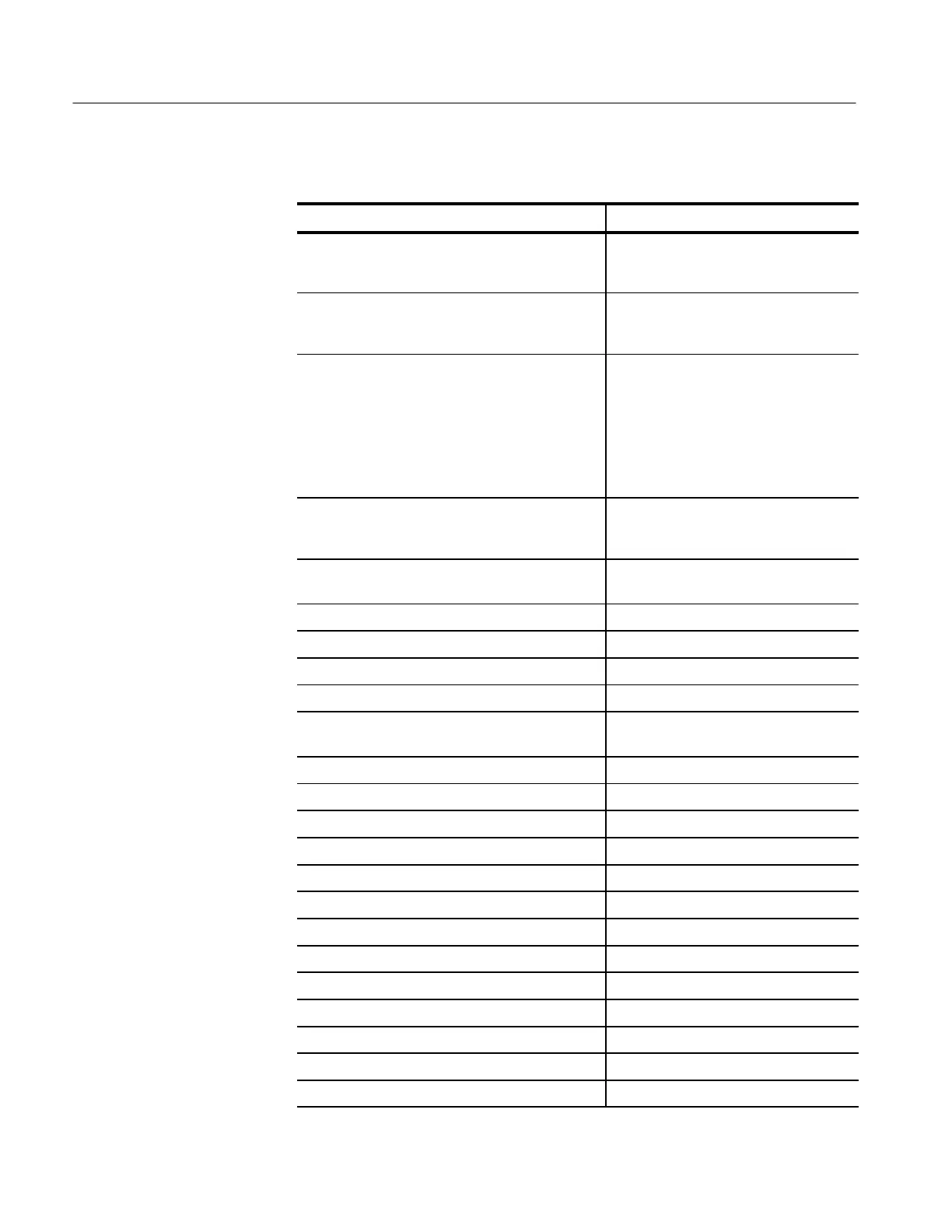

Appendix D: Factory Initialization Settings

D–4

TDS 500B, TDS 600B, & TDS 700A User Manual

Table D–1: Factory Initialization Defaults (Cont.)

Control Changed by Factory Init to

Logic trigger pattern time qualification

Lower limit

Upper limit

5 ns

5 ns

Logic trigger Setup/Hold times

Setup

Hold

3 ns

2 ns

Logic trigger sources and levels

(Setup/Hold)

Data Source = Channel 1 = 1.4 V

Clock Source = Channel 2 = 1.4 V

(Source levels are clipped to 1.2 V at the

default volts/division setting established

by Factory Init)

Clock Edge = Rising

Logic trigger threshold (all channels)

(pattern, state, and Setup/Hold)

1.4 V

(clipped to 1.2 V at the default volts/divi-

sion setting when no 10X probe attached)

Logic trigger triggers when ...

(pattern and state)

Goes TRUE

Main trigger mode Auto

Main trigger type Edge

Math1 definition Ch 1 + Ch 2

Math1 extended processing No extended processing

Math2 definition Ch 1 – Ch 2 (FFT of Ch 1 for instruments

with Option 2F Advanced DSP Math)

Math2 extended processing No extended processing

Math3 definition Inv of Ch 1

Math3 extended processing No extended processing

Measure delay edges Both rising and forward searching

Measure delay to Channel 1 (Ch1)

Measure gating Off

Measure high ref 90% and 0 V (units)

Measure high-low setup Histogram

Measure low ref 10% and 0 V (units)

Measure mid ref 50% and 0 V (units)

Measure mid2 ref 50% and 0 V (units)

Pulse glitch filter state On (Accept glitch)

Pulse glitch trigger polarity Positive

Loading...

Loading...