Theory of Oper ation

Power Distribu

tion is not shown in the block diagram but is covered at the end of

this section.

Serial Digital Input

The serial digital signal inputs are passive loop-throughs, so they m ust be

terminated to operate properly. Each input is applied to a cable equalizer and then

to a serial-to-parallel conversion circuit. The output of these sections are parallel

data and a word clock.

Composite

Input

The Composite inputs a re also passive loop-throughs. If unterminated, the

signal appears twice as large as it should. The two sets of inputs go through a

2-to-1 m

ultiplexer; then the selected signal is clamped if selected by the user.

After the clamp, the signal is filtered and then applied to an A-to-D converter

to generate a 12-bit parallel signal. There is also a sync separator to generate

timing information and a picture decoder. The output of the picture decoder is

very similar to the parallel data from the serial digital input. The separated sync

passes on to the waveform processing (WFM) FPGAs, where it processed in

the di

gital domain.

Reference Input

The R

eference input is a passive loopthrough similar to that o f the Composite

inputs. The buffered signal is clamped and then digitized to generate a 10-bit

stream. A simple sync separator ge nerates timing information, which is sent to

the wa ve form processing FPGAs. As on the composite inputs, the separated

sync from the reference p asses on to the WFM FPGAs, where it is processed

in the digital domain.

Digital Waveform Processing Engine

The parallel data streams from a ll three video inputs are applied to the waveform

p

rocessing FPGA . This block up-samples, interpolates, demodulates and

otherwise processes the data to generate the signals needs to c reate the displays.

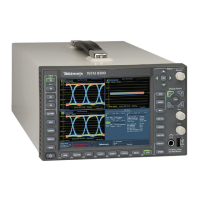

2–2 WVR6020, WVR7020, and WVR7120 Waveform Rasterizers Service Manual

Loading...

Loading...