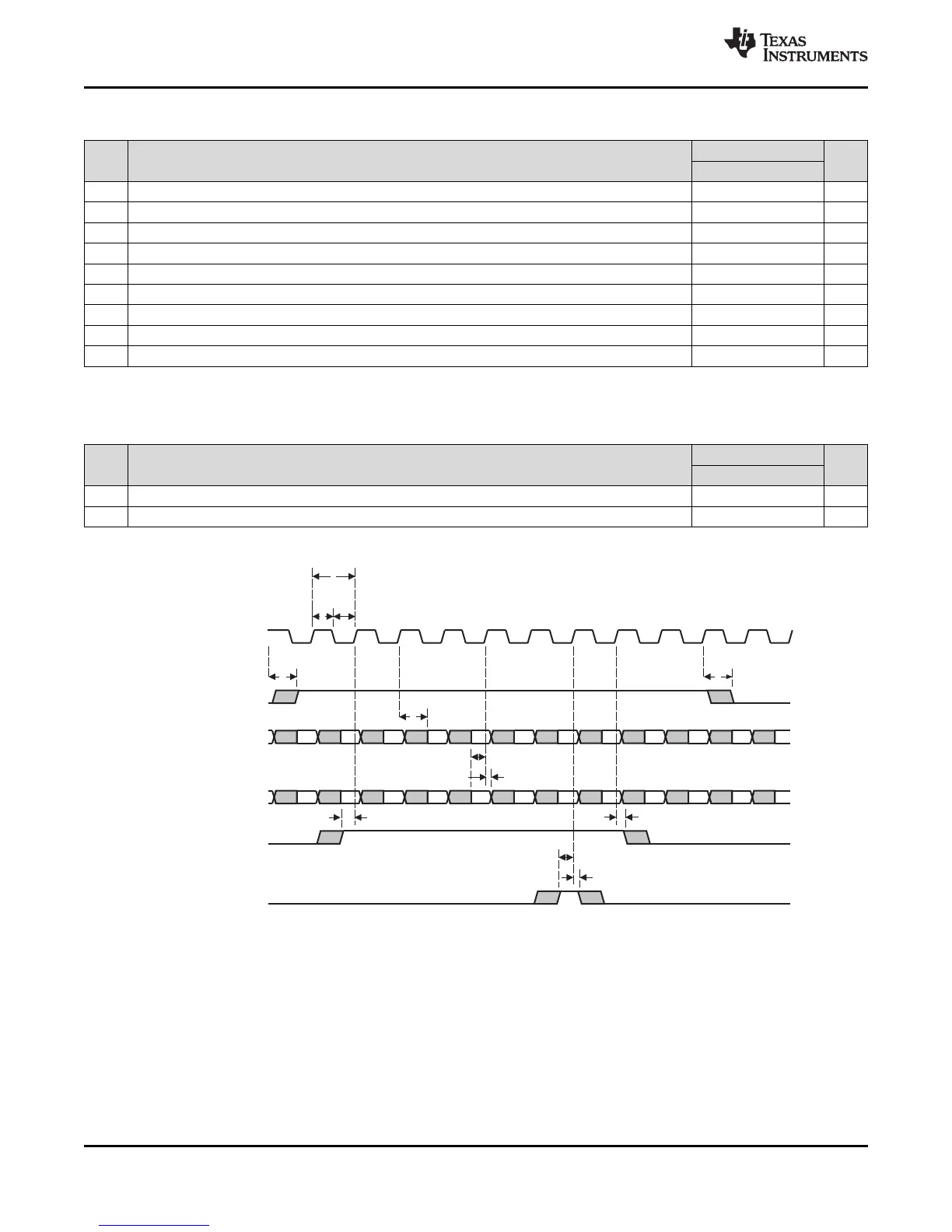

RMII_MHz_50_CLK

RMII_TXEN

RMII_TXD[1:0]

RMII_RXD[1:0]

RMII_CRS_DV

RMII_RXER

1

2 3

5 5

4

6

7

8 9

10

11

AM1808

SPRS653E –FEBRUARY 2010–REVISED MARCH 2014

www.ti.com

Table 6-102. Timing Requirements for EMAC RMII

1.3V, 1.2V, 1.1V

(1)

NO. UNIT

MIN TYP MAX

1 tc(REFCLK) Cycle Time, RMII_MHZ_50_CLK

(2)

20 ns

2 tw(REFCLKH) Pulse Width, RMII_MHZ_50_CLK High 7 13 ns

3 tw(REFCLKL) Pulse Width, RMII_MHZ_50_CLK Low 7 13 ns

6 tsu(RXD-REFCLK) Input Setup Time, RXD Valid before RMII_MHZ_50_CLK High 4 ns

7 th(REFCLK-RXD) Input Hold Time, RXD Valid after RMII_MHZ_50_CLK High 2 ns

8 tsu(CRSDV-REFCLK) Input Setup Time, CRSDV Valid before RMII_MHZ_50_CLK High 4 ns

9 th(REFCLK-CRSDV) Input Hold Time, CRSDV Valid after RMII_MHZ_50_CLK High 2 ns

10 tsu(RXER-REFCLK) Input Setup Time, RXER Valid before RMII_MHZ_50_CLK High 4 ns

11 th(REFCLKR-RXER) Input Hold Time, RXER Valid after RMII_MHZ_50_CLK High 2 ns

(1) RMII is not supported at operating points below 1.1V nominal.

(2) Per the RMII industry specification, the RMII reference clock (RMII_MHZ_50_CLK) must have jitter tolerance of 50 ppm or less.

Table 6-103. Switching Characteristics Over Recommended Operating Conditions for EMAC RMII

1.3V, 1.2V, 1.1V

(1)

NO. PARAMETER UNIT

MIN TYP MAX

4 td(REFCLK-TXD) Output Delay Time, RMII_MHZ_50_CLK High to TXD Valid 2.5 13 ns

5 td(REFCLK-TXEN) Output Delay Time, RMII_MHZ_50_CLK High to TXEN Valid 2.5 13 ns

(1) RMII is not supported at operating points below 1.1V nominal.

Figure 6-49. RMII Timing Diagram

192 Peripheral Information and Electrical Specifications Copyright © 2010–2014, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM1808

Loading...

Loading...