AM1808

www.ti.com

SPRS653E –FEBRUARY 2010–REVISED MARCH 2014

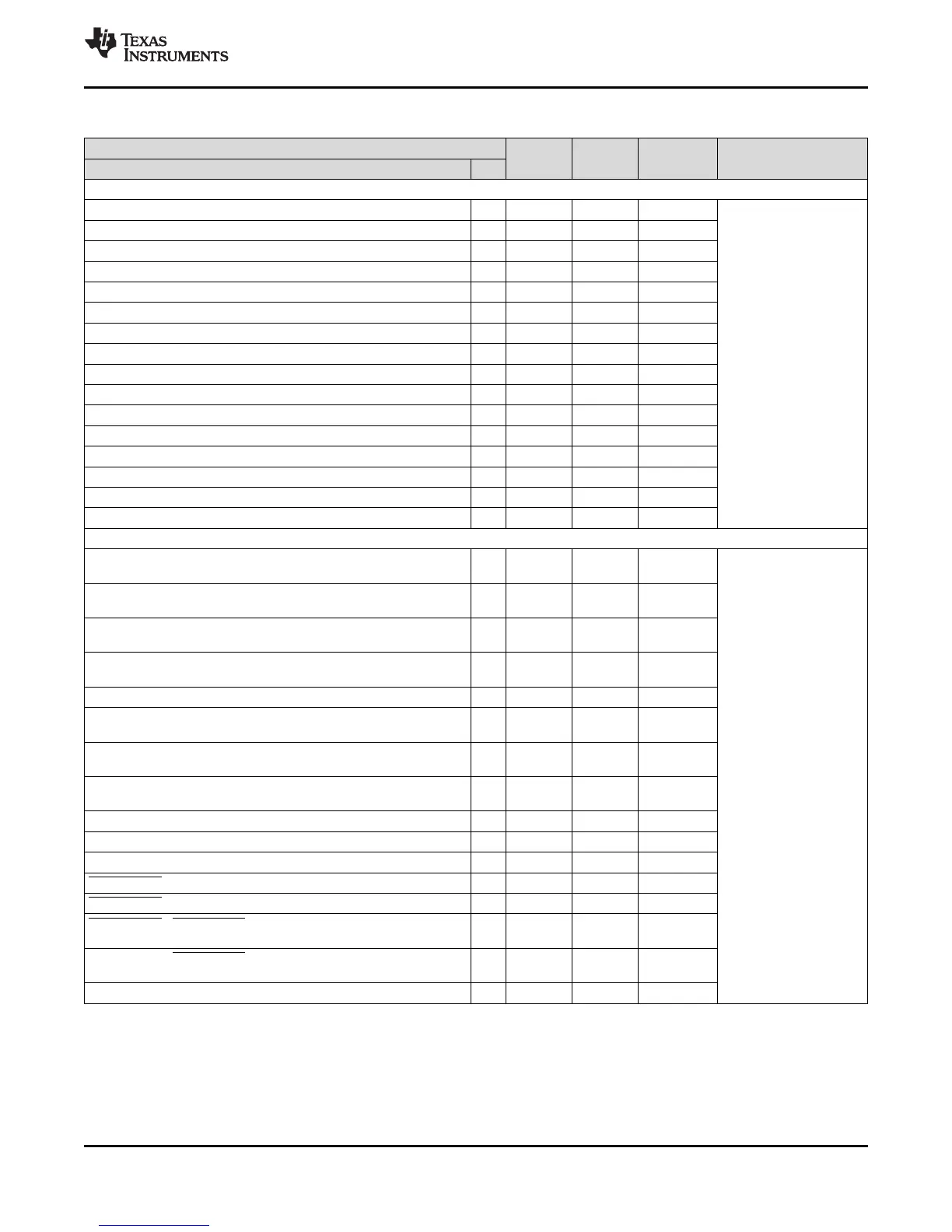

Table 3-27. General Purpose Input Output Terminal Functions (continued)

SIGNAL

POWER

TYPE

(1)

PULL

(2)

DESCRIPTION

GROUP

(3)

NAME NO.

GP7

VP_DOUT[7] / LCD_D[7] / UPP_XD[15] / GP7[15] / PRU1_R31[15] U2 I/O CP[28] C

VP_DOUT[6] / LCD_D[6] / UPP_XD[14] / GP7[14] / PRU1_R31[14] U1 I/O CP[28] C

VP_DOUT[5] / LCD_D[5] / UPP_XD[13] / GP7[13] / PRU1_R31[13] V3 I/O CP[28] C

VP_DOUT[4] / LCD_D[4] / UPP_XD[12] / GP7[12] / PRU1_R31[12] V2 I/O CP[28] C

VP_DOUT[3] / LCD_D[3] / UPP_XD[11] / GP7[11] / PRU1_R31[11] V1 I/O CP[28] C

VP_DOUT[2] / LCD_D[2] / UPP_XD[10] / GP7[10] / PRU1_R31[10] W3 I/O CP[28] C

VP_DOUT[1] / LCD_D[1] / UPP_XD[9] / GP7[9] / PRU1_R31[9] W2 I/O CP[28] C

VP_DOUT[0] / LCD_D[0] / UPP_XD[8] / GP7[8] /PRU1_R31[8] W1 I/O CP[28] C

GPIO Bank 7

VP_DOUT[15/] LCD_D[15] / UPP_XD[7] / GP7[7] / BOOT[7] P4 I/O CP[29] C

VP_DOUT[14] / LCD_D[14] / UPP_XD[6] / GP7[6] / BOOT[6] R3 I/O CP[29] C

VP_DOUT[13] / LCD_D[13] / UPP_XD[5] / GP7[5] / BOOT[5] R2 I/O CP[29] C

VP_DOUT[12] / LCD_D[12] / UPP_XD[4] / GP7[4] / BOOT[4] R1 I/O CP[29] C

VP_DOUT[11] / LCD_D[11] / UPP_XD[3] / GP7[3] / BOOT[3] T3 I/O CP[29] C

VP_DOUT[10] / LCD_D[10] / UPP_XD[2] / GP7[2] / BOOT[2] T2 I/O CP[29] C

VP_DOUT[9] / LCD_D[9] / UPP_XD[1] / GP7[1] / BOOT[1] T1 I/O CP[29] C

VP_DOUT[8] / LCD_D[8] / UPP_XD[0] / GP7[0] / BOOT[0] U3 I/O CP[29] C

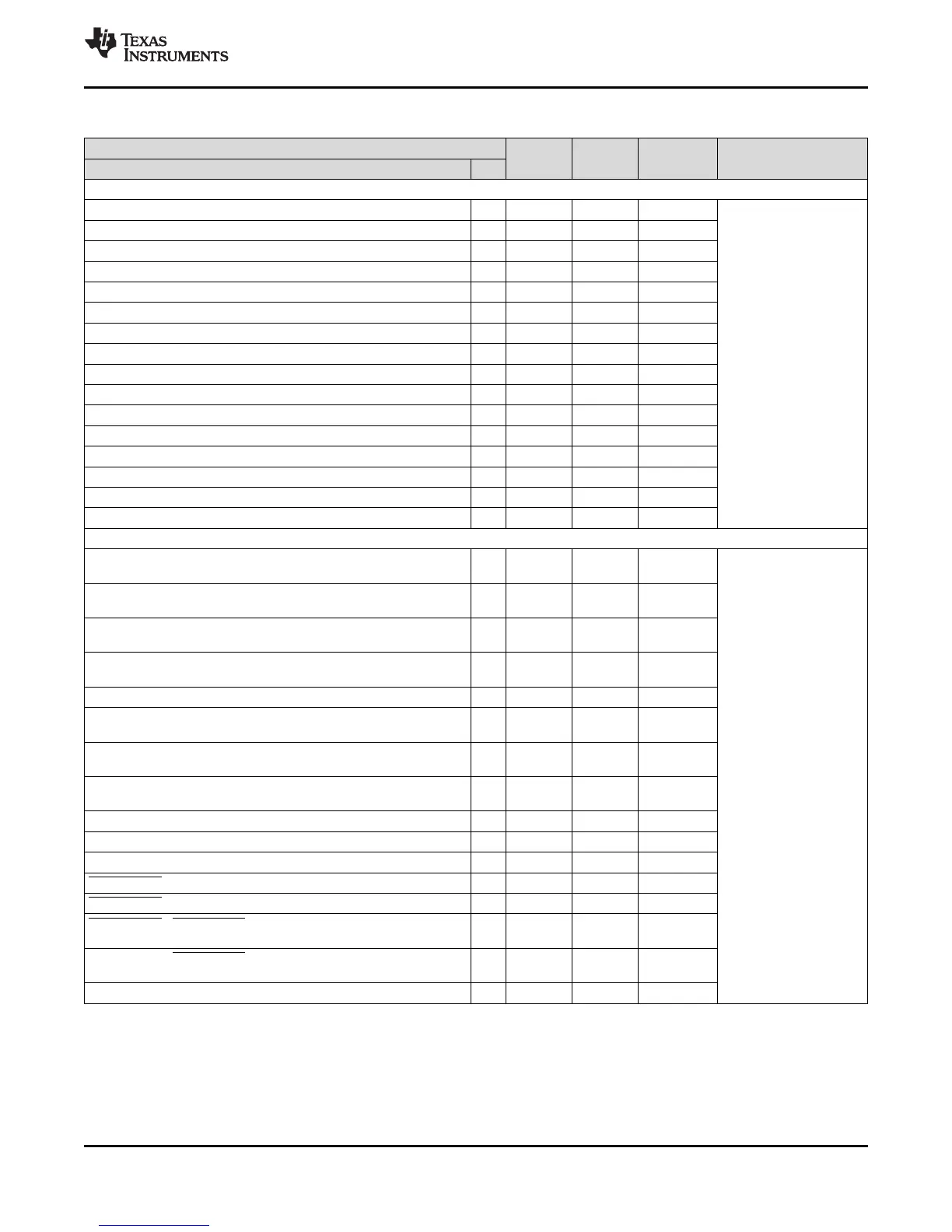

GP8

PRU0_R30[25] / MMCSD1_DAT[0] / UPP_CHB_CLOCK / GP8[15]

G1 I/O CP30] C

/ PRU1_R31[27]

PRU0_R30[24] / MMCSD1_CLK / UPP_CHB_START / GP8[14] /

G2 I/O CP[30] C

PRU1_R31[26]

PRU0_R30[23] / MMCSD1_CMD / UPP_CHB_ENABLE / GP8[13] /

J4 I/O CP[30] C

PRU1_R31[25]

PRU0_R30[22] / PRU1_R30[8] / UPP_CHB_WAIT / GP8[12] /

G3 I/O CP[30] C

PRU1_R31[24]

MMCSD1_DAT[7] / LCD_PCLK / PRU1_R30[7] / GP8[11] F1 I/O CP[31] C

MMCSD1_DAT[6] / LCD_MCLK / PRU1_R30[6] / GP8[10] /

F2 I/O CP[31] C

PRU1_R31[7]

MMCSD1_DAT[5] / LCD_HSYNC / PRU1_R30[5] / GP8[9] /

H4 I/O CP[31] C

PRU1_R31[6]

GPIO Bank 8

MMCSD1_DAT[4] / LCD_VSYNC / PRU1_R30[4] / GP8[8] /

G4 I/O CP[31] C

PRU1_R31[5]

AXR0 / ECAP0_APWM0 / GP8[7] / MII_TXD[0] / CLKS0 F3 I/O CP[6] A

SPI0_SOMI /EPWMSYNCI / GP8[6] / MII_RXER C16 I/O CP[7] A

SPI0_SIMO / EPWMSYNCO / GP8[5] / MII_CRS C18 I/O CP[7] A

SPI0_SCS[5] / UART0_RXD / GP8[4] / MII_RXD[3] C19 I/O CP[8] A

SPI0_SCS[4] / UART0_TXD / GP8[3] / MII_RXD[2] D18 I/O CP[8] A

SPI0_SCS[3] / UART0_CTS / GP8[2] / MII_RXD[1] /

E17 I/O CP[9] A

SATA_MP_SWITCH

SPI0_SCS[2] / UART0_RTS / GP8[1] / MII_RXD[0] /

D16 I/O CP[9] A

SATA_CP_DET

RTCK/ GP8[0]

(1)

K17 I/O IPD B

(1) GP8[0] is initially configured as a reserved function after reset and will not be in a predictable state. This signal will only be stable after

the GPIO configuration for this pin has been completed. Users should carefully consider the system implications of this pin being in an

unknown state after reset.

Copyright © 2010–2014, Texas Instruments Incorporated Device Overview 55

Submit Documentation Feedback

Product Folder Links: AM1808

Loading...

Loading...