ECO NO:

DATE:

APPROVED:

REVISION RECORD

LTR

A

D

C

6

A

B

C

D

5

4

3

2

1

B

SCALE:

SHEET: OF

DRAWING NO:

TITLE:

COMPANY:

RELEASED:

DATED:

DATED:

QUALITY CONTROL:

CHECKED:

DATED:

DATED:

DRAWN:

CODE:

SIZE:

REV:

23

4

<Scale>

<Revision>

<Drawing Number>

A0

<Code>

<Title>

<Company Name>

<Release Date>

<QC Date>

<Checked Date>

<Drawn Date>

<Released By>

<QC By>

<Checked By>

<Drawn By>

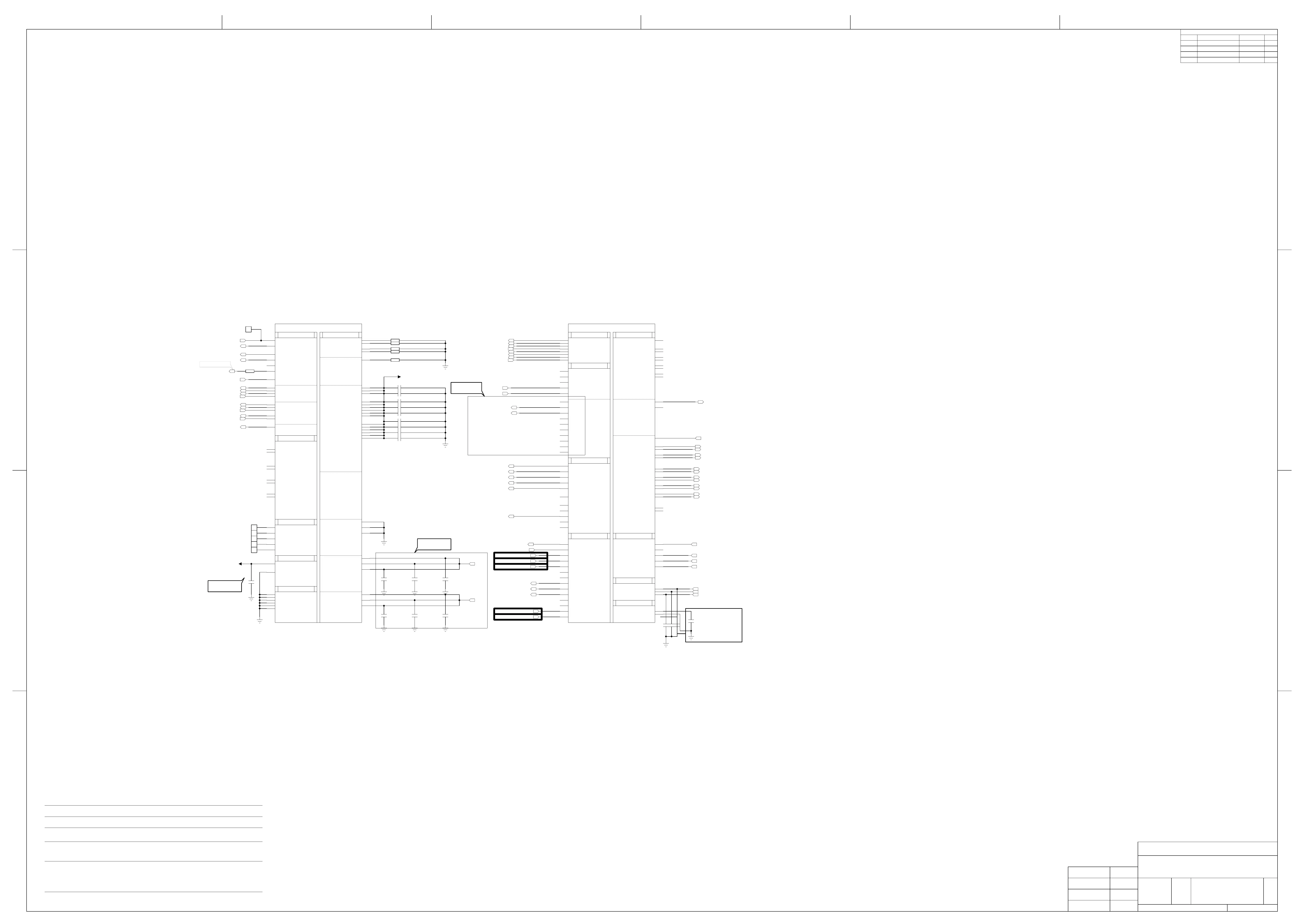

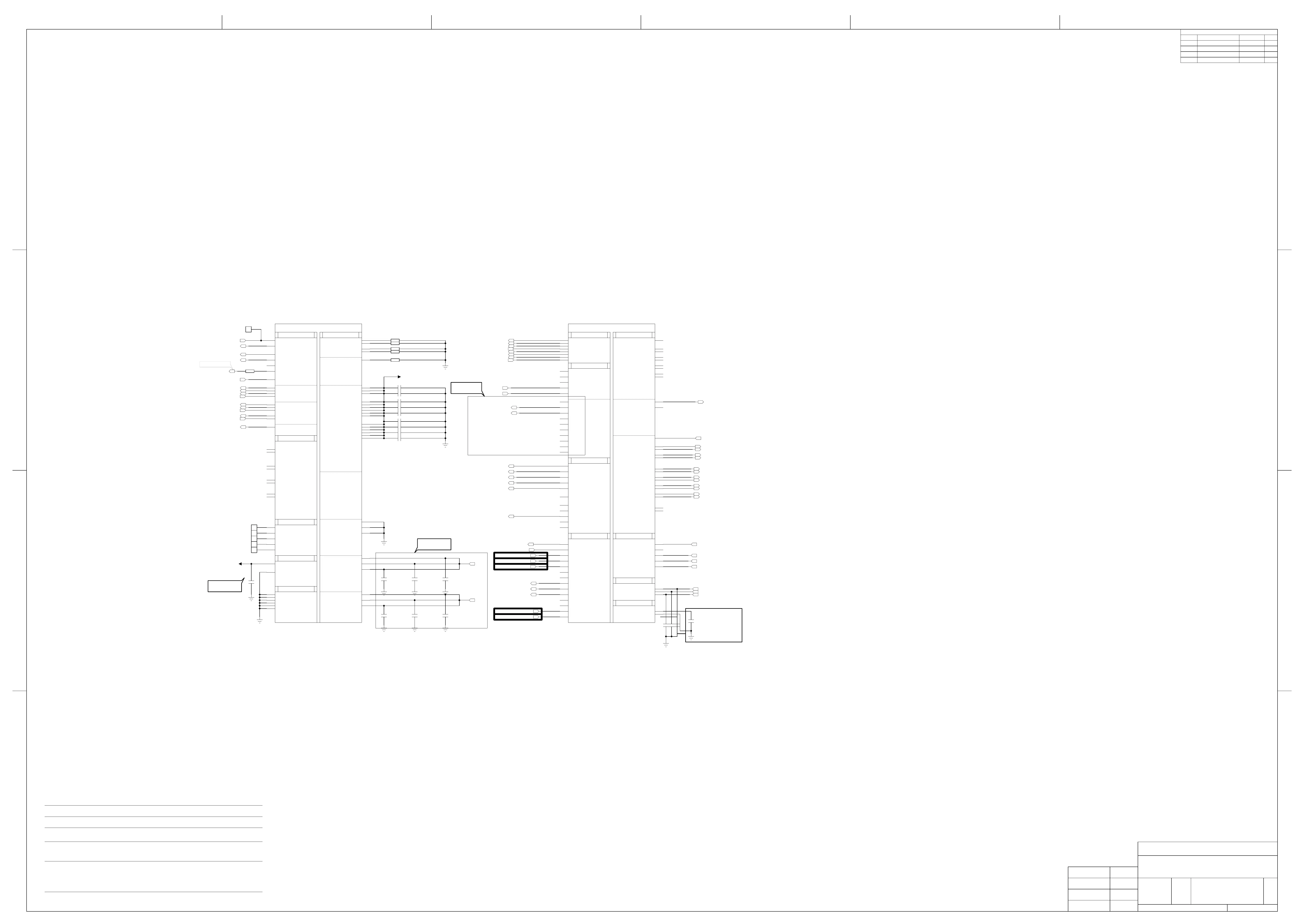

Note: 12-1

Close to BB IC.

Note: 12-2

Note 12-1:

Schematic design notice of "11_BB_11" page.

Note 12-2:

The BPI_BUS0~BPI_BUS9 are capable of 2.8V I/O operation.

Apply 1.8V to DVDD18_EFUSE (AK24) for eFuse programming.

Note 12-3:

The de-coupling cap. of DRAM VREF have to be placed as close to

BB as possible.

Note: 12-3

Note 12-4:

Note: 12-4

SRCLKENAI2 features watch dog reset output to reset 4-phase buck.

R1207 BOM option:

R1207 = 0R when BOM option of U2401 is DA9210.

R1207 = NC when BOM option of U2401 is 2nd source.

BPI - W/G

SIM

BPI - L

AUX IN

MT6795-MWFPOP-852P

ABB_IF

RFI_C

REF POWER

MISC BSI

AN7

SIM1_SCLK

AN8

SIM1_SIO

AP8

SIM1_SRST

AH4

INT_SIM1

AL6

SIM2_SCLK

AN6

SIM2_SIO

AL5

SIM2_SRST

AH3

INT_SIM2

H31

BPI_OUT14

G31

BPI_OUT13

H33

BPI_OUT12

G33

BPI_OUT11

G34

BPI_OUT10

F34

BPI_BUS9

F33

BPI_BUS8

E33

BPI_BUS7

D33

BPI_BUS6

F31

BPI_BUS5

E31

BPI_BUS4

D31

BPI_BUS3

C32

BPI_BUS2

C31

BPI_BUS1

B31

BPI_BUS0

M33

RFIC0_BSI_EN

L32

RFIC0_BSI_CK

M32

RFIC0_BSI_D2

L33

RFIC0_BSI_D1

L31

RFIC0_BSI_D0

K33

TD_TXBPI

K32

RFIC1_BSI_EN

J33

RFIC1_BSI_CK

K31

RFIC1_BSI_D2

K30

RFIC1_BSI_D1

J30

RFIC1_BSI_D0

AL33

LTE_TXBPI

AL29

PAVM1

AL30

PAVM0

AP30

BPI_OUT25

AN30

BPI_OUT24

AP31

BPI_OUT23

AN31

BPI_OUT22

AM31

BPI_OUT21

AN32

BPI_OUT20

AM32

BPI_OUT19

AN33

BPI_OUT18

AL32

BPI_OUT17

AL31

BPI_OUT16

AK31

BPI_OUT15

W28

TDX26M_IN

V34

TD_TX_BBIP

W33

TD_TX_BBIN

V33

TD_TX_BBQP

U33

TD_TX_BBQN

R30

TD_RX_BBIP

P30

TD_RX_BBIN

M30

TD_RX_BBQP

N30

TD_RX_BBQN

Y31

APC

Y32

APC2

AA28

LTEX26M_IN

AE30

LTE_TX_BBIP

AD30

LTE_TX_BBIN

AB30

LTE_TX_BBQP

AC30

LTE_TX_BBQN

AD34

LTE_RX1_BBIP

AD33

LTE_RX1_BBIN

AE32

LTE_RX1_BBQP

AD32

LTE_RX1_BBQN

AB32

LTE_RX2_BBIP

AC32

LTE_RX2_BBIN

AC33

LTE_RX2_BBQP

AC34

LTE_RX2_BBQN

AG31

ET_P

AG32

ET_N

AH31

MISC_BSI_CS0B

AJ31

MISC_BSI_CS1B

AJ33

MISC_BSI_CK

AH32

MISC_BSI_DO

AK33

MISC_BSI_DI

V31

AUXIN2

T31

AUXIN1

U31

AUXIN0

T34

REFP

T33

REFN

U1001-B

MT6795W/M

Misc

PLLs Test Pin

DRAM_IF

PMU_IF

NC

JTAG

MT6795-MWFPOP-852P

H2

SYSRSTB

G4

WATCHDOG

H5

SRCLKENA0

J2

SRCLKENA1

J5

SRCLKENAI

H4

SRCLKENAI2

K5

RTC32K_CK

L3

PWRAP_SPI0_CSN

M5

PWRAP_SPI0_CK

N5

PWRAP_SPI0_MO

M6

PWRAP_SPI0_MI

M3

AUD_CLK_MOSI

L2

AUD_DAT_MOSI

M2

AUD_DAT_MISO

K4

ANC_DAT_OUT

L4

ANC_DAT_IN

K2

DISP_PWM0

AP33

TP_MEMPLLPOP

AN34

TN_MEMPLLPOP

B34

TP_MEMPLL_A

A33

TN_MEMPLL_A

AP2

TP_MEMPLL_B

AN1

TN_MEMPLL_B

AM11

JTRST_B

AN12

JTCK

AL11

JTDO

AL12

JTDI

AK13

JTMS

AK24

DVDD18_EFUSE

R5

TESTMODE

A1

NC

A2

NC

A34

NC

B1

NC

AP1

NC

AP34

NC

AN14

ZQ0_A

AN13

ZQ1_A

AG33

ZQ0_B

AH33

ZQ1_B

J29

EXTDN_A

AH27

DDRVPOP

AH28

DDRVPOP

AH29

DDRVPOP

H24

DDRV_A

H26

DDRV_A

H28

DDRV_A

J24

DDRV_A

J26

DDRV_A

J28

DDRV_A

AF9

DDRV_B

AG9

DDRV_B

AH9

DDRV_B

AJ9

DDRV_B

AJ10

DDRV_B

AJ11

DDRV_B

H30

VREF_A

AN18

VREF(CA)_A

A22

VREF(DQ)_A

AK9

VREF_B

AA34

VREF(CA)_B

W1

VREF(DQ)_B

V15

TP_ARMPLL

V16

TN_ARMPLL

AH26

VBIASNPOP

K25

VBIASN1_A

AG12

VBIASN1_B

U1001-A

MT6795W/M

C1211

1.0uF

0201

R1201

240R 1%

0201

R1202

240R 1%

0201

R1203

240R 1%

0201

R1204

240R 1%

0201

R1205

240R 1%

C1207

100nF

C1208

100nF

C1209

100nF

C1202

100nF

C1204

100nF

C1205

100nF

C1210

100nF

C1212

100nF

C1213

100nF

C1214

100nF

C1215

100nF

C1216

100nF

C1217

1.0uF

0201

R1207

0R

0201

C1218

100pF

0201

C1219

100pF

0201

C1230

100pF

TP1305

TP1306

TP1307

TP1308

TP1309

TP18

C1201

10uF

C1206

10uF

C1203

10uF

GND

GND

GND

GND

GND

GND

GND

VGP4_PMU

GND

GND

GND

GND

VDRAM_PMU

GND

RF_RX1_BBIP

[10]

RF_RX1_BBIN

[10]

RF_RX1_BBQP

[10]

RF_RX1_BBQN

[10]

RF_RX2_BBIP

[10]

RF_RX2_BBIN

[10]

RF_RX2_BBQP

[10]

RF_RX2_BBQN

[10]

AUX_IN0_NTC

[21]

MIPI0_SCLK

[11]

MIPI1_SCLK

[12]

MIPI1_SDATA

[12]

MIPI0_SDATA

[11]

APC1

[12]

AUD_DAT_MISO_2

[6]

ADC2_BOARD_ID1

[21]

MIPI1_SCLK

MIPI1_SDATA

MIPI0_SDATA

MIPI0_SCLK

AUX_IN1_NTC

[11]

GPIO10_MCAM_PD

GPIO91_BOARD_ID0

[21]

GND

SYSRSTB

[6]

WATCHDOG

[6,7,9]

ENBB_6169

[6,7,9,10]

EXT_4P_PMU_EN

[9]

RTC32K1V8

[6,7]

PWRAP_SPI0_CSN

[6,7]

PWRAP_SPI0_CK

[6,7]

PWRAP_SPI0_MO

[6,7]

PWRAP_SPI0_MI

[6,7]

AUD_CLK_MOSI

[6]

AUD_DAT_MOSI_1

[6]

AUD_DAT_MISO_1

[6]

AUD_DAT_MOSI_2

[6]

DISP_PWM0

[19]

SIM1_SCLK_6795

[23]

SIM1_SRST_6795

[23]

SIM1_SIO_6795

[23]

SIM2_SCLK_6795

[23]

SIM2_SIO_6795

[23]

SIM2_SRST_6795

[23]

BPI_BUS8

[12]

BPI_BUS7

[13]

LTE_RFIC0_BSI_EN

[10]

LTE_RFIC0_BSI_CK

[10]

LTE_RFIC0_BSI_D2

[10]

LTE_RFIC0_BSI_D1

[10]

LTE_RFIC0_BSI_D0

[10]

LTE_TXBPI

[10]

LTE_RF_BPI_BUS20

[13]

LTE_RF_BPI_OUT21

[13]

LTE_RF_BPI_BUS19

[13]

LTE_LTEX26M_IN

[10]

RF_TX_BBIP

[10]

RF_TX_BBIN

[10]

RF_TX_BBQP

[10]

RF_TX_BBQN

[10]

LCM_ID0

[19]

LCM_ID1

[19]

DDR_VREF

[4,7]

DDR_VREF

[4,7]

SRCLKENA1

[6,7]

INT_SIM1

[23]

INT_SIM2

[23]

GPIO80_FLASH_TX

[20]

GPIO90_EN

[15]

GPIO79_SCAM_RST

[20]

TUNE_SW1

TUNE_SW2

Loading...

Loading...