A

B

D

H

F

C

E

L

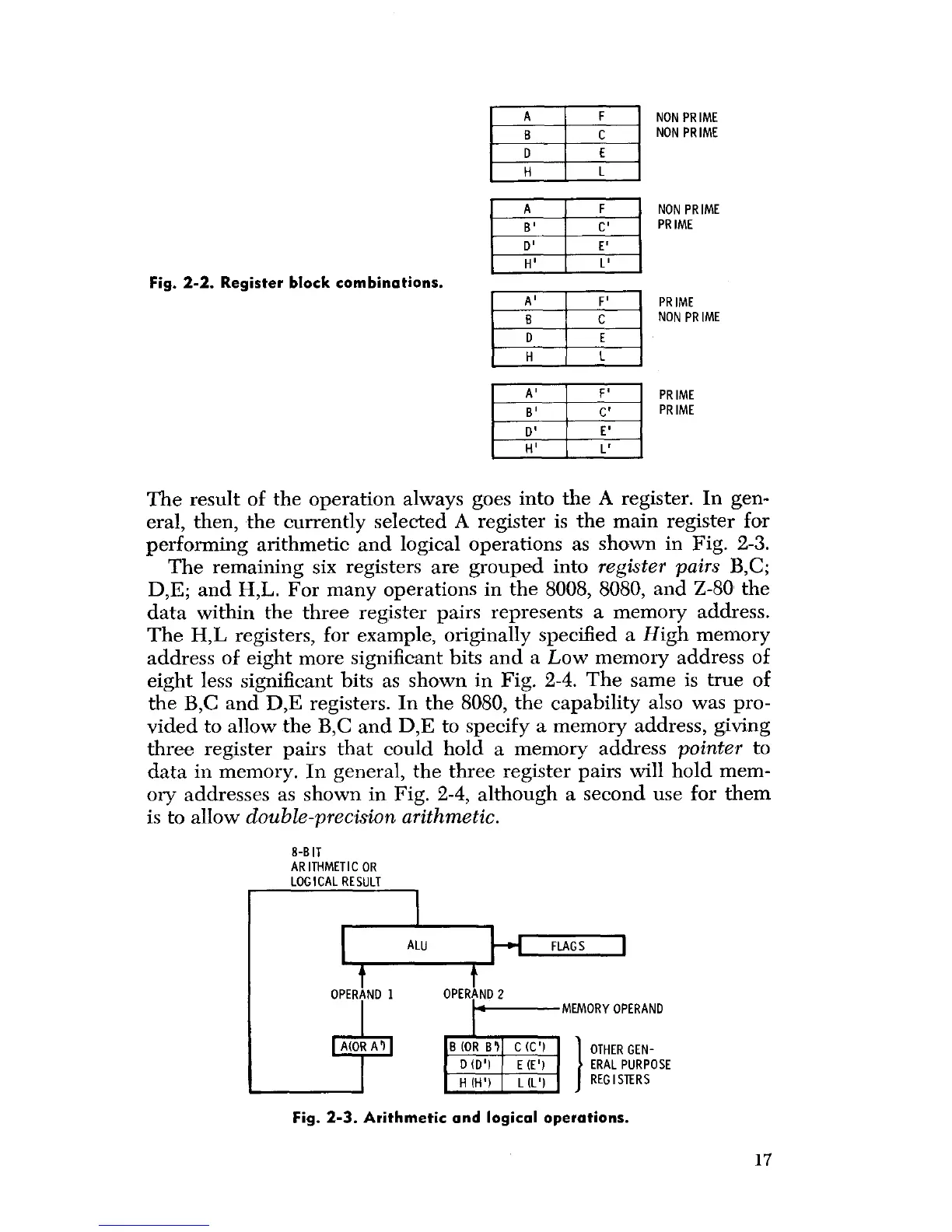

Fig. 2

-

2. Register block combinations.

A

B

D

H

F

C.

E'

L'

A

B

D

H

F'

C

E

L

W

H

NON PRIME

NON PRIME

NON PRIME

PRIME

PRIME

NON PRIME

PRIME

PRIME

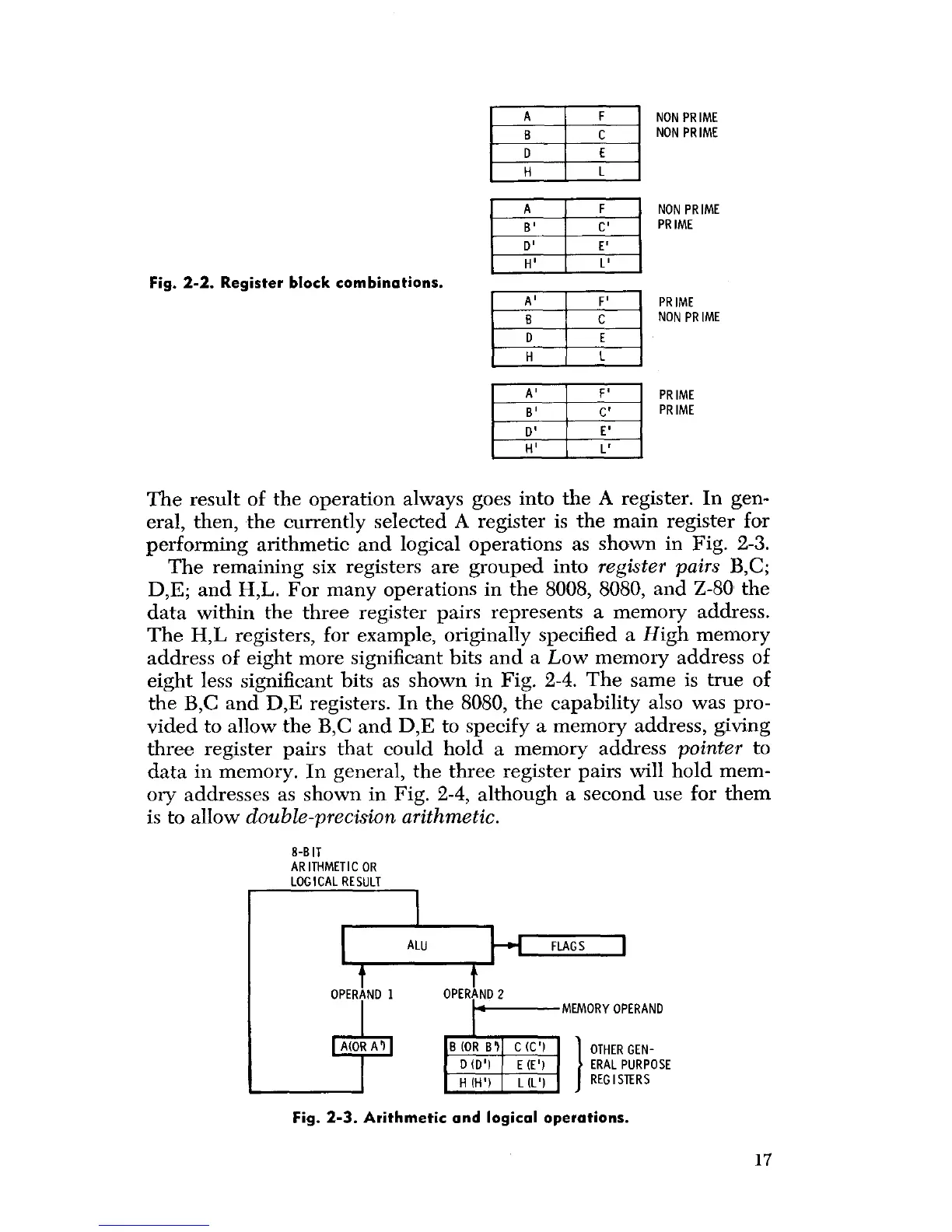

The result of the operation always goes into the A register. In gen-

eral, then, the currently selected A register is the main register for

performing arithmetic and logical operations as shown in Fig. 2-3.

The remaining six registers are grouped into

register pairs

B,C;

D,E; and H,L. For many operations in the 8008, 8080, and Z-80 the

data within the three register pairs represents a memory address.

The H,L registers, for example, originally specified a High memory

address of eight more significant bits and a Low memory address of

eight less significant bits as shown in Fig. 2-4. The same is true of

the B,C and D,E registers. In the 8080, the capability also was pro-

vided to allow the B,C and D,E to specify a memory address, giving

three register pairs that could hold a memory address

pointer

to

data in memory. In general, the three register pairs will hold mem-

ory addresses as shown in Fig. 2-4, although a second use for them

is to allow

double-precision arithmetic.

8-BIT

AR ITHMETIC OR

LOGICAL RESULT

AL

U

A

FL

GS

OPERA

ND 1

OPER

AND 2

MEMORY OPERAND

AIOR A9

B (OR 8

1

C (C')

1

OTHER GEN-

L

L (n

E (E'1

ERAL PURPOSE

H (H ')

_A

L (L')

J

REGISTERS

Fig. 2-3. Arithmetic

and logical operations.

17

Loading...

Loading...