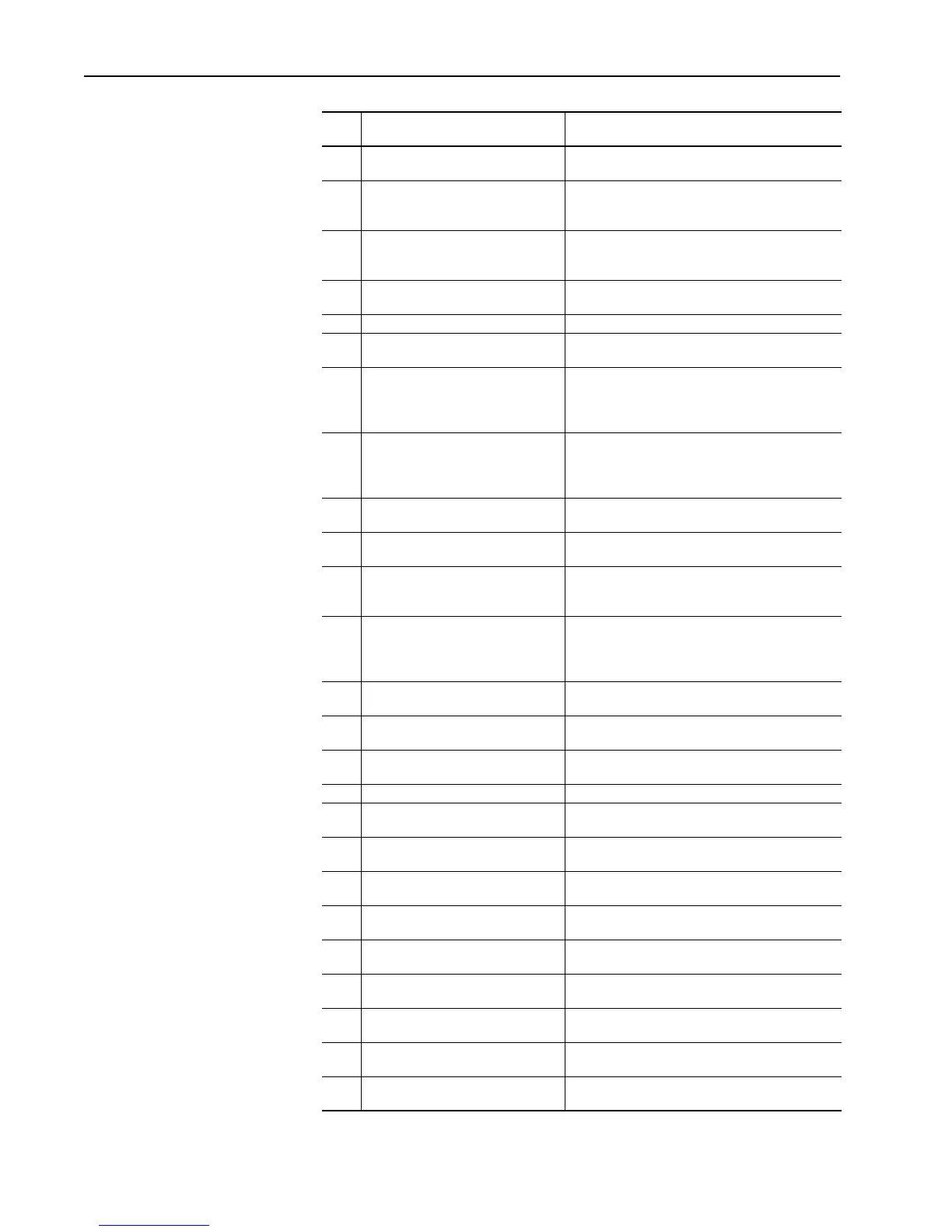

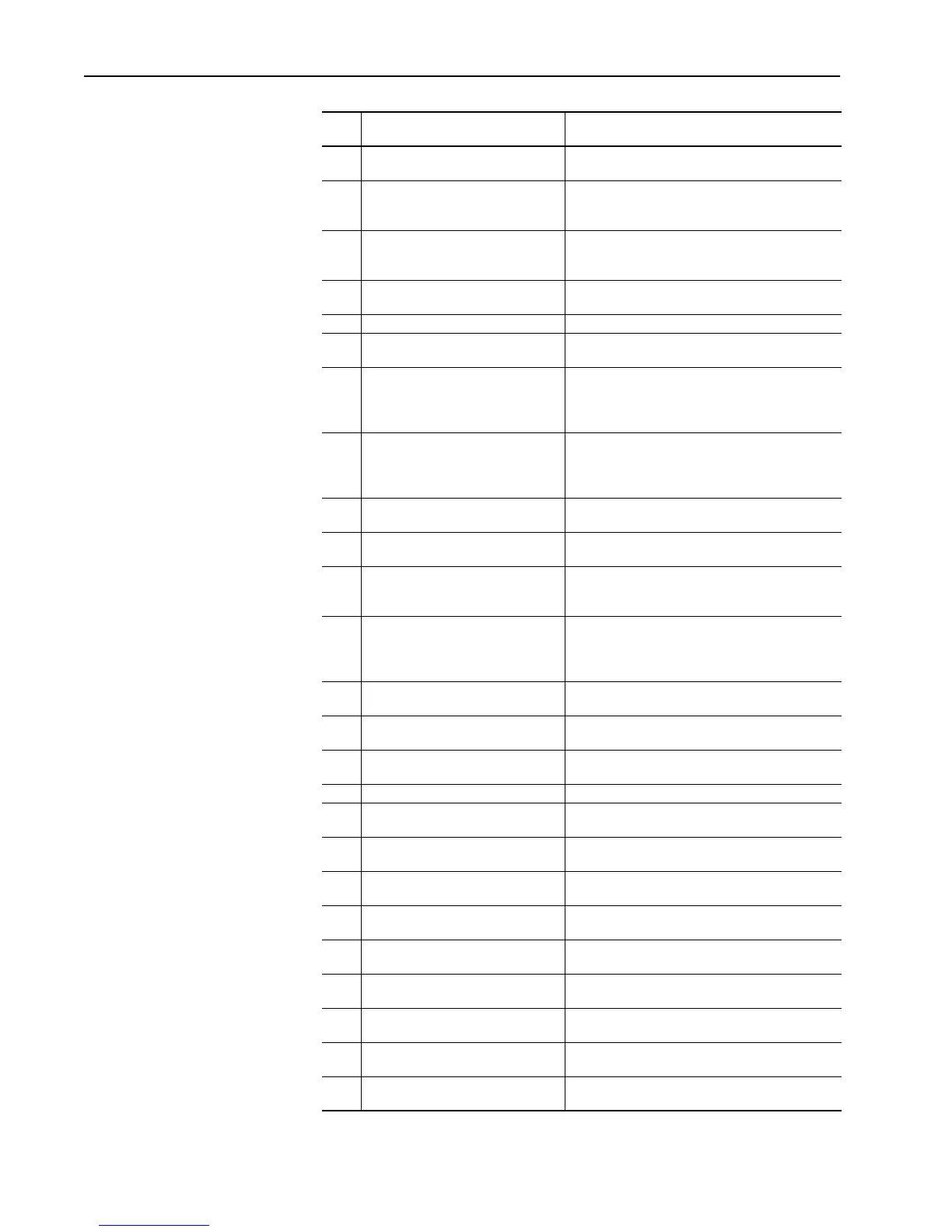

6-2 Test Points

15 0 to +5V DC square wave ENCA signal indicating the frequency of the A

channel encoder feedback.

17 +5VDC when phase loss exists. 0V DC

when no phase loss exists.

PHASELOSS signal used as input to the phase loss

latch circuit, the output of which is sent to the drive

logic.

19 0V DC when measured with respect to

TE ground.

Analog ground test point. All analog signals on the

Main Control Board must be measured with respect

to analog ground.

20 +1.5V DC to +3.0V DC for nominal

value.

POWERSUPPLY signal used to monitor the status of

the DC supply voltages.

21 DC volts between 0 and +10V DC. DC voltage representing armature voltage feedback.

23 0 to +5V, 6 pulse Pulses representing 4x encoder frequency in reverse,

otherwise 0.

24 Full wave rectified DC volts between 0

and –3V DC single wave.

IFFB signal from Power Stage Interface represents

field current feedback as sensed by FCT. –3V DC

equals the maximum value of the range specified by

the J1 jumper position.

25 DC voltage between 0 and +5V DC. DC voltage representing field current feedback

derived from the IFFB signal. DC voltage scaling is

set so 3.0V DC represents maximum value of the

range specified by the J1 jumper position.

26 DC voltage between 0 and +5V DC. DC voltage representing armature voltage feedback.

2.5V DC equals 0V DC armature voltage feedback.

27 DC voltage between 0 and +5V DC. DC voltage representing armature voltage feedback.

TP 26 filtered.

28 0 V DC when no AC overcurrent exists.

+5 V DC when an AC overcurrent

exists, unlatched.

OCAC signal used as a logic input to the overcurrent

latch circuit and to the drive logic.

29 0V DC when overcurrent latch circuit is

not latched. +5V DC when overcurrent

latch circuit is latched

AC and DC overcurrent signals used as input to the

drive logic. Once an overcurrent condition has

occurred, the output of the latch circuit is held high

until a drive reset has occurred.

30 0 to +5V square wave with varying

period

SYNCHAB (NOT) signal used as input to the

synchronizing circuit to determine phase rotation.

31 +5V DC when contactor is open. SYSTRIP signal used to open Main Contactor when

overcurrent has been sensed.

33 0 to +5V square wave with varying

period.

Signal used to reset the charge balance current

feedback circuit used for armature current feedback.

34 0 when resetting, +5V DC for charging. Armature current integrator reset signal.

35 0 to 5V DC Pulse 4 times encoder frequency (signal not direction

sensitive).

36 0 to 5V DC Pulse 4 time encoder frequency signal in forward direction,

0 in other cases.

37 +5V DC when overcurrent latch circuit

is not latched. 0V DC when latched.

Inverse of OVERCURRENT signal measured at

TP29. Used as input to the system inhibit circuit.

38 0 to +5V DC square-wave representing

the inverse of the line D to C waveform.

SYNCHBC (NOT) signal used as input to the

synchronizing logic to determine phase rotation.

39 0V DC when system operation is not

inhibited. +5V DC when inhibited.

SYSINHIBIT signal used in drive logic to open DC

contactor.

41 0 to +5V DC. Trip Point at 2.6V DC. 24V DC power supply sense. Drive faults at less than

2.6V DC.

43 0V DC when coast stop command is

not received. +5V DC when received.

ECOAST signal used in drive logic to control

operation after coast stop command.

51 +5, +0.02V DC when measured with

respect to TP52.

Digital circuit power supply voltage.

52 0V DC when measured with respect to

TE signal ground.

Digital Ground. All logic signals must be measured

with respect to TP52.

Test

Point Normal Value Description

Aotewell Ltd industry-mall.net

Loading...

Loading...