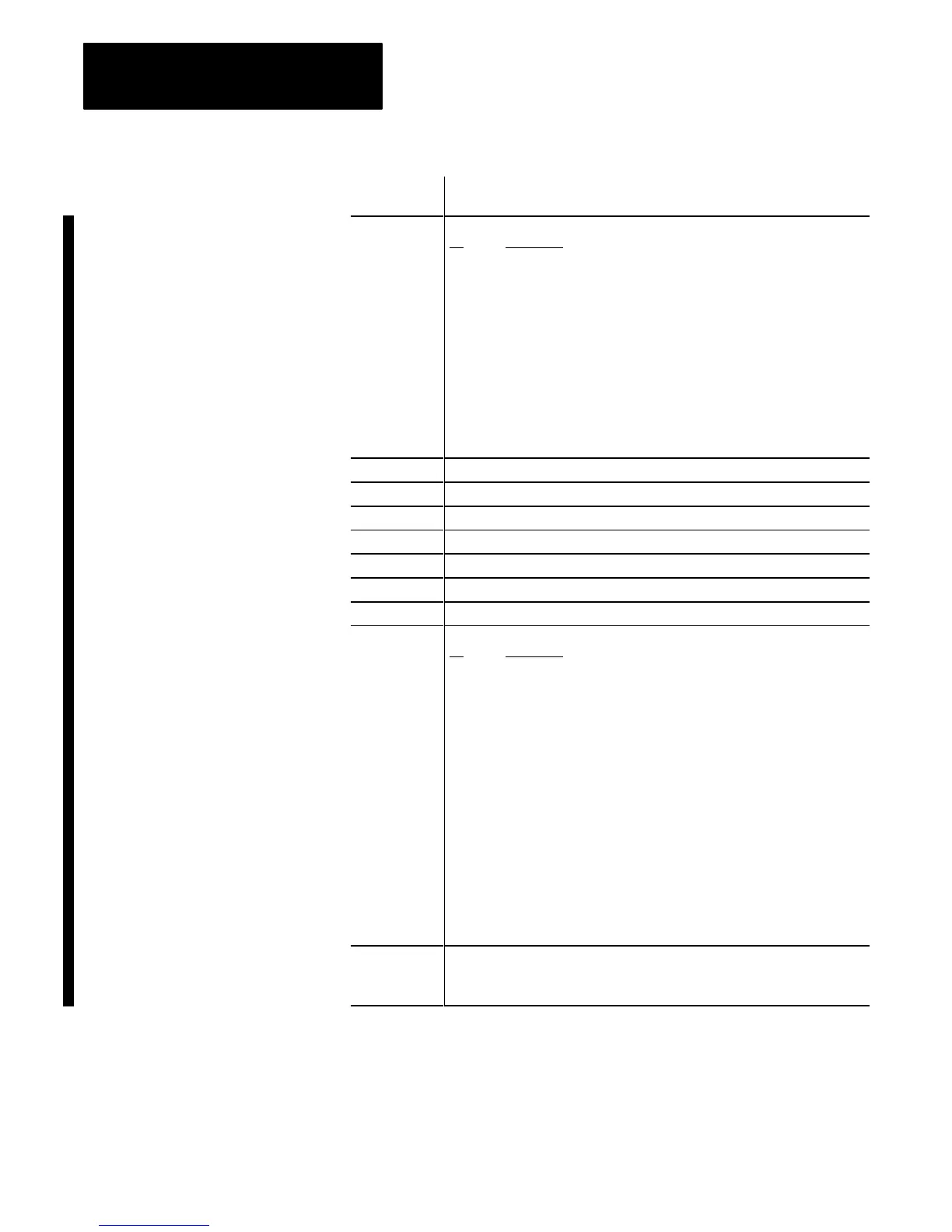

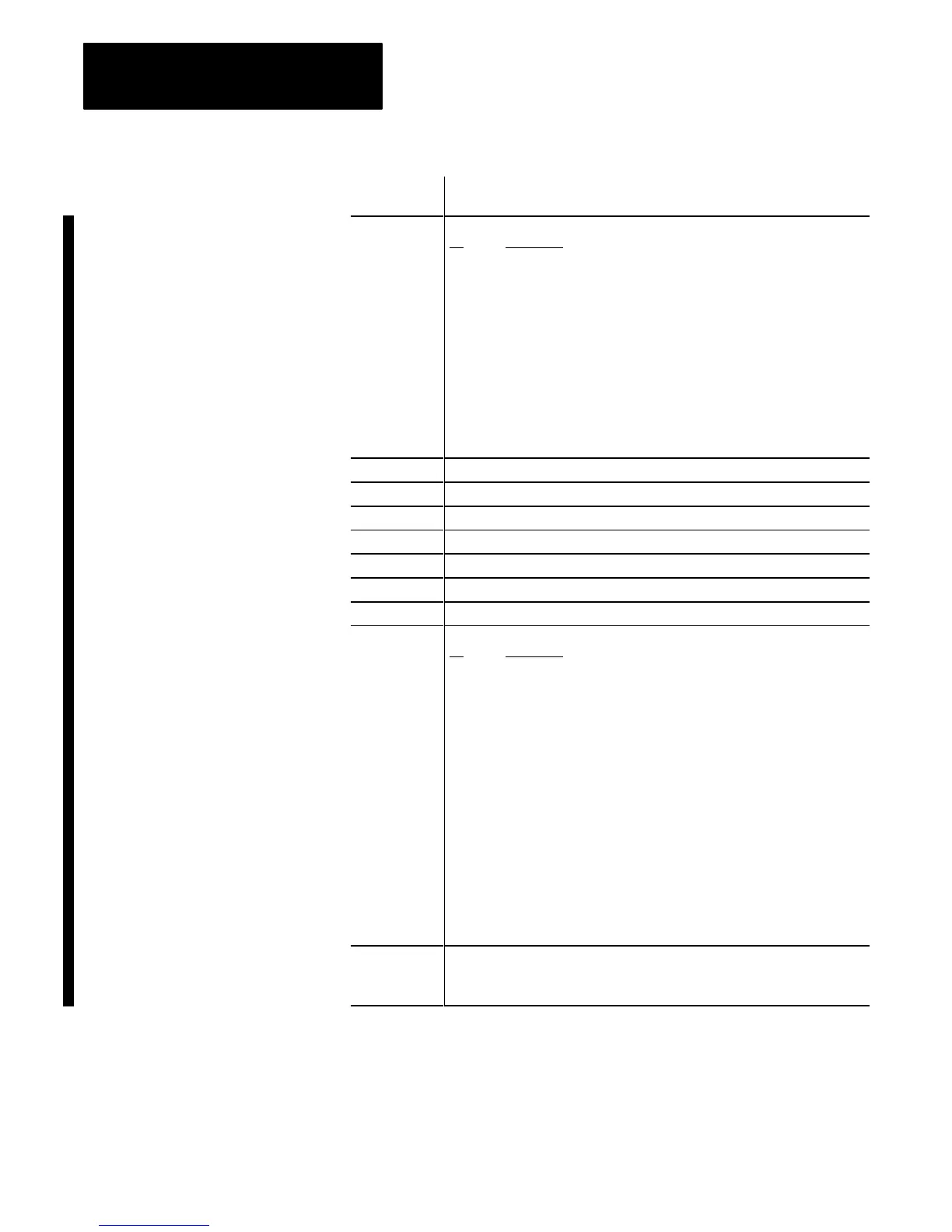

Addressing Reference

1785 PLC-5

10

This word of

the status file:

Stores:

S:17 Minor fault (word 2)

Bit Description

0 BT queue full to remote I/O

1 queue full – channel 1A

2 queue full – channel 1B

3 queue full – channel 2A

4 queue full – channel 2B

5 no modem on serial port

6 remote I/O rack in local rack table; or, remote I/O rack is greater than

the image size

8 ASCII instruction error

9 duplicate node address

10 DF1 master poll list error

11 protected processor data table element violation

12 protected processor file violation

S:18 Processor clock year

S:19 Processor clock month

S:20 Processor clock day

S:21 Processor clock hour

S:22 Processor clock minute

S:23 Processor clock second

S:24 Indexed addressing offset

S:26 User control bits

Bit Description

0 Restart/continuous SFC: when reset, processor restarts at first

step in SFC.

When set, processor continues with active step after power loss

or change to RUN.

1 Start-up protection after power loss; when reset, no protection.

When set, processor executes fault routine at power-up

(sets word 11, bit 5).

2 Define the address of the local rack: when reset, local rack

address is 0. When set, local rack address is 1.

3 Set complementary I/O: when reset, complementary I/O is not en-

abled.

When set, complementary I/O is enabled.

4 Local block transfer compatibility bit: when reset, normal operation.

When set, eliminates frequent checksum errors to certain BT mod-

ules.

5 When set (1), delay adapter channel response by 1s for compatibility

with PLC-3 scanners. When reset (0), operate in normal response

time.

S:27 Rack control bits:

• low 8 bits – I/O rack inhibit bits for racks 0-7

• high 8 bits – I/O rack reset bits for racks 0-7

Loading...

Loading...