DE1-SOC COMPUTER SYSTEM WITH NIOS II For Quartus II 15.0

3.1 Interrupts from Parallel Ports

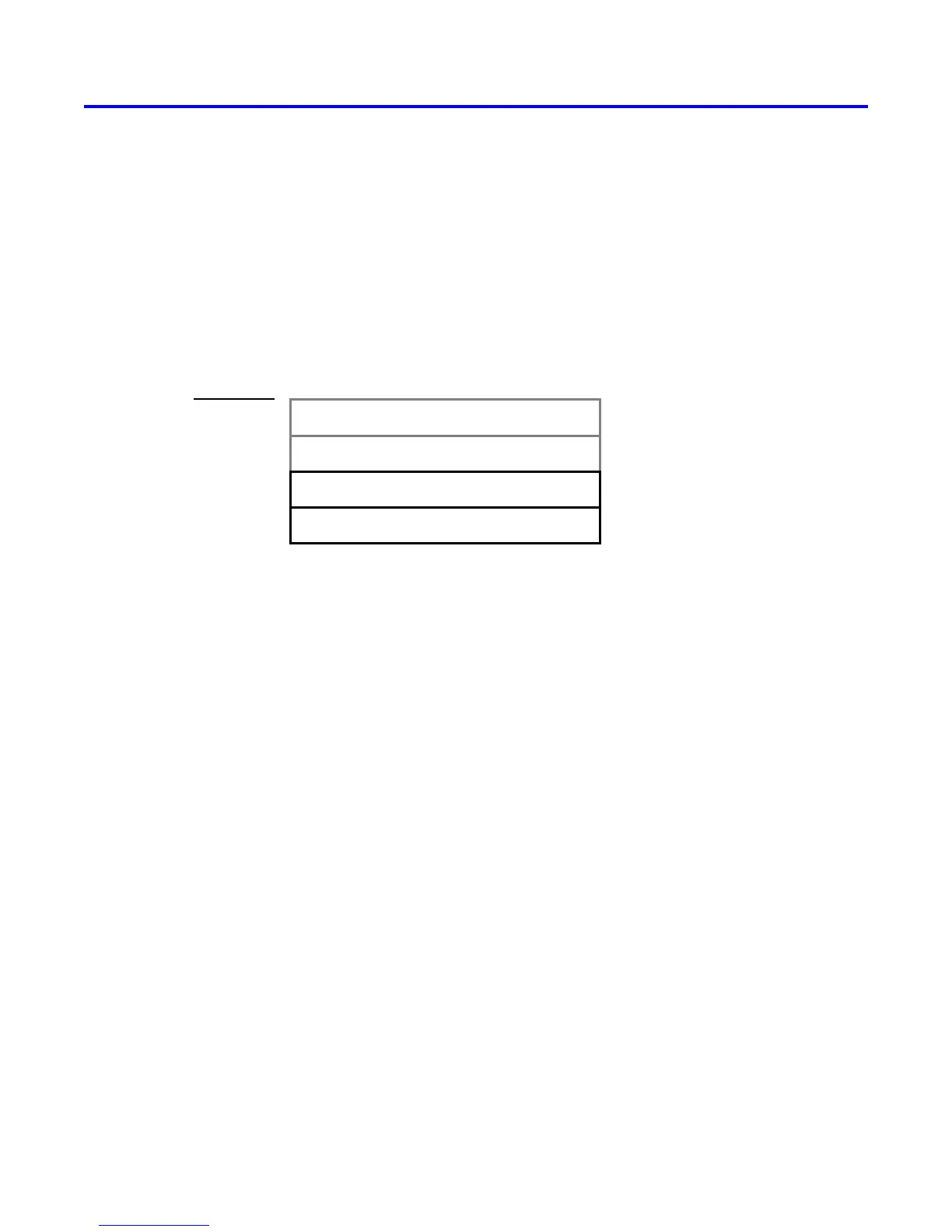

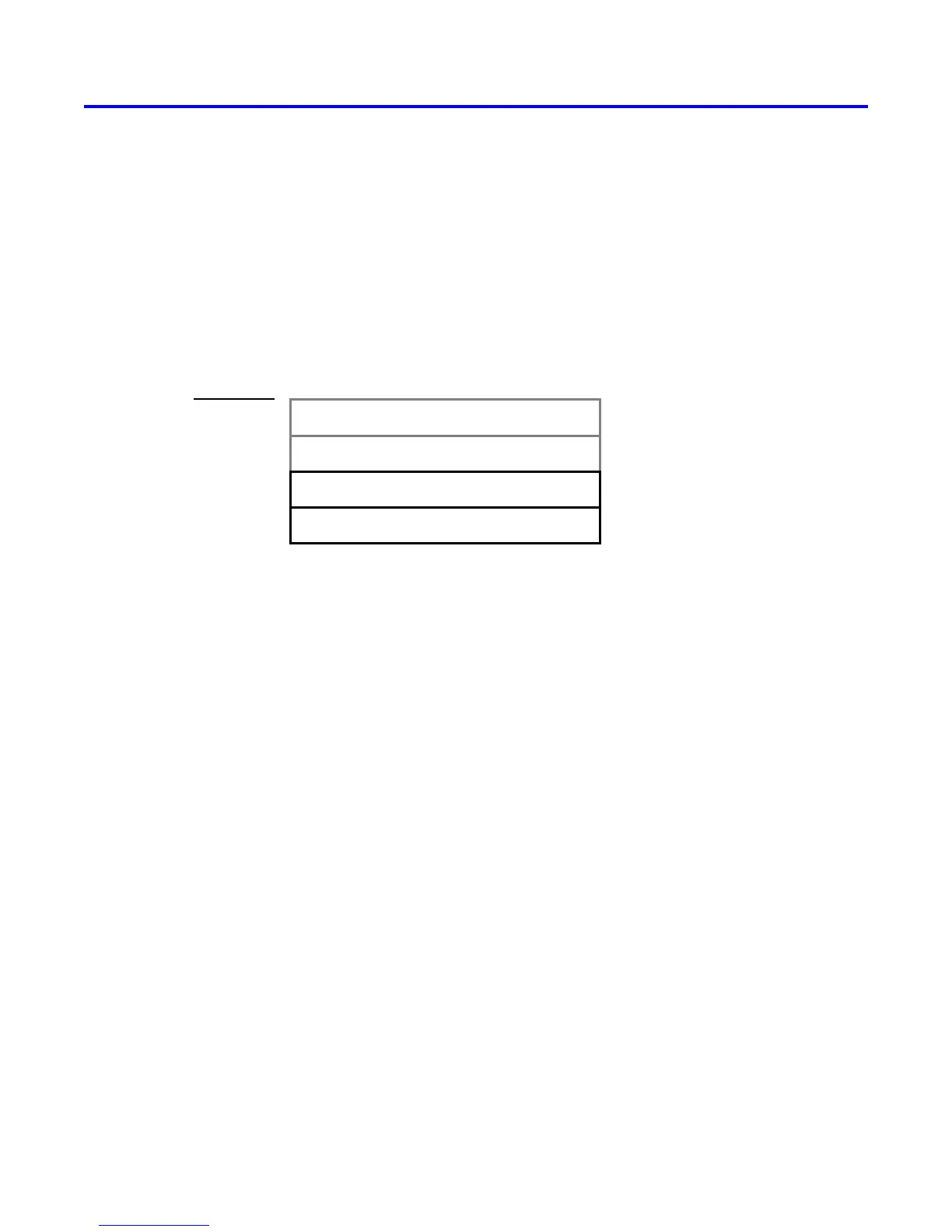

Parallel ports implemented in the FPGA in the DE1-SoC Computer were illustrated in Figure 2, which is reproduced

as Figure 15. As the figure shows, parallel ports that support interrupts include two related registers at the addresses

Base + 8 and Base + C. The Interruptmask register, which has the address Base + 8, specifies whether or not an

interrupt signal should be sent to the processor when the data present at an input port changes value. Setting a bit

location in this register to 1 allows interrupts to be generated, while setting the bit to 0 prevents interrupts. Finally,

the parallel port may contain an Edgecapture register at address Base + C. Each bit in this register has the value 1 if

the corresponding bit location in the parallel port has changed its value from 0 to 1 since it was last read. Performing

a write operation to the Edgecapture register sets all bits in the register to 0, and clears any associated interrupts.

Address

0214331 30

. . .

Base

Base + 8

Base + C

Base + 4

Input or output data bits

Direction bits

Data register

Direction register

Interruptmask register

Edgecapture register

Edge bits

Mask bits

Direction bits

Figure 15. Registers used for interrupts from the parallel ports.

3.1.1 Interrupts from the Pushbutton Switches

Figure 6 showed the registers associated with the pushbutton parallel port. The Interruptmask register allows inter-

rupts to be generated when a key is pressed. Each bit in the Edgecapture register is set to 1 by the parallel port when

the corresponding key is pressed. An interrupt service routine can read this register to determine which key has been

pressed. Writing any value to the Edgecapture register deasserts the interrupt signal being sent to the processor and

sets all bits of the Edgecapture register to zero.

3.2 Interrupts from the JTAG UART

Figure 10 showed the data and Control registers of the JTAG UART. As we said in Section 2.5, RAVAIL in the Data

register gives the number of characters that are stored in the receive FIFO, and WSPACE gives the amount of unused

space that is available in the transmit FIFO. The RE and WE bits in Figure 10 are used to enable processor interrupts

associated with the receive and transmit FIFOs. When enabled, interrupts are generated when RAVAIL for the receive

FIFO, or WSPACE for the transmit FIFO, exceeds 7. Pending interrupts are indicated in the Control register’s RI and

WI bits, and can be cleared by writing or reading data to/from the JTAG UART.

3.3 Interrupts from the FPGA Interval Timer

Figure 14, in Section 2.6, shows six registers that are associated with the interval timer. As we said in Section 2.6,

the TO bit in the Status register is set to 1 when the timer reaches a count value of 0. It is possible to generate an

interrupt when this occurs, by using the ITO bit in the Control register. Setting the ITO bit to 1 causes an interrupt

Altera Corporation - University Program

2015

15

Loading...

Loading...