1

19

2 20

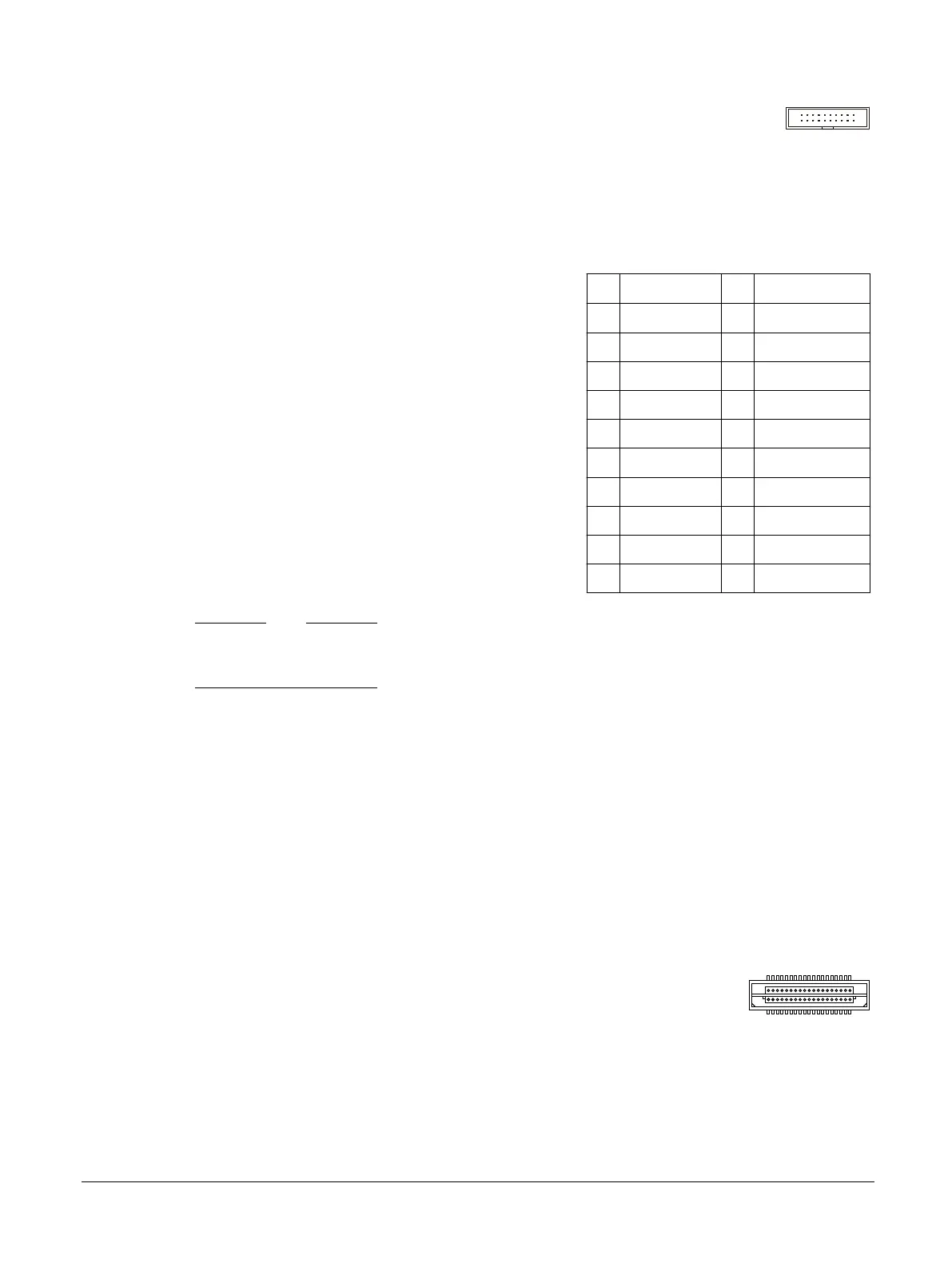

Figure A-3 20-pin Cortex debug and ETM connector

The following table shows the pin mapping for each P‑JTAG, SWD, and 4‑bit trace signal on the 20‑pin

Cortex debug and ETM connector.

Table A-3 20-pin Cortex debug and ETM connector, J12, pin mapping

Pin Signal Pin Signal

1 1V8 2 SWDIOTMS

3 GND 4 SWDCLKTCK

5 GND 6 SWOTDOEXTa

7 NC 8 NC/TDIEXTb

9 GNDDETECT 10 nSRST

11 3V0_OUT 12 TRACECLK

13 3V0_OUT 14 TRACEDATA[0]

15 GND 16 TRACEDATA[1]

17 GND 18 TRACEDATA[2]

19 GND 20 TRACEDATA[3]

Note

• Pins 2, 6, 8, 9, 10, 11, and 13 have pullup resistors to 1V8.

• Pin 4 has a pulldown resistor to GND.

Related information

2.18 System debug on page 2-50

1.3 Location of components on the MPS3 board on page 1-15

A.1.4 38-pin MICTOR connector

The MPS3 board provides one 1V8 38‑pin MICTOR connector. The connector supports P‑JTAG

processor debug to enable connection of DSTREAM, or a compatible third‑party debugger. The

connector also supports Serial Wire Debug (SWD) and 16‑bit trace.

The 38‑pin MICTOR connector connects to general‑purpose pins on the FPGA. The availability of

P‑JTAG, SWD, or 16‑bit trace depends on the design that you implement in the FPGA.

The following figure shows the 38‑pin MICTOR connector, J13.

2

38

1 37

Figure A-4 38-pin MICTOR connector

A Signal descriptions

A.1 Debug connectors

100765_0000_04_en Copyright © 2017–2020 Arm Limited or its affiliates. All rights

reserved.

Appx-A-73

Non-Confidential

Loading...

Loading...