EtherCAT communication EL6731-00x0

EL6731158 Version: 2.8

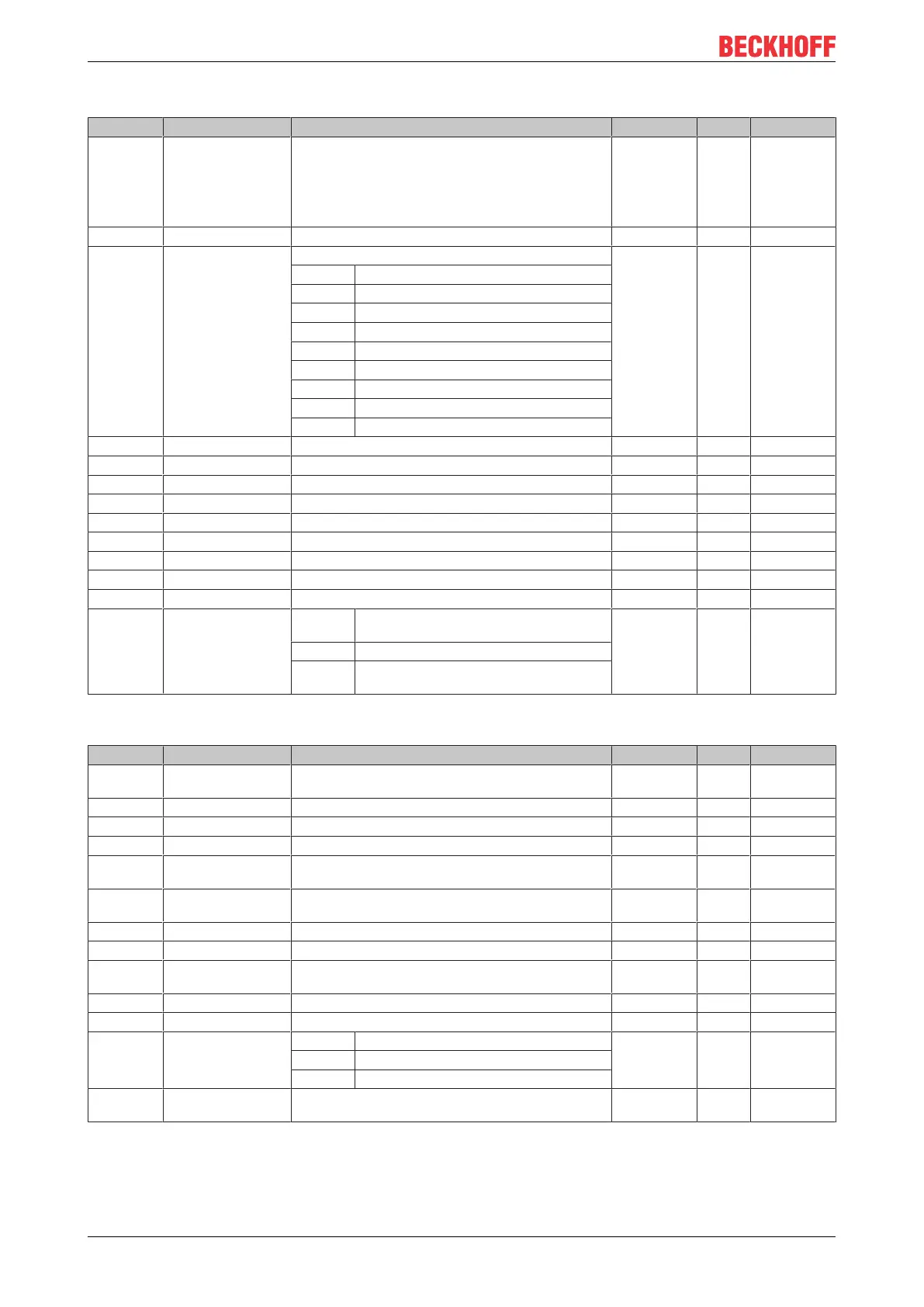

Index F800 DP Bus Parameter Set

Index (hex) Name Meaning Data type Flags Default

F800:0 DP Bus Parameter

Set

This object contains the DP bus parameters. The object

is to be transmitted with Complete Access, or SubIndex 0

must first be set to 0, then the individual SubIndexes

transmitted (non-existent SubIndexes or gaps are

thereby to be omitted) and finally SubIndex 0 set to the

correct value.

UINT8 RW 0x18 (24

dec

)

F800:01 DL_Add DP-Master station address UINT8 RW 0x00 (0

dec

)

F800:02 Data_rate Baud rate UINT8 RW 0x00 (0

dec

)

0 9.6 kbaud

1 19.2 kbaud

2 93.75 kbaud

3 187.5 kbaud

4 500 kbaud

6 1.5 Mbaud

7 3 Mbaud

8 6 Mbaud

9 12 Mbaud

F800:03 Tsl Slot time in bit times UINT16 RW *

F800:04 min Tsdr Min. TSDR in bit times UINT16 RW 0x0B (11

dec

)

F800:05 max Tsdr Max. TSDR in bit times UINT16 RW *

F800:06 Tqui Quiet Time in bit times UINT8 RW *

F800:07 Tset Setup Time in bit times UINT8 RW *

F800:08 Ttr Target Token Rotation Time in bit times UINT32 RW *

F800:09 G GAP Update Factor (1-100) UINT8 RW 0x64 (100

dec

)

F800:0A HSA Highest master address (0-126) UINT8 RW 0x7E (126

dec

)

F800:0B max_retry_limit Maximum number of repeats (1-8) UINT8 RW *

F800:0C Bp_Flag Bit 0 Single master operation (no GAP update is

sent)

UINT8 RW 0x00 (0

dec

)

Bits 1-6 Reserve, must be 0

Bit 8 Auto-Clear mode is on (DP master goes to

CLEAR if a DP slave is not exchanging data)

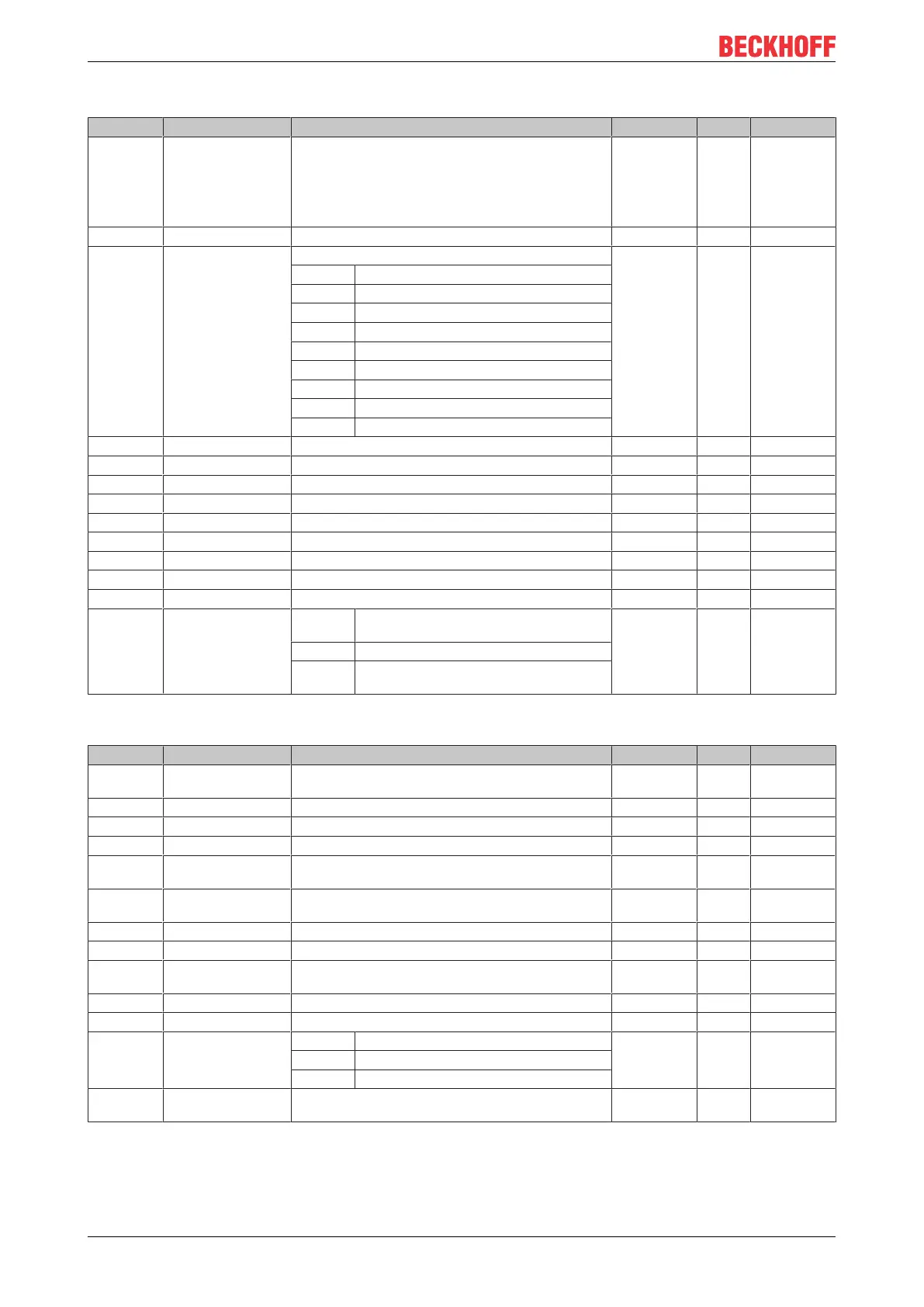

Index F800 DP bus parameter set

Index (hex) Name Meaning Data type Flags Default

F800:0D Min_Slave_Interval Cycle time for DP telegrams (except data exchange (runs

synchronously to the EtherCAT master))

UINT16 RW *

F800:0E Poll_Timeout Reserve, must be 0 UINT16 RW 0x0000 (0

dec

)

F800:0F Data_Control_Time Cycle time of the Global_Control telegram UINT16 RW *

F800:10 Alarm_Max Reserve, must be 0 UINT8 RW 0x00 (0

dec

)

F800:11 Max_User_Global_co

ntrol

Reserve, must be 0 UINT8 RW 0x00 (0

dec

)

F800:12 Max Retry Limit

(Data-Exchange)

Maximum number of data exchange repeats BIT4 RW *

F800:13 Send Set-Prm-Unlock Reserve, must be 0 BIT2 RW 0x00 (0

dec

)

F800:14 Auto Clear Mode Reserve, must be 0 BIT2 RW 0x00 (0

dec

)

F800:15 Operate Delay (in 100

ms)

Automatic switching to OPERATE in the OP state is de-

layed according to this setting

UINT8 RW 0x00 (0

dec

)

F800:16 Safety Time (in us) Reserve, must be 0 UINT16 RW 0x0000 (0

dec

)

F800:17 Flags Reserve, must be 0 UINT16 RW 0x0000 (0

dec

)

F800:18 Watchdog Reaction 0 DP Master in CLEAR Mode OCTET-

STRING[26]

RW {0}

1 DP Master in OPERATE Mode

2 DP Master in STOP Mode

F800:1A Vendor specific Reserve, must be 0 OCTET-

STRING[26]

RW

Loading...

Loading...