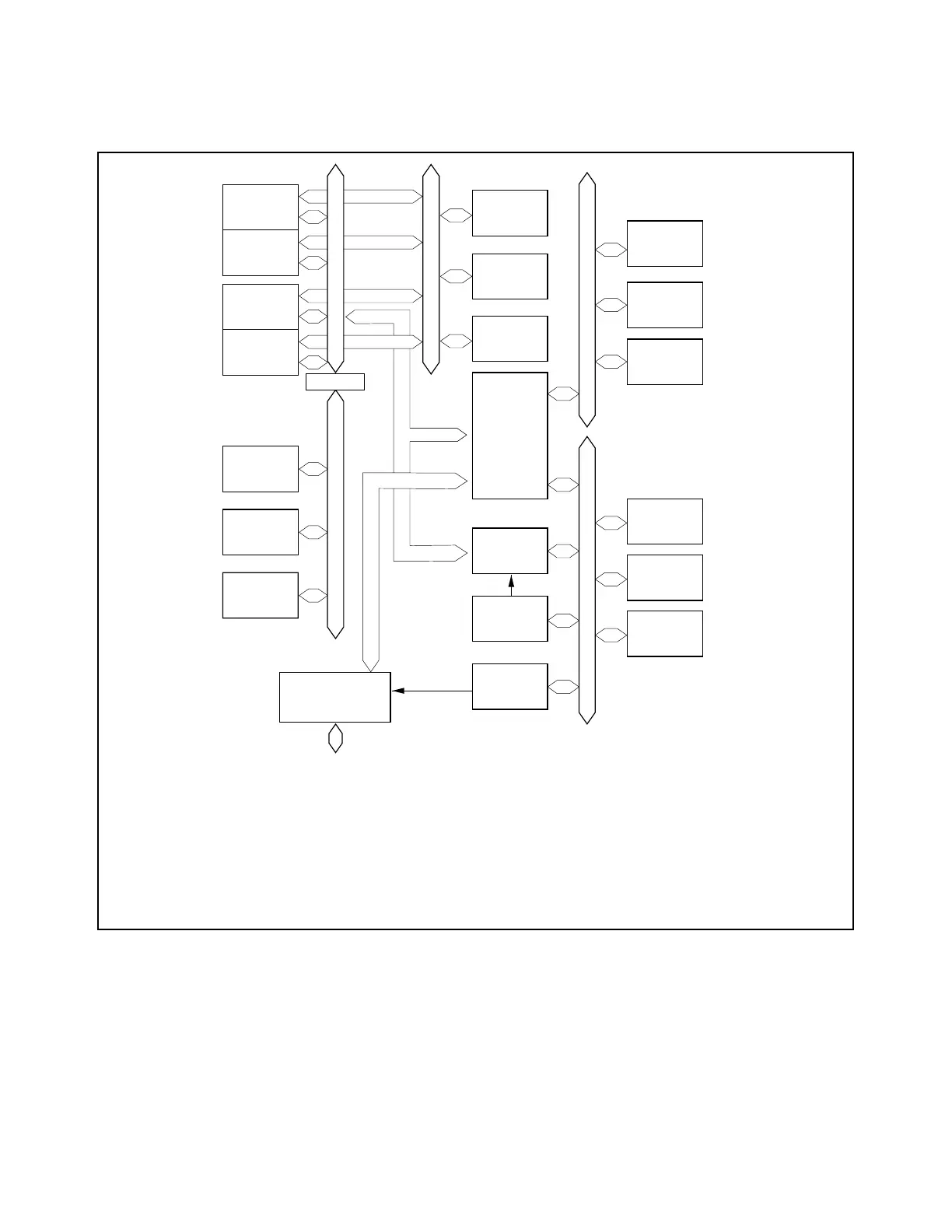

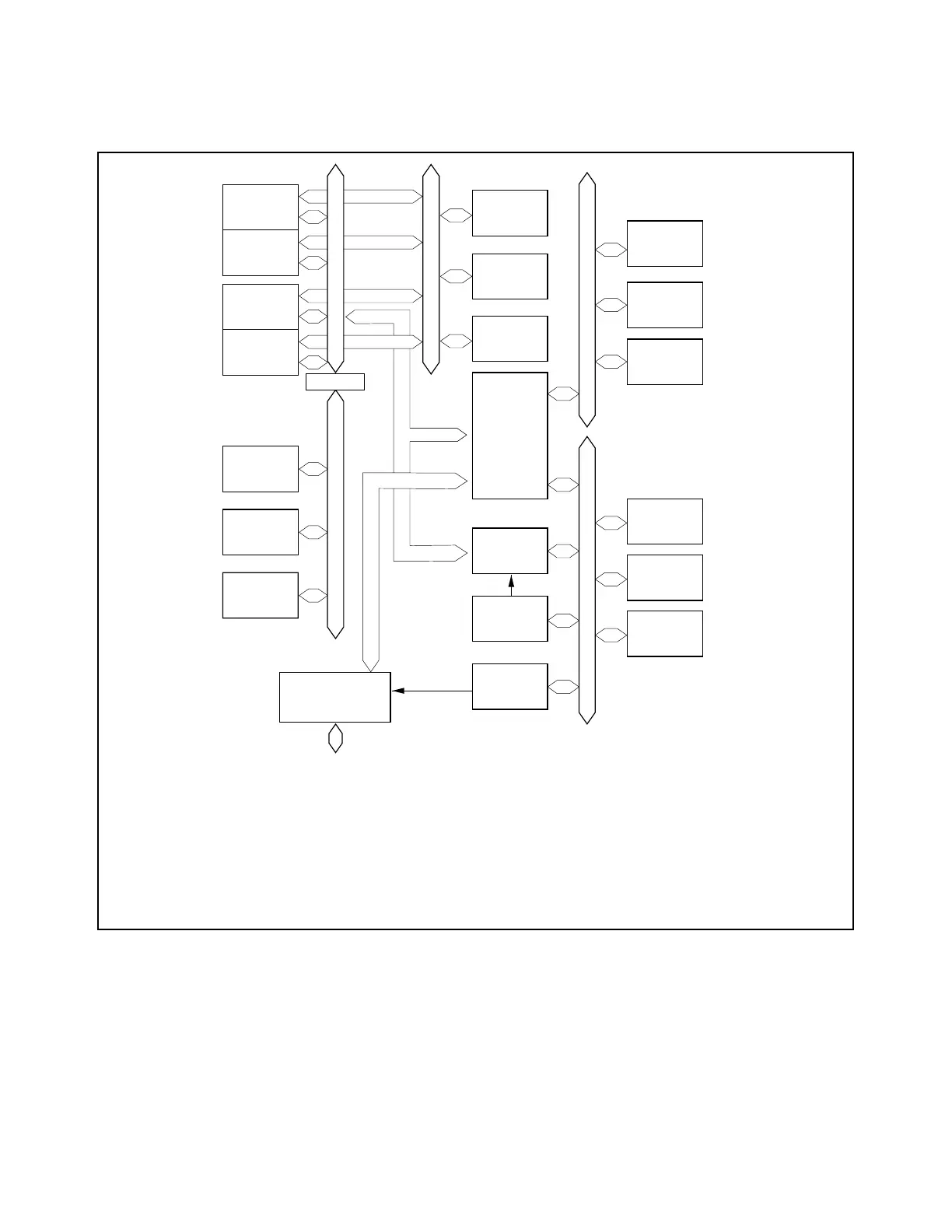

— 23 —

MMU

TLB

CPU

UBC

SCI

TMU

RTC

SCIF

ADC

DAC

AUD

DMAC

CMT

I/O port

External bus

interface

BSC

CCN

CACHE

H-UDI

INTC

CPG/WDT

Peripheral bus 1

Peripheral bus 2

I bus 1I bus 2

L bus

Legend:

ADC:

AUD:

BSC:

CACHE:

CCN:

CMT:

CPG/WDT:

CPU:

DAC:

A/D converter

Advanced user debugger

Bus state controller

Cache memory

Cache memory controller

Compare match timer

Clock pulse generator/watchdog timer

Central processing unit

D/A converter

DMAC:

H-UDI:

INTC:

MMU:

RTC:

SCI:

SCIF:

TLB:

TMU:

UBC:

Direct memory access controller

Hitachi user-debugging interface

Interrupt controller

Memory management unit

Realtime clock

Serial communication interface (with smart card interface)

Serial communication interface (with FIFO)

Address translation buffer

Timer unit

User break controller

BRIDGE

5-7-2. Block Diagram

Loading...

Loading...