— 31 —

■ HOST INTERFACE

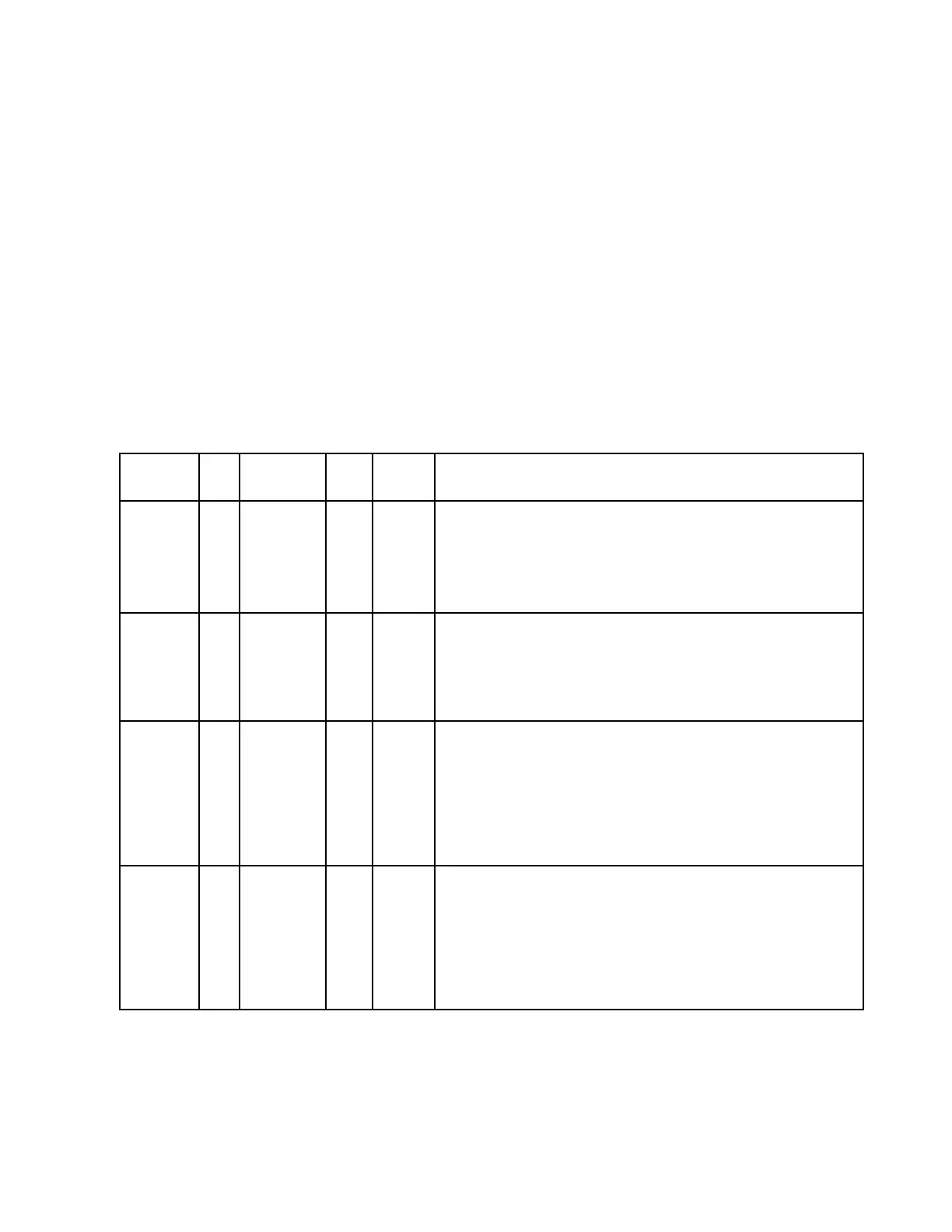

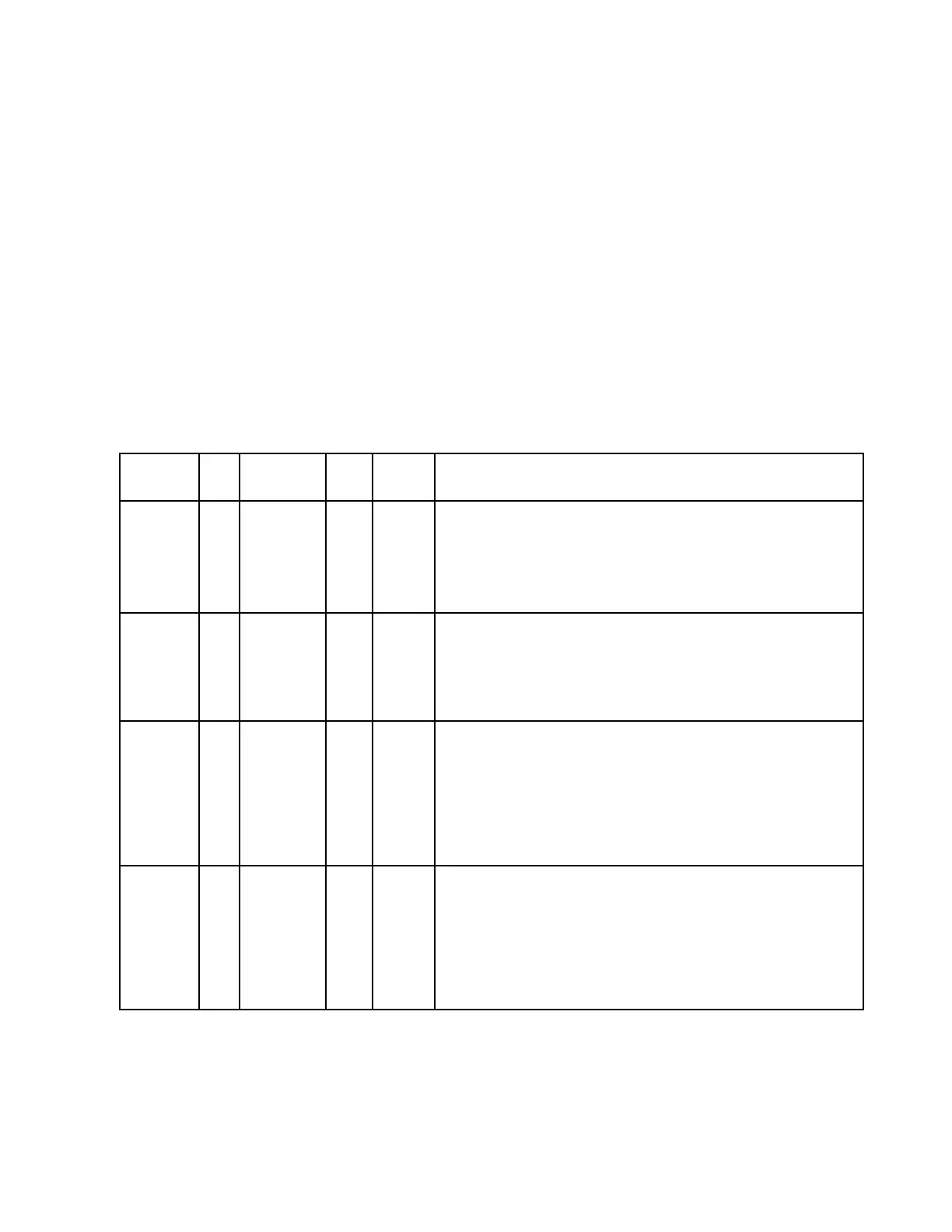

Pin Names Type Pin# Cell RESET# Description

State

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs system address bit 0 (A0).

• For MC68K #1, this pin inputs the lower data strobe (LDS#).

AB0 I 70 CS Input • For MC68K #2, this pin inputs system address bit 0 (A0).

• For Generic #1, this pin inputs system address bit 0 (A0).

• For Generic #2, this pin inputs system address bit 0 (A0).

45, 53, 54,

55, 56, 57,

AB[16:1] I 58, 59, 62, C Input These pins input the system address bits 16 through 1 (A[16:1]).

63, 64, 65,

66, 67, 68,

69

These pins have multiple functions.

• For SH-3/SH-4 mode, these pins are connected to [D15:0].

3, 4, 5, 6, 7, • For MC68K #1, these pins are connected to D[15:0].

DB[15:0] IO 8, 9, 11, 12, C/TS2 Hi-Z • For MC68K #2, these pins are connected to D[31:16] for a

13, 14, 15, 32-bit device (e.g. MC68030) or D[15:0] for a 16-bit device

16, 17, 18, (e.g. MC68340).

19 • For Generic #1, these pins are connected to D[15:0].

• For Generic #2, these pins are connected to D[15:0].

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs the write enable signal for

the lower data byte (WE0#).

• For MC68K #1, this pin must be tied to IO V DD

WE0# I 77 CS Input • For MC68K #2, this pin inputs the bus size bit 0 (SIZ0).

• For Generic #1, this pin inputs the write enable signal for the

lower data byte (WE0#).

• For Generic #2, this pin inputs the write enable signal (WE#).

5-10-3. Pin Function

■ KEY

I = Input

O = Output

IO = Bi-Directional (Input/Output)

P = Power pin

C = CMOS level input

CS = CMOS level Schmitt input

COx = CMOS output driver, x denotes driver type (see I OL /I OH in Table 6-4: “Output Specifications,” on

page 25)

TSx = Tri-state CMOS output driver, x denotes driver type (see I OL /I OH in Table 6-4: “Output Specifications,”

on page 25)

CNx = CMOS low-noise output driver, x denotes driver type (see I OL /I OH in Table 6-4: “Output

Specifications,” on page 25)

TEST = CMOS level test input with pull down resistor

Loading...

Loading...