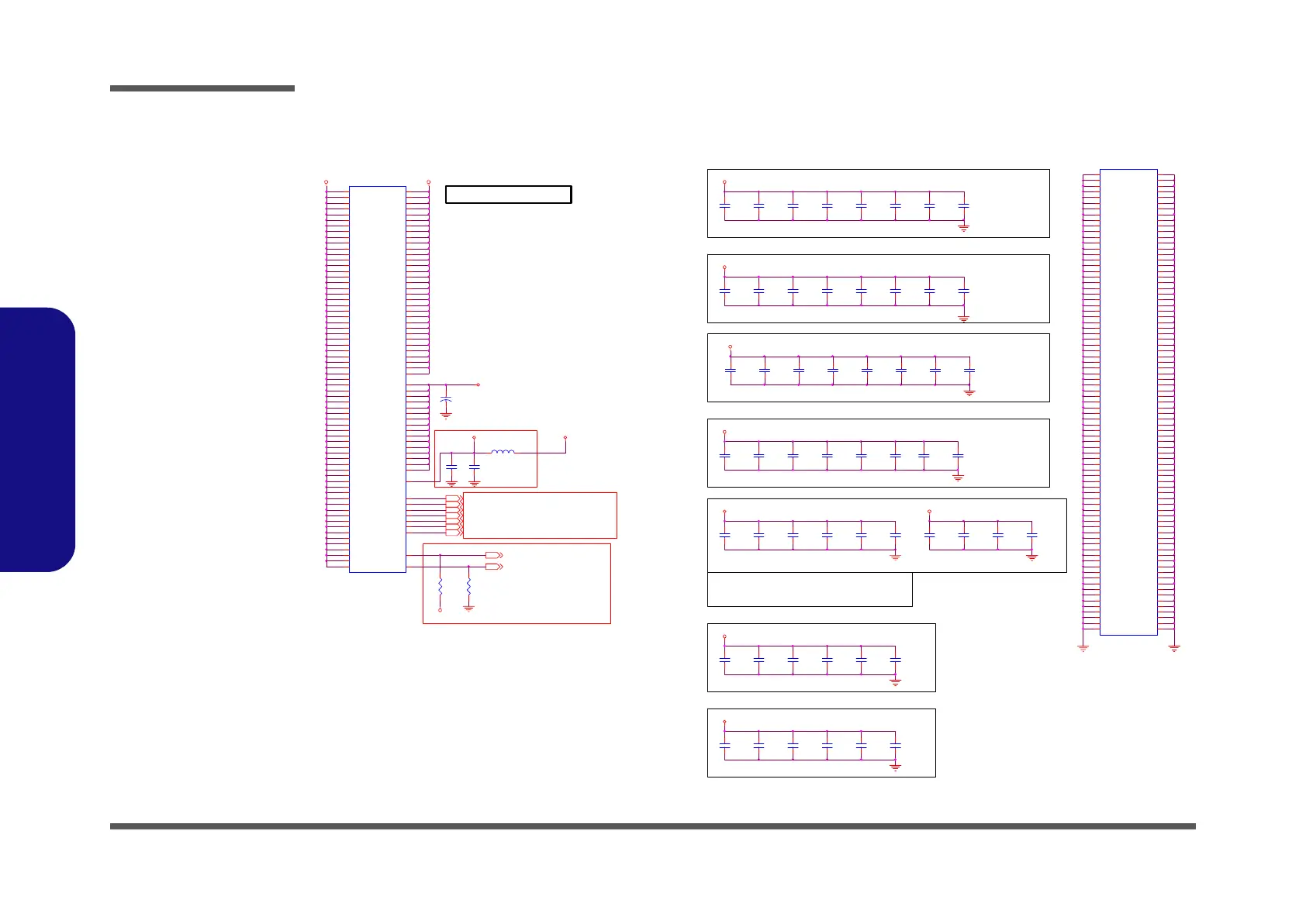

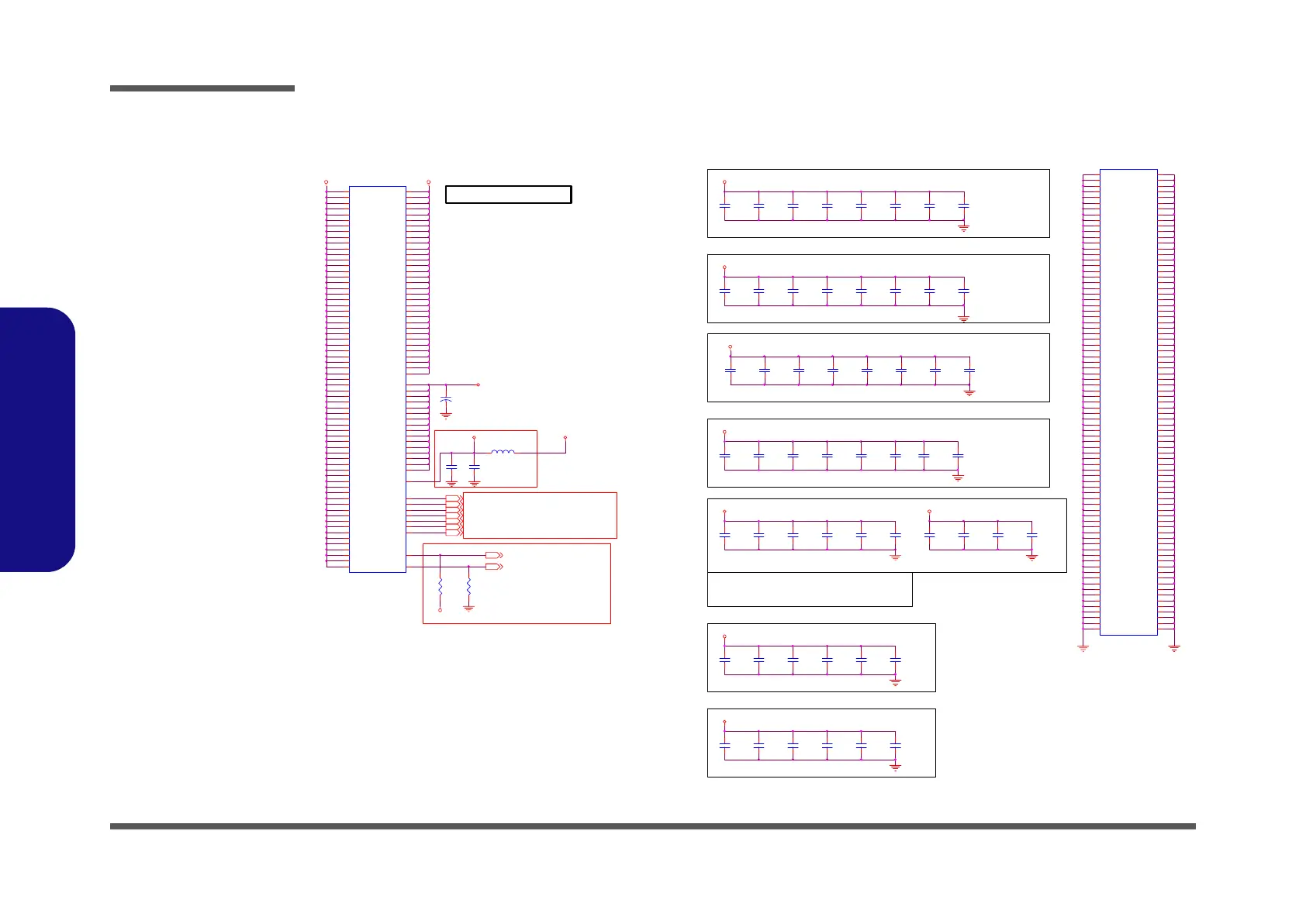

Schematic Diagrams

B - 4 PROCESSOR 2/2

B.Schematic Diagrams

PROCESSOR 2/2

C444

22U_6.3V_08

C43

10u/10V_08

Place these inside socket cavity on L1 (South side Primary)

C44

10u/10V_08

C67

10u/10V_08

C41

1U_50V_06

+VCORE

H_VID6

C440

1U_50V_06

+1.5VS

VID[6..0] trace:space (4:8

or 5:10),Zo=55ohm +-15%

R25

100_1%_06

C42

10u/10V_08

L26 HCB1608KF-121T25

C441

22U_6.3V_08

Place these inside socket cavity on L1 (South side Primary)

H_VID1

VSSSENSE

C446

22U_6.3V_08

Layout note:

C432

22U_6.3V_08

C439

22U_6.3V_08

C64

10u/10V_08

+VCORE

H_VID2 28

C454

22U_6.3V_08

+VCORE

C466

0.01u/25V_04

Layout note:

C453

0.1u/16V_04

C31

0.1u/16V_04

Place these inside socket cavity on L8 (North side secondary)

H_VID3 28

H_VID4 28

Place these inside socket cavity on L1 (South side Primary)

C69

1U_50V_06

+VCORE

C443

1U_50V_06

C66

10u/10V_08

2.5A

+1.05VS

C452

0.1u/16V_04

VCCSENSE 28

C26

0.1u/16V_04

C434

0.1u/16V_04

C38

10u/10V_08

VSSSENSE 28

H_VID3

H_VID0

Near pin B26

Boost Voltage 1.2V

Place these inside socket cavity on L8 (South side secondary)

viax20

H_VID1 28

H_VID5 28

C433

0.1u/16V_04

C74

0.1u/16V_04

+VCORE

C435

0.1u/16V_04

Place these inside socket cavity on L8 (North side secondary)

10A 400MIL

H_VID5

C60

10u/10V_08

C438

22U_6.3V_08

C48

10u/10V_08

Route VCCSENSE and

VSSSENSE traces at 27.4Ohm

with 50 mil spacing.

Place PU and PD within 1

inch of CPU.

JSKT1C

PZ47913-2741-01

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M2 1

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

+

C429

150U/4V_B

H_VID0 28

C40

1U_50V_06

Deeper Sleep Voltage 0.748V

R24

100_1%_06

C46

10u/10V_08

C45

10u/10V_08

+1.05VS

C436

22U_6.3V_08

+VCORE

C68

10u/10V_08

C47

10u/10V_08

C442

22U_6.3V_08

C450

22U_6.3V_08

C65

10u/10V_08

C445

22U_6.3V_08

JSKT1D

PZ47913-2741-01

A4

A8

A11

A14

A16

A19

A23

A26

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VSS[001]

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

VSS[009]

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

VSS[017]

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

VSS[023]

VSS[024]

VSS[025]

VSS[026]

VSS[027]

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

VSS[035]

VSS[036]

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

VSS[044]

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

VSS[050]

VSS[051]

VSS[052]

VSS[053]

VSS[054]

VSS[055]

VSS[056]

VSS[057]

VSS[058]

VSS[059]

VSS[060]

VSS[061]

VSS[062]

VSS[063]

VSS[064]

VSS[065]

VSS[066]

VSS[067]

VSS[068]

VSS[069]

VSS[070]

VSS[071]

VSS[072]

VSS[073]

VSS[074]

VSS[075]

VSS[076]

VSS[077]

VSS[078]

VSS[079]

VSS[080]

VSS[081]

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

Place these inside socket cavity on L1 (North side Primary)

VCCSEN SE

C73

0.1u/16V_04

C447

0.1u/16V_04

C70

1U_50V_06

C39

10u/10V_08

130mA

C449

22U_6.3V_08

C61

10u/10V_08

Layout note:

+VCORE

C467

10u/10V_08

C76

0.1u/16V_04

H_VID2

CPUVS Decoupling Guidelines : 1.5mOhm

used 330uF * 6 ( max ESR = 9mOhm / cap. )

& 3mOhm used 22uF * 32 MLCC

+VCCA_CPU

C27

0.1u/16V_04

C75

0.1u/16V_04

H_VID6 28

+1.05VS

C437

22U_6.3V_08

H_VID4

6 * 330uF (9mohm ESR each, 1.8nH ESL each)

3 on the north , 3 on the south

+VCORE

C63

10u/10V_08

C28

0.1u/16V_04

C29

0.1u/16V_04

C62

10u/10V_08

C448

22U_6.3V_08

C30

0.1u/16V_04

Layout

note:

+VCORE

Sheet 3 of 39

PROCESSOR 2/2

Loading...

Loading...