1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

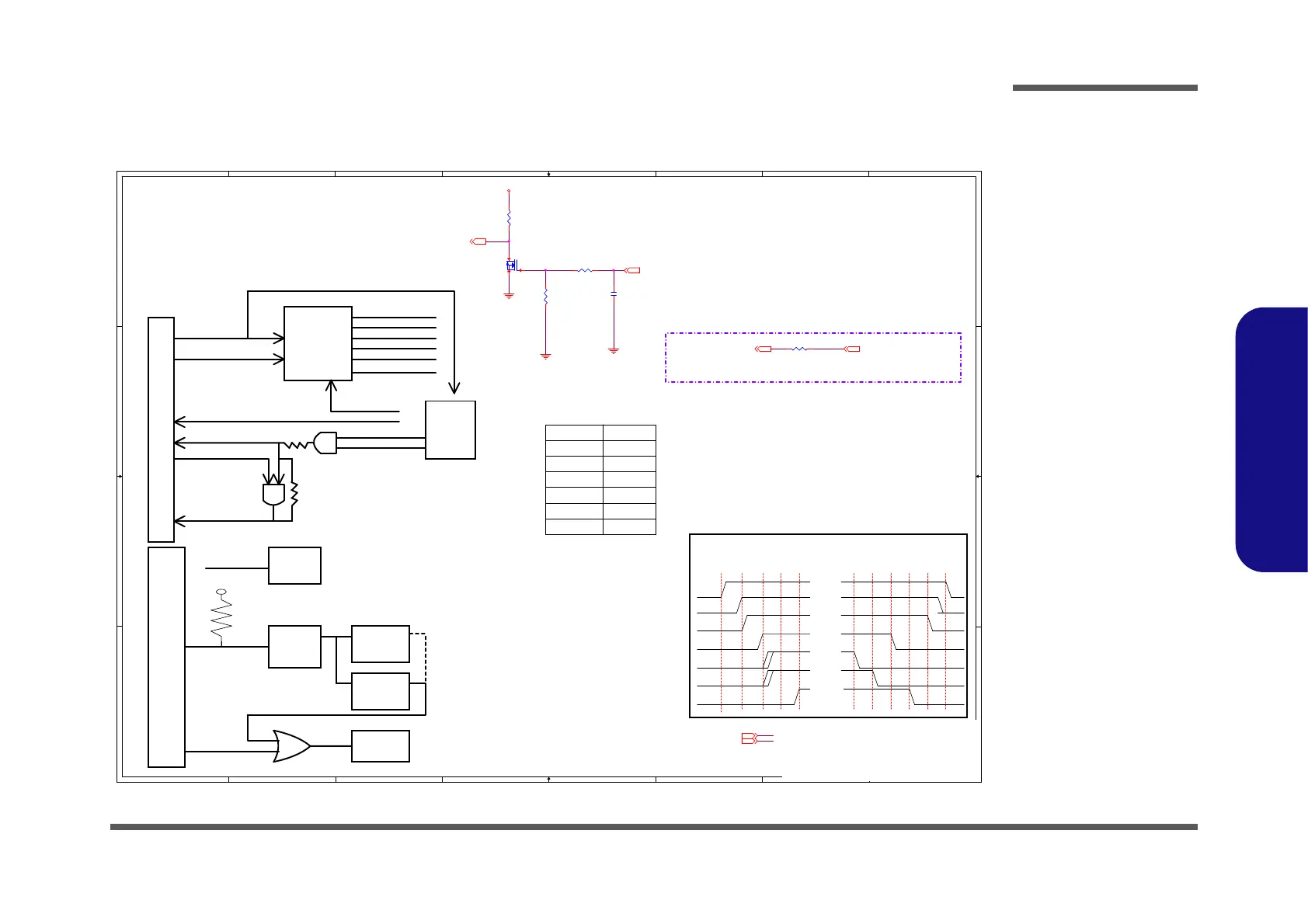

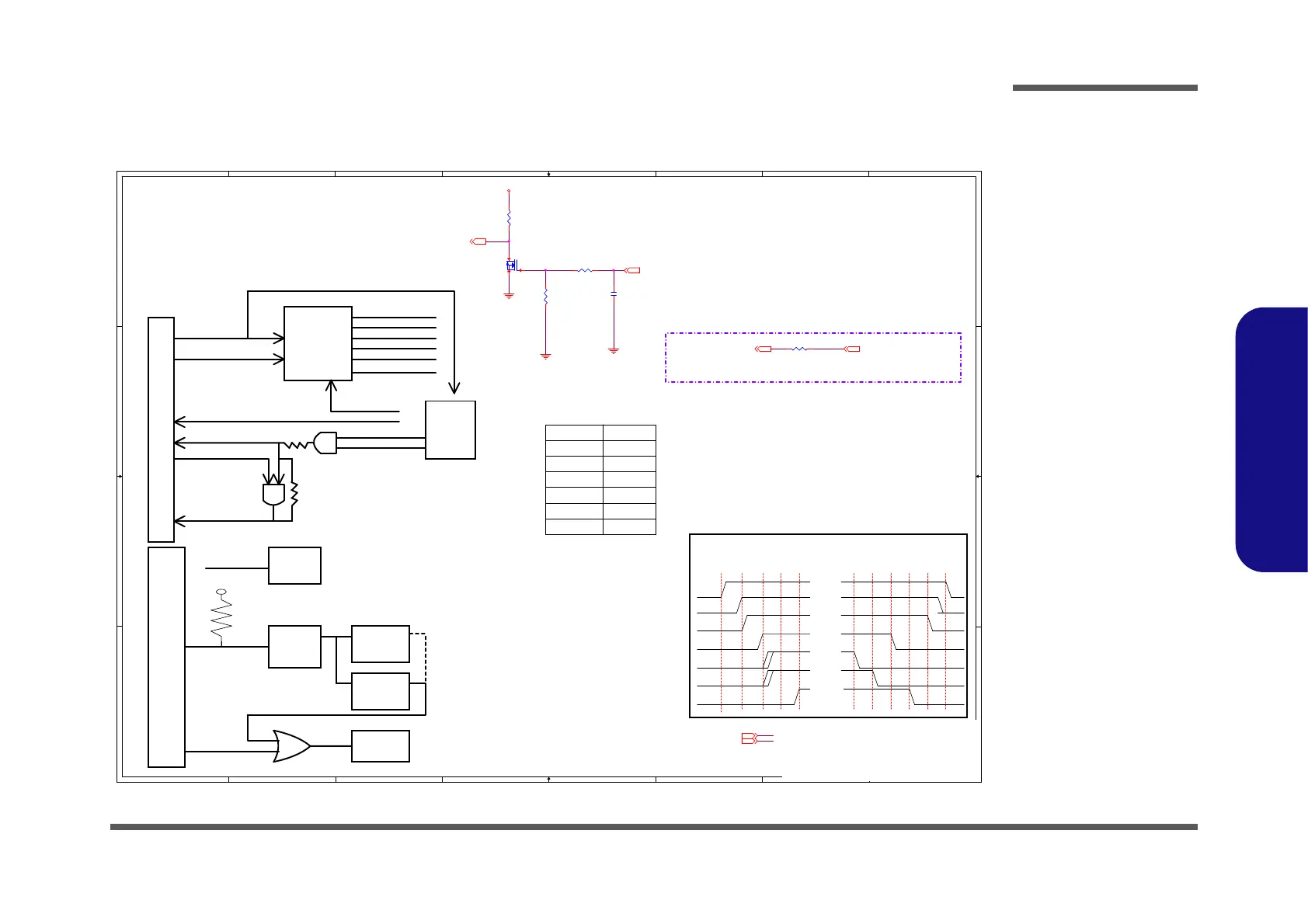

NVIDIA GPIO LEVEL SHIFT

GC6 2.1 Control Signals

1.1V8_MAIN_EN

2.GC6_FB_EN

3.GPU_EVENT#

4.GPU_PEX_RST_HOLD#

5.SYS_PEX_RST_MON#

GPU

1V8_MAIN_EN

GC6_FB_EN

VR Complex

1V8_AON

1V8_MAIN

NVVDD

PEX&1.05V

NVVDDS

EC/PCH

GPU_PWR_EN

GPU_EVENT#

GPU_RST#

PLATFORM_RST#

SYS_PEX_RST_MON#

GPU_PEX_RST_HOLD#

GPU_PEX_RST#

FBVDD/Q

FROM 8330B_RE

DP_E

GC6 2.1 - VR Complex

1. GPU_PWR_EN

2. 1V8_MAIN_EN

3. GC6_FB_EN

GPU

GPU_PWR_EN

(SYSTEM)

1V8_AON

1V8_AON

1V8_MAIN_EN 1V8_MAIN

PEX&1.05V

NVVDD

FBVDD/Q

EN

EN

EN

EN

EN

PGOOD

PGOOD PGOOD

PGOOD

GC6_FB_EN

PGOOD

DG P.93 note: t1(from 1V8_RUN_EN to PEX_VDD/NVVDD_PG) must NOT exceed 4ms.

N17E

FBVDDQ

POWER ON SEQUENCE POWER OFF SEQUENCE

GPPG8_PCH_1V8RUN_EN (GPP_G8) (1V8_MAIN)

GPPG9_PCH_NV3V3_EN (GPP_G9) (NV3V3)

GPPG10_PCH_NVVDD_EN (GPP_G10) (NVVDD)

GPPG11_PCH_NVVDDS_EN (GPP_G11) (NVVDDS)

GPPG0_PCH_PEXVDD_EN (GPP_G0) (PEX_VDD)

net PCH_GPIO Voltage

DGPU_PWR_EN (GPP_F23) (1V8_AON)

POWER RAIL

State in GC6

1V8_AON

1V8_MAIN

PEX&1.05V

NVVDD

ON

OFF

OFF

OFF

FBVDD/Q ON

NVVDDS OFF

9/13 Common Design

D02_12/19_H

1V8_AON

1V8_AON10,16,17,51,52,53

GPIO4_1V8_MAIN_EN 16,17GPIO4_1V8_MAIN_EN_R24

3.3VS8,9,20,21,22,23,24,26,27,28,29,32,34,36,37,38,39,40,41,42,47,51,52,53

MDP_E_HPD 21,28

IFPE_HPD_R#16

Title

Size Document Number R e v

Date: Sheet

of

6-71-N85J0-D01

D02B

[18] NVIDIA GPIO LEVEL SHIFT

A3

18 63Friday, March 02, 2018

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size Document Number R e v

Date: Sheet

of

6-71-N85J0-D01

D02B

[18] NVIDIA GPIO LEVEL SHIFT

A3

18 63Friday, March 02, 2018

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size Document Number R e v

Date: Sheet

of

6-71-N85J0-D01

D02B

[18] NVIDIA GPIO LEVEL SHIFT

A3

18 63Friday, March 02, 2018

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

R314

10K_04

Q5

MTN2002ZS3

G

DS

R77 1K_04

C281 220p_50V_NPO_04

R60 100K_04

R296 *0_04

Loading...

Loading...