5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CNVI

CLOSE TO CPU

HDA_SDO/HDA_SYNNC/HDA_BCLK/HDA_RST#

CAP should be close PCH

Trace Length <1"

CLOSE TO CPU

GPP_R2

HIGH: OVERRIDEN

WEAK INTERNAL PD 20K

LOW: SECURITY MEASURES NOT OVERRIDEN

FLASH DESCRIPTOR SECURITY OVERRIDE

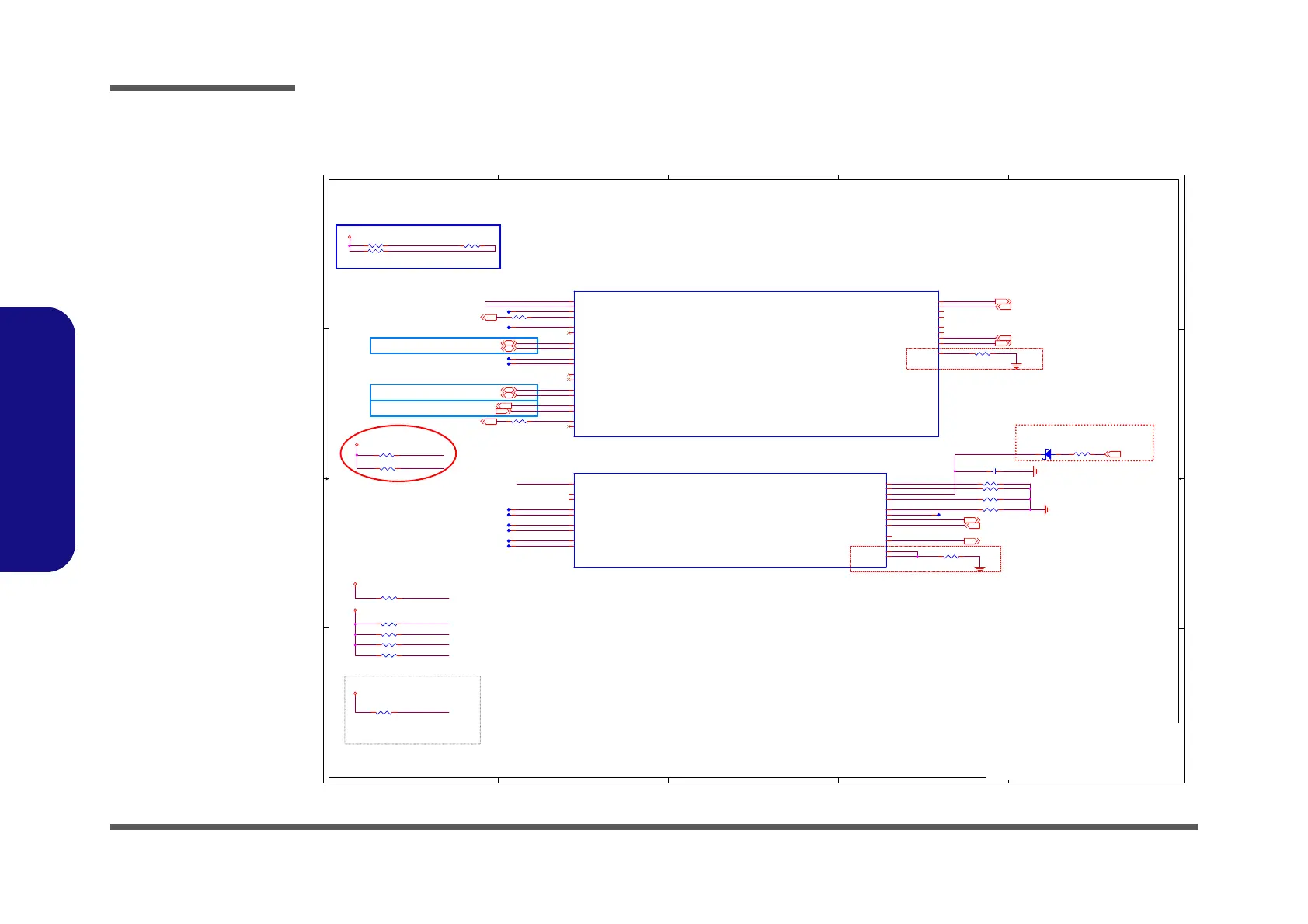

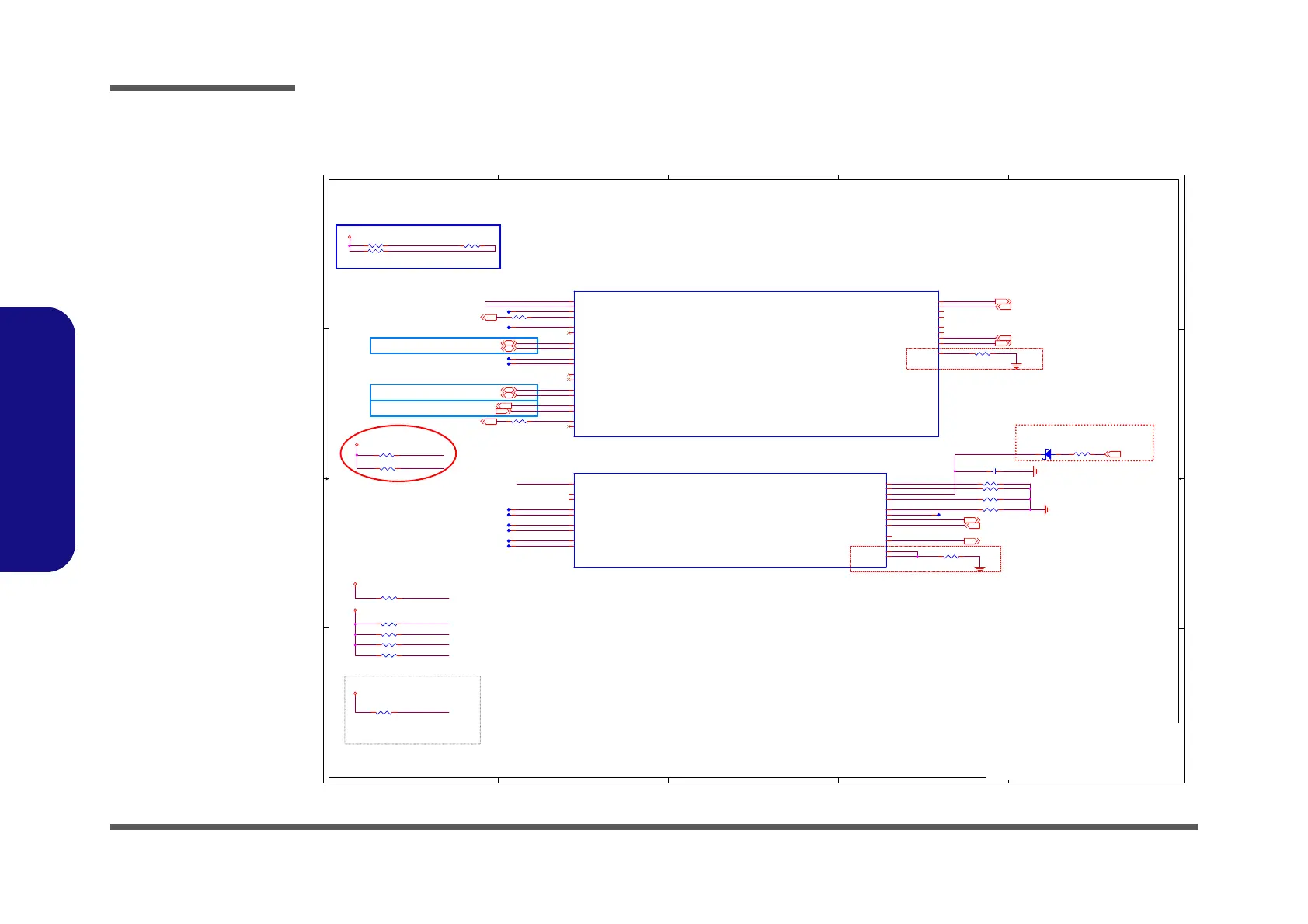

ADL-P I2C, ISH, AUDIO

㒢

BOT

朊暨⎗

REWORK

天攫㔋䅙䇯

Touch PAD

㓦伖

BOT

朊

㉮味⎗㉱䶂⛘㕡

For BIOS Debug

Type-C

Follow NJ50MU, 0615

3.3VS

3.3VA

3.3VA

VDD3

3.3VA

ME_WE 32

PCH_BT_EN 29

WLAN_WAKEUP#_R 29

DMIC_DATA 31

DMIC_CLK 31

SB_BLON 17

CNVI_MFUART2_RXD29

CNVI_MFUART2_TXD29

SB_KBCRST# 32

SSD1_PWR_EN 24

T_SCL31

T_SDA31

DEVSLP07,25

WLAN_RST#10,29

I2C3_SDA23

I2C3_SCL23

Title

Size Document Number Rev

Date: Sheet

of

6-7P-NJ5P5-002

D02

[05] ADL-P F,G/22 I2C, AUDIO

A3

548Monday, July 25, 2022

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

NJ50MU

Title

Size Document Number Rev

Date: Sheet

of

6-7P-NJ5P5-002

D02

[05] ADL-P F,G/22 I2C, AUDIO

A3

548Monday, July 25, 2022

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

NJ50MU

Title

Size Document Number Rev

Date: Sheet

of

6-7P-NJ5P5-002

D02

[05] ADL-P F,G/22 I2C, AUDIO

A3

548Monday, July 25, 2022

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

NJ50MU

R292 *0_04

R681 200_1%_04

<Function>

BMAP_REV = 0.52

NA_71925

U48G

IC

INS116301456

7 OF 22

<Function>

EY48

GPP_S7/SNDW3_DATA/DMIC_DATA1

EW48

GPP_S6/SNDW3_CLK/DMIC_CLK_A1

EY50

GPP_S5/SNDW2_DATA/DMIC_CLK_B1

EV50

GPP_S4/SNDW2_CLK/DMIC_CLK_B0

FC50

GPP_S3/SNDW1_DATA/DMIC_DATA0/I2S1_RXD

FA50

GPP_S2/SNDW1_CLK/DMIC_CKL_A0/I2S1_TXD

EY53

GPP_S1/SNDW0_DATA/I2S1_SFRM

EV53

GPP_S0/SNDW0_CLK/I2S1_SCLK

EY34

GPP_D19/I2S_MCLK1_OUT

FC53

SNDW_RCOMP_2

FA53

SNDW_RCOMP_1

DV47

GPP_A13/PMC_I2C_SCL

DV51

GPP_A11/PMC_I2C_SDA

EB46

GPP_R7/I2S2_RXD/DMIC_DATA1

EB44

GPP_R6/I2S2_TXD/DMIC_CLK_A1

ET53

GPP_R5/HDA_SDI1/I2S2_SFRM/DMIC_DATA0

ER53

GPP_R4/HDA_RST#/I2S2_SCLK/DMIC_CLK_A0

ER59

GPP_R3/HDA_SDI0/I2S0_RXD/HDAPROC_SDI

ER57

GPP_R2/HDA_SDO/I2S0_ TXD /HDAPROC_ SDO

EP60

GPP_R1/HDA_SYNC/I2S0_SFRM/DMIC_CLK_B1

ER56

GPP_R0/HDA_BCLK/I2S0_SCLK/DMIC_CLK_B0/HDAPROC_BCLK

R291 *0_04

BMAP_REV = 0.52

NA_71925

U48F

IC

INS116301360

6 OF 22

<Function>

DN57

GPP_B16/I2C5_SDA/ISH_I2C2_SDA

DN60

GPP_B17/I2C5_SCL/ISH_I2C2_SCL

EL43

GPP_H8/I2C4_SDA/CNV_MFUART2_RXD

EN43

GPP_H9/I2C4_SCL/CNV_MFUART2_TXD

DR58

GPP_B7/ISH_I2C1_SDA/I2C3_SDA

DR56

GPP_B8/ISH_I2C1_SCL/I2C3_SCL

DT56

GPP_B5/ISH_I2C0_SDA/I2C2_SDA

DT57

GPP_B6/ISH_I2C0_SCL/I2C2_SCL

EF43

GPP_H6/I2C1_SDA

EH43

GPP_H7/I2C1_SCL

EF46

GPP_H4/I2C0_SDA

EH46

GPP_H5/I2C0_SCL

EV34

GPP_D17/UART1_RXD/ISH_UART1_RXD

EW30

GPP_D18/UART1_TXD/ISH_UART1_TXD

EK41

GPP_H12/I2C7_SDA/UART0_RTS#/M2_SKT2_CFG2/ISH_GP6B/DEVSLP0B

EL41

GPP_H13/I2C7_SCL/UART0_CTS#/M2_SKT2_CFG3/ISH_GP7B/DEVSLP1B

EN46

GPP_H10/UART0_RXD/M2_SKT2_CFG0

EN48

GPP_H11/UART0_TXD/M2_SKT2_CFG1

DR61

GPPC_RCOMP

EV31

GPP_D0/ISH_GP0/BK0/SBK0

EY31

GPP_D1/ISH_GP1/BK1/SBK1

EY30

GPP_D2/ISH_GP2/BK2/SBK2

FA34

GPP_D3/ISH_GP3/BK3/SBK3

EW36

GPP_D15/ISH_UART0_RTS#/I2C7B_SDA

EY36

GPP_D16/ISH_UART0_CTS#/I2C7B_SCL

EV28

GPP_D13/ISH_UART0_RXD/I2C4B_SDA

EY28

GPP_D14/ISH_UART0_TXD/I2C4B_SCL

D56RB751S-40H

AC

R720 2.2K_04

R253 *0_04

R662 *10K_04

R644

2.2K_04

R266 *0_04

R232 *200K_04

R682 0_04

R664 10K_04

R285 *0_04

R283

*1K_04

R653

*2.2K_04

R657 10K_04

R667 *0_06

R257 200_1%_04

R719 2.2K_04

R284

*1K_04

R666 *10K_04

C480 *2p_25V_NPO_02

PCH_MUTE#

GPP_D18

HDA_SDIN0

HDA_SYNC

HDA_RST#

HDA_BITCLK

HDA_SDOUT

HDA_SDOUT

UART0_TX

SB_KBCRST#

UART0_RX

T_SCL

T_SDA

GPP_H13

GPP_D19

GPP_D19

SB_KBCRST#

WLAN_WAKEUP#_R

UART0_RX

UART0_TX

I2C3_SCL

I2C3_SDA

I2C3_SCL

I2C3_SDA

Loading...

Loading...