D D

C C

B B

A A

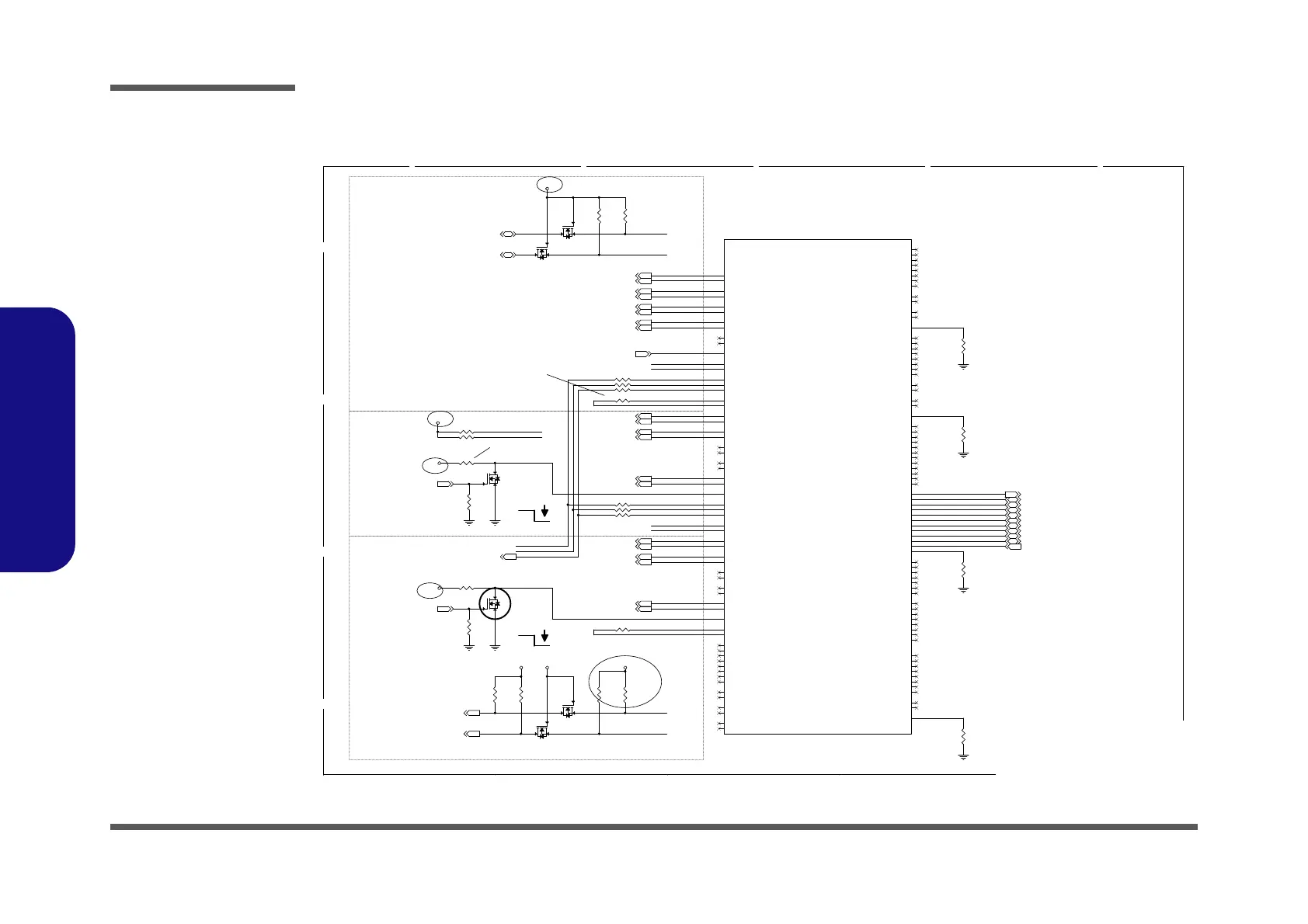

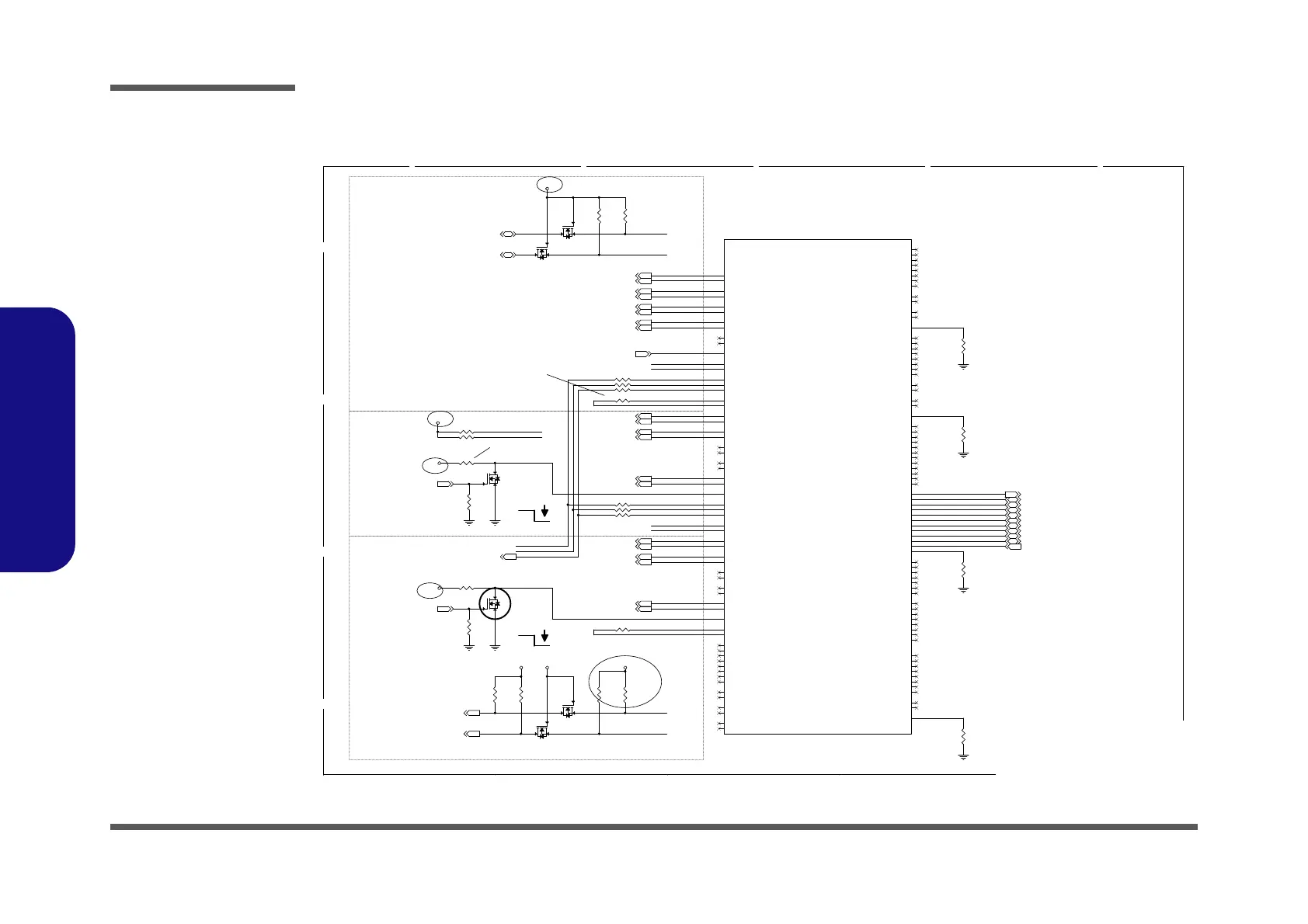

eDP

VGA

HDMI

ON

ON

Note: There is no need to

have a RCOMP for DDI0.

Please ensure that the

eDP_RCOMP pin is populated

with the correct value. The

SoC will use the eDP_RCOMP

value for DDI Port0 as

well.

DDI_HPD is input port so pull

high to 1.8VS.

Internal PU 20K CMOS

BIOS modify GPIO_199 to P_20K_Hi

DDI_HPD is input port so pull

high to 1.8VS.

2016/5/30

delete net

Note: It is required to enable

internal 20k pull up resistor on

the HV_DDIx_HPD signals by BIOS.

1109 Modify

1109 Modify

1109 Modify

1109 Modify

1109 Modify

MCSI_DPHY1.2_RCOMP

VGA_HPD_R

HDMI_CTRLDATA

HDMI_CTRLCLK

DDI0_PLLOBS_DP

DDI0_PLLOBS_DN

EDP_PLLOBS_DP

EDP_PLLOBS_DN

PANEL0_BKLTEN

PANEL0_BKLTCTL

PANEL0_VDDEN

PANEL1_VDDEN

PANEL1_BKLTCTL

PANEL1_BKLTEN

EDP_HPD_R

SOC_BKLTEN

SOC_BRIGHTNESS EMMC_RCOMP

MDSI_RCOMP

MCSI_DPHY1.1_RCOMP

DDI1_CTRLCLK

DDI1_CTRLDATA

DDI1_CTRLCLK

DDI1_CTRLDATA

SOC_BRIGHTNESS

SOC_BKLTEN

HDMI_CTRLDATA

HDMI_CTRLCLK

1.8VA

1.8VA

1.8VA

3.3VS 1.8VS

1.8VA

1.8VA

EDP_HPD13,14

EMMC_STROBE 10

HDMI_HPD16

VGA_HPD15

HDMIC_C0CN16

HDMIC_C0CP16

HDMIC_C1CN16

HDMIC_C1CP16

HDMIC_C2CN16

HDMIC_C2CP16

HDMIC_CLKCN16

HDMIC_CLKCP16

VGA_LANE0P15

VGA_LANE1N15

VGA_LANE1P15

VGA_LANE0N15

VGA_AUX_CH_P15

VGA_AUX_CH_N15

SOC_ENAVDD14

EDP_AUXN13

EDP_TXN_013

EDP_TXP_013

EDP_TXN_113

EDP_TXP_113

EDP_AUXP13

EMMC_CLK 10

EMMC_DAT3 10

EMMC_DAT0 10

EMMC_DAT1 10

EMMC_DAT4 10

EMMC_DAT5 10

EMMC_DAT2 10

EMMC_DAT6 10

EMMC_DAT7 10

EMMC_CMD 10

EDP_BLON14

EDP_BRIGHTNESS13

HDMI_SCL-C16

HDMI_SDA-C16

Title

Size Document Number R e v

Date: Sheet

of

1.0

[03] APL SOC_2/8_DISPLAY,eMMC

A3

3

33Tuesday, November 15, 2016

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

W940PU_D02

6-71-W94P0-D02

Title

Size Document Number R e v

Date: Sheet

of

1.0

[03] APL SOC_2/8_DISPLAY,eMMC

A3

3

33Tuesday, November 15, 2016

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

W940PU_D02

6-71-W94P0-D02

Title

Size Document Number R e v

Date: Sheet

of

1.0

[03] APL SOC_2/8_DISPLAY,eMMC

A3

3

33Tuesday, November 15, 2016

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

W940PU_D02

6-71-W94P0-D02

S

D

G

Q14A

MTDK3S6R

2

6 1

S

D

G

Q20B

MTDK3S6R

5

3 4

R40 402_1%_04

R319 *10K_04

R31 *4.7K_04

R304 *0_04

S

D

G

Q14B

MTDK3S6R

5

3 4

R36 *4.7K_04

R309 0_04

R316 *0_04

R303 0_04

R30

100K_04

R267

100K_04

R311 *0_04

S

D

G

Q24B

MTDK3S6R

5

34

R50

150_1%_04

R315 0_04

R265

100K_04

R341

10K_04

R342

10K_04

R38

150_1%_04

S

D

G

Q24A

MTDK3S6R

2

61

R277

100K_04

R63

200_1%_04

R37 *402_1%_04

R259

10K_04

APL_SOC

DDI0

DDI1

EDP

MCSI and Camera interface

EMMC

SDIO

MDSI_C

SDCARD

MDSI_A

U1C

GP_CAMERASB06

R35

GP_CAMERASB07

L34

GP_CAMERASB00

L37

GP_CAMERASB02

J34

GP_CAMERASB01

P34

GP_CAMERASB04

M37

GP_CAMERASB05

F30

GP_CAMERASB03

H30

MDSI_A_DP_0

AP12

EDP_AUXN

AH9

DDI0_TXN_0

AK2

SDCARD_CMD

AC52

EDP_TXP_3

AC7

EDP_AUXP

AH10

DDI0_TXP_0

AK3

SDCARD_CLK

AB58

DDI0_RCOMP_P

AG1

EDP_TXP_0

AG7

EDP_TXP_2

AC6

EDP_TXN_3

AC9

EDP_RCOMP_P

AG6

EDP_RCOMP_N

AG5

DDI0_TXN_2

AH2

DDI0_TXP_2

AH3

SDCARD_D3

AB51

DDI0_RCOMP_N

AG2

EDP_TXN_0

AG9

EDP_TXN_2

AC5

DDI0_TXN_3

AL1

DDI0_TXP_3

AL2

SDCARD_D2

AC51

DDI0_AUXN

AM15

DDI0_AUXP

AM16

DDI0_TXP_1

AM3

DDI0_TXN_1

AM2

DDI1_TXN_0

AF3

SDCARD_D0

AC49

SDCARD_D1

AC48

EDP_TXP_1

AG12

DDI1_TXP_0

AF2

SDIO_CLK

P58

SDCARD_LVL_WP

AB55

SDCARD_CD_N

AB54

EDP_TXN_1

AG10

DDI1_AUXN

AK15

DDI1_TXP_1

AD3

DDI1_TXN_1

AD2

SDIO_D3

T55

SDIO_D2

T54

SDIO_CMD

T57

SDIO_PWR_DWN_N

P51

DDI1_TXN_2

AC2

DDI1_TXP_2

AC1

SDIO_D1

P57

SDIO_D0

T52

MSCI_RX_CLK0_N

J23

EMMC_D1

T58

DDI1_AUXP

AK16

DDI1_TXN_3

AB2

DDI1_TXP_3

AB3

EMMC_D0

V58

EMMC_CLK

Y58

MSCI_RX_CLK0_P

L23

EMMC_RCOMP

V59

MCSI_DPHY1.1_COMP

H27

MCSI_RX_DATA0_P

M23

MCSI_CLKN_2

F19

MCSI_CLKP_2

H19

PANEL1_BKLTEN

B53

PANEL1_BKLTCTL

C53

EMMC_CMD

Y51

EMMC_D3

V51

EMMC_D2

T59

GPIO_199_HV_DDI1_HPD

A50

PANEL1_VDDEN

C52

EMMC_D6

V55

EMMC_D7

V57

EMMC_RCLK

V54

MCSI_DP_3

F17

MCSI_DN_3

E17

MCSI_CLKP_0

M19

MCSI_CLKN_0

L19

DDI1_DDC_SCL

A54

DDI1_DDC_SDA

C54

EMMC_D4

V52

EMMC_D5

Y49

MDSI_RCOMP

AP7

GP_CAMERASB11

E30

MCSI_DP_1

P21

MCSI_DN_1

R21

MCSI_DN_2

J17

MCSI_DP_2

L17

PANEL0_BKLTCTL

C46

PANEL0_BKLTEN

B47

GPIO_200_HV_DDI0_HPD

C50

PANEL0_VDDEN

C47

GP_CAMERASB10

R34

GP_CAMERASB09

M35

GP_CAMERASB08

M34

MCSI_DP_0

P17

MCSI_DN_0

M17

HV_DDI0_DDC_SCL

B49

HV_DDI0_DDC_SDA

C49

MCSI_RX_DATA0_N

P23

MCSI_RX_DATA1_P

J21

MCSI_RX_DATA1_N

H21

MCSI_RX_DATA2_P

M25

MCSI_RX_DATA2_N

L25

MCSI_RX_DATA3_P

H25

MCSI_RX_DATA3_N

J25

MSCI_RX_CLK1_P

F25

MSCI_RX_CLK1_N

E25

MCSI_DPHY1.2_COMP

F27

MDSI_A_DN_0

AP10

MDSI_A_DP_1

AR2

MDSI_A_DN_1

AR1

MDSI_A_DP_2

AP15

MDSI_A_DN_2

AP13

MDSI_A_DP_3

AP6

MDSI_A_DN_3

AP5

MDSI_A_CLKP

AP2

MDSI_A_CLKN

AP3

MIPI_I2C_SDA

B51

MIPI_I2C_SCL

C51

MDSI_C_DP_0

AK7

MDSI_A_TE

M45

MDSI_C_TE

M43

MDSI_C_DN_0

AK6

MDSI_C_DP_1

AM5

MDSI_C_DN_1

AM6

MDSI_C_DP_2

AM12

MDSI_C_DN_2

AM10

MDSI_C_DP_3

AK13

MDSI_C_DN_3

AM13

MDSI_C_CLKP

AM9

MDSI_C_CLKN

AM7

EDP_HPD/PMC_SPI_FS1

P48

R248

10K_04

R33

150_1%_04

S

D

G

Q20A

MTDK3S6R

2

6 1

R318 *10K_04

Loading...

Loading...