CMT2300A

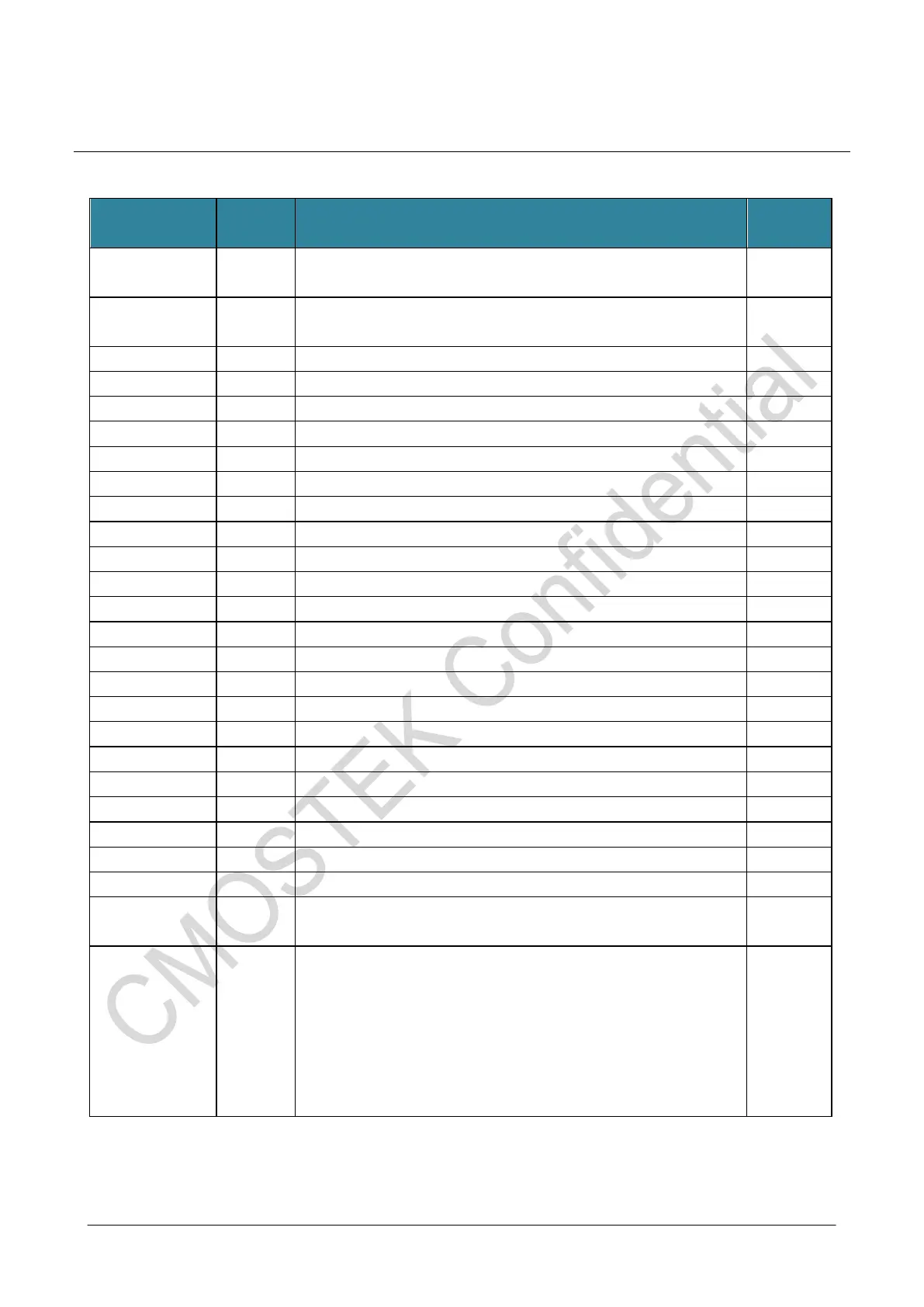

Table 18. CMT2300A interrupt mapping table

Indicates the chip is entering RX and is already in RX. It is 1 in PLL

Tuning and RX state, and it is 0 in the other states.

Indicates the chip is entering TX and is already in TX. It is 1 in PLL tuning

and TX state, and it is 0 in the other states.

Indicates whether the RSSI is active.

Indicates that the Preamble is received successfully.

Indicates that the Sync Word is received successfully.

Indicates that the Node ID is received successfully.

Indicates that the CRC for the current packet is correct.

Indicates that a packet has been received.

Indicates that the SLEEP counter timed out.

Indicates that the RX counter timed out.

Indicates that the TX operation is completed.

Indicates that the RX FIFO is not empty.

Indicates the number of unread bytes of the RX FIFO is over FIFO TH

Indicates RX FIFO is full.

Indicates each time a byte is written to the RX FIFO. Itis a pulse.

indicates RX FIFO is overflow

Indicates that TX FIFO is not empty

Indicates the number of unread bytes of the TX FIFO is over FIFO TH.

Indicates TX FIFO is full.

Indicates that the current state is STBY.

Indicates that the current state is RFS or TFS.

Indicates that the current state is RX.

Indicates that the current state is TX.

Indicates that low battery is detected (VDD is lower than TH)

Indicates the chip is entering TX or RX and is already in TX or RX. It is 1 in

PLL tuning, TX or RX state, and it is 0 in the other states.

Indicates that the current packet has been received, covering 4 possible

different situations.

1. The packet is received completely and correctly.

2. Manchester decoding has error. Decoder is automatically reset.

3. NODE ID receiving has error. Decoder is automatically reset.

4. Signal collision occurred. Decoder is not reset, waiting for MCU to

response.

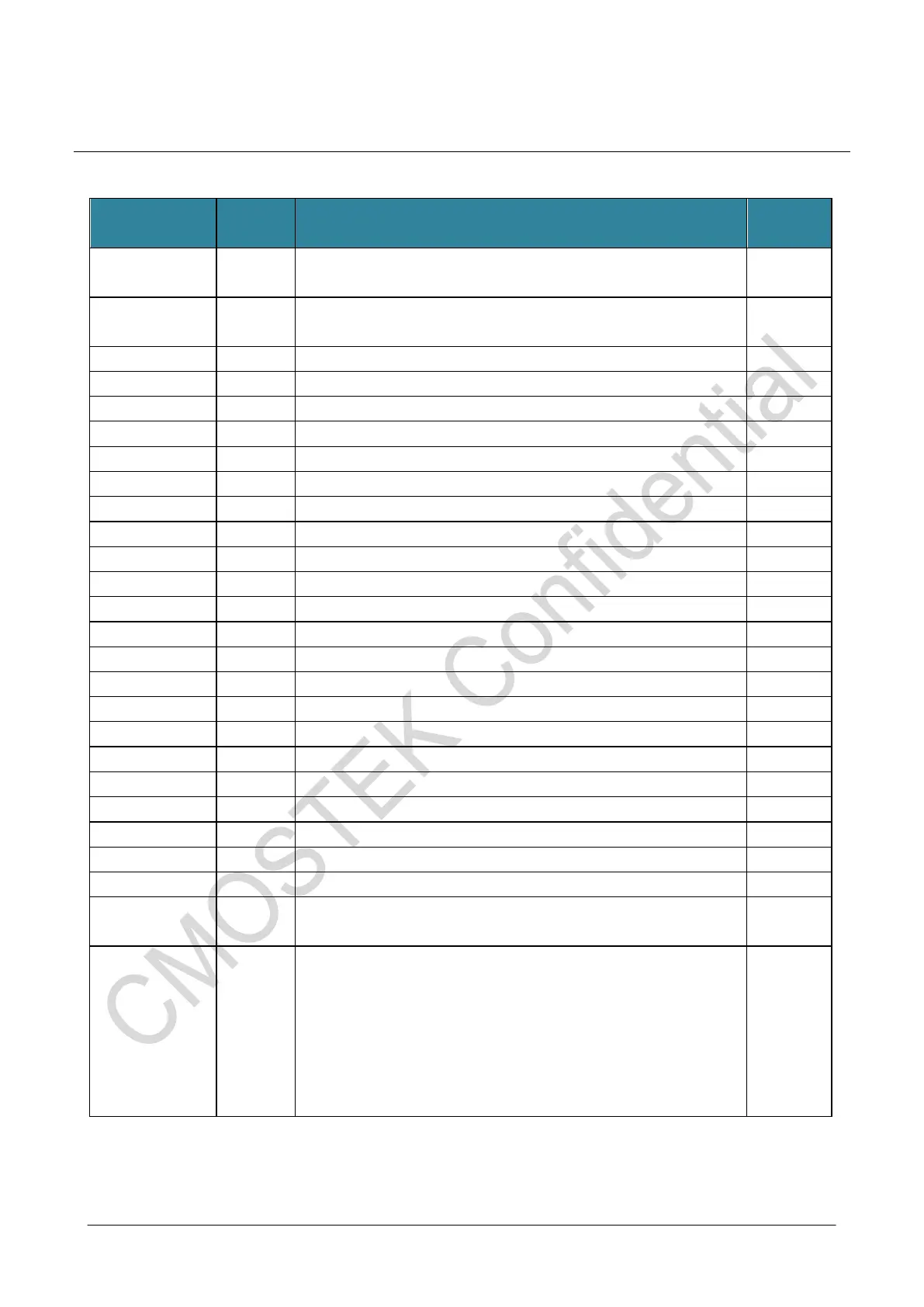

By default, Interrupt is active high (logic 1 is valid). Users can set the INT_POLAR register bit to 1 to make all interrupts active low

(logic 0 is valid).Taking INT1 as an example, the control and sources selection of all the available interrupts is shown below. The

control and mapping of INT1 and INT2 are the same.

Loading...

Loading...