CMT2380F17

Rev0.1 | 258/347

21 Two Wire serial Interface (TWI0/ I2C0)

The Two-Wire serial Interface is a two-wire, bi-directional serial bus. It is ideally suited for typical

microcontroller applications.

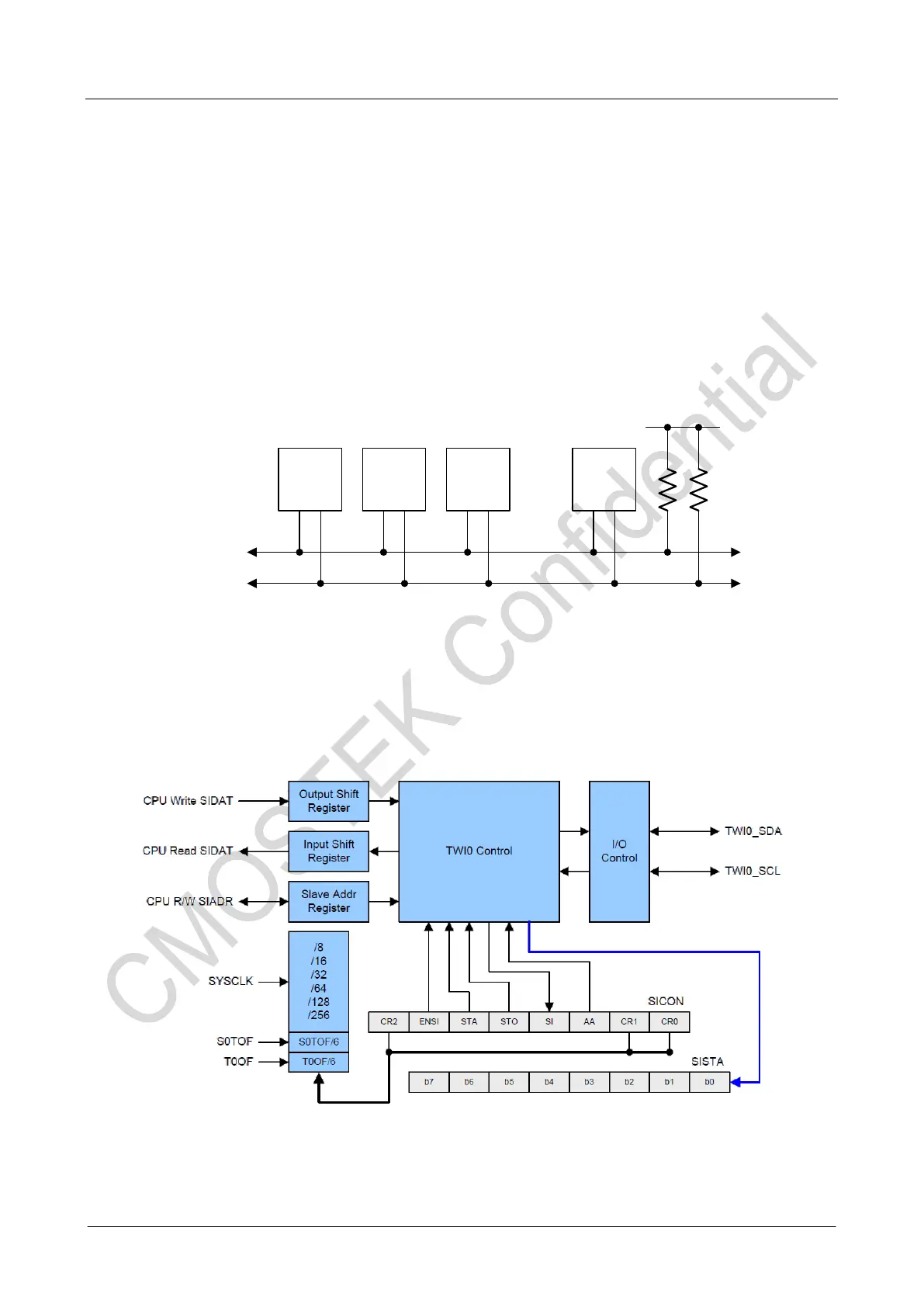

The TWI/ I2C protocol allows the systems designer to interconnect up to 128 different devices using only

two bi-directional bus lines, one for clock (TWI0_SCL) and one for data (TWI0_SDA). The TWI bus provides

control of TWI0_SDA (serial data), TWI0_SCL (serial clock) generation and synchronization, arbitration logic,

and START/STOP control and generation. The only external hardware needed to implement this bus is a

single pull-up resistor for each of the TWI bus lines. All devices connected to the bus have individual

addresses, and mechanisms for resolving bus contention are inherent in the TWI/ I2C protocol.

Device 0 Device 1 Device 2 Device n

TWI0_SDA

TWI0_SCL

VDD

………

Figure 21-1. TWI/ I2C Bus Interconnection

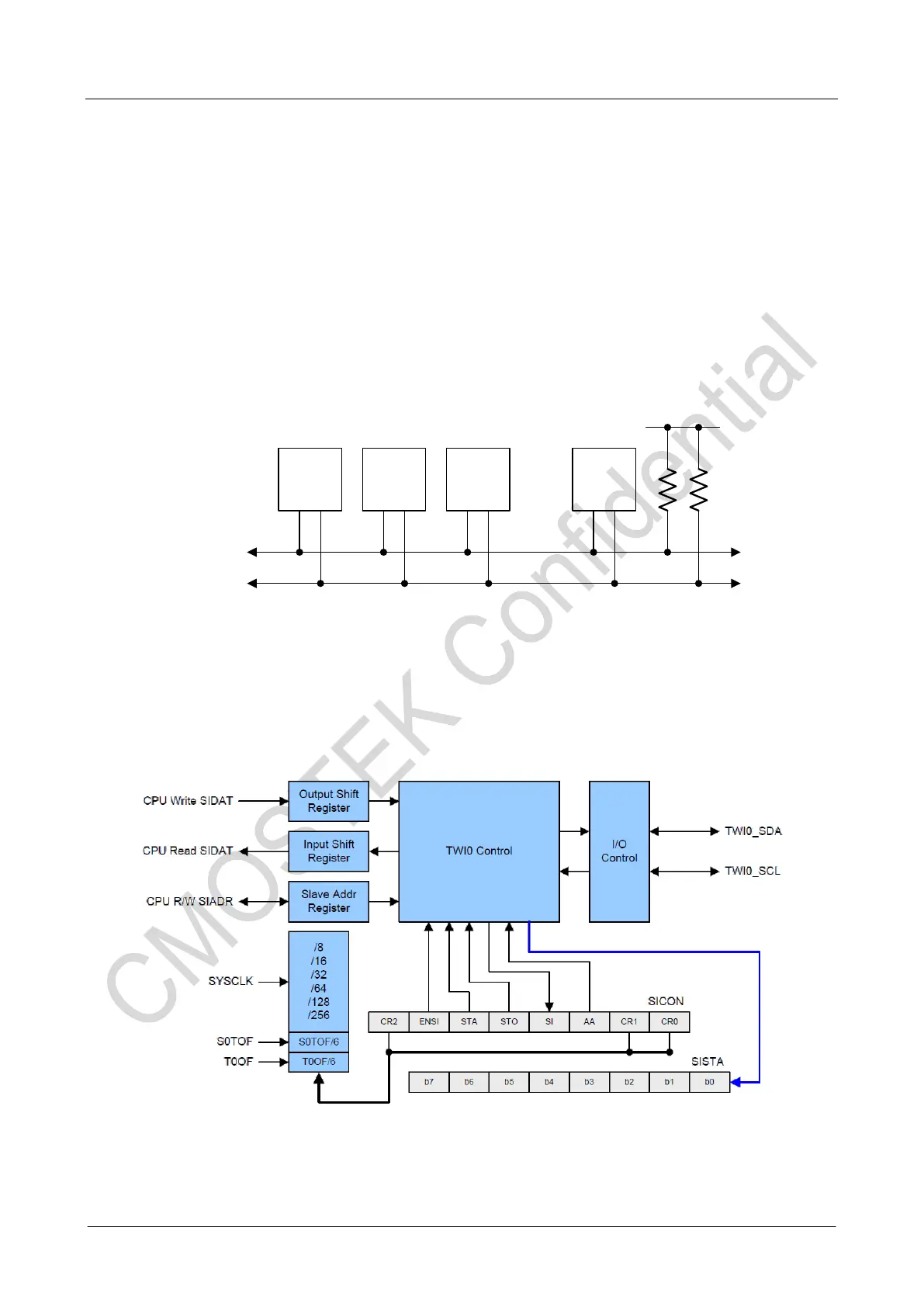

The TWI/ I2C bus may operate as a master and/or slave, and may function on a bus with multiple

masters. The CPU interfaces to the TWI/ I2C through the following four special function registers: SICON

configures the TWI/ I2C bus; SISTA reports the status code of the TWI/ I2C bus; and SIDAT is the data

register, used for both transmitting and receiving TWI/ I2C data. SIADR is the slave address register. And, the

TWI/ I2C hardware interfaces to the serial bus via two lines: SDA (serial data line) and SCL (serial clock line).

Figure 21-2. TWI/ I2C Block Diagram

21.1 Operating Modes

There are four operating modes for the TWI/ I2C:

Loading...

Loading...