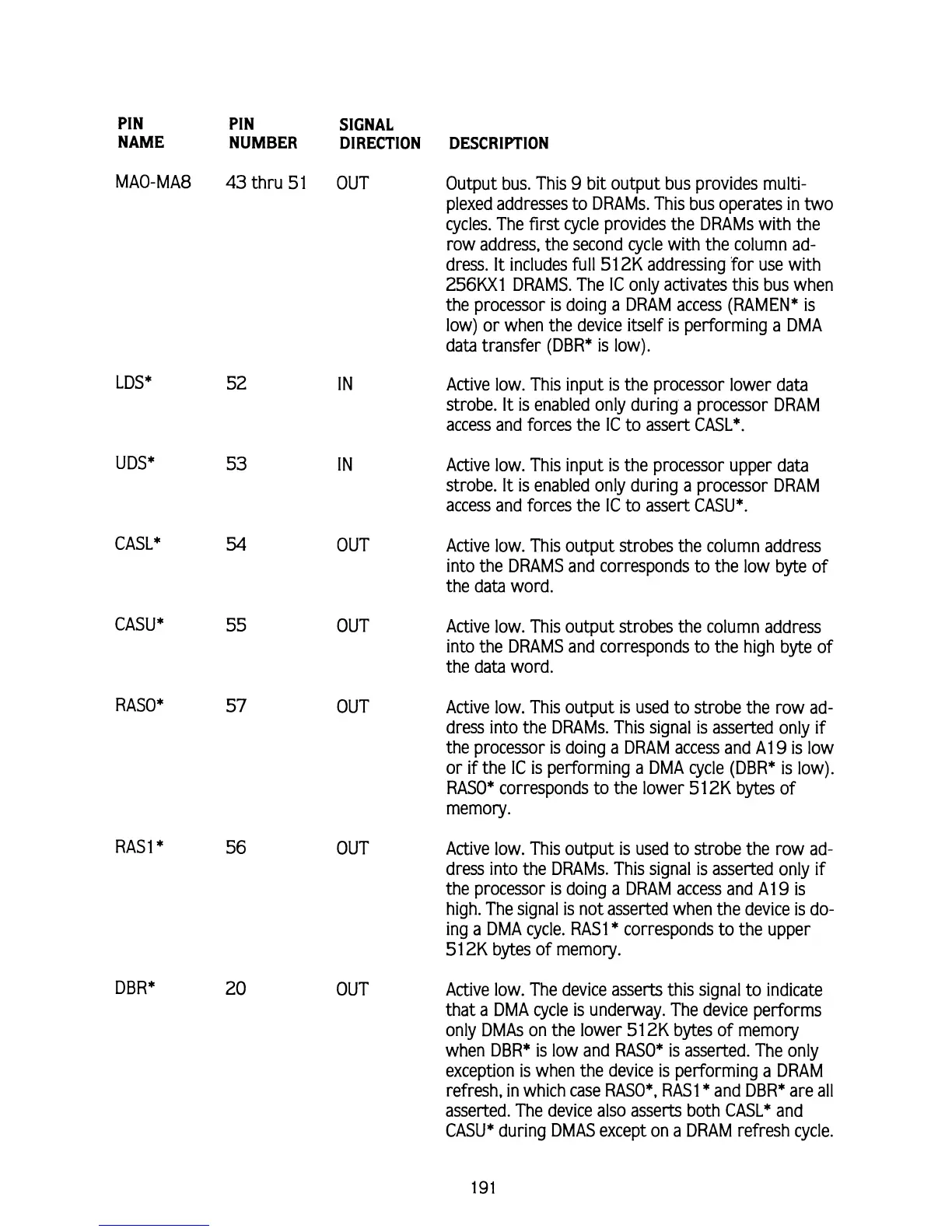

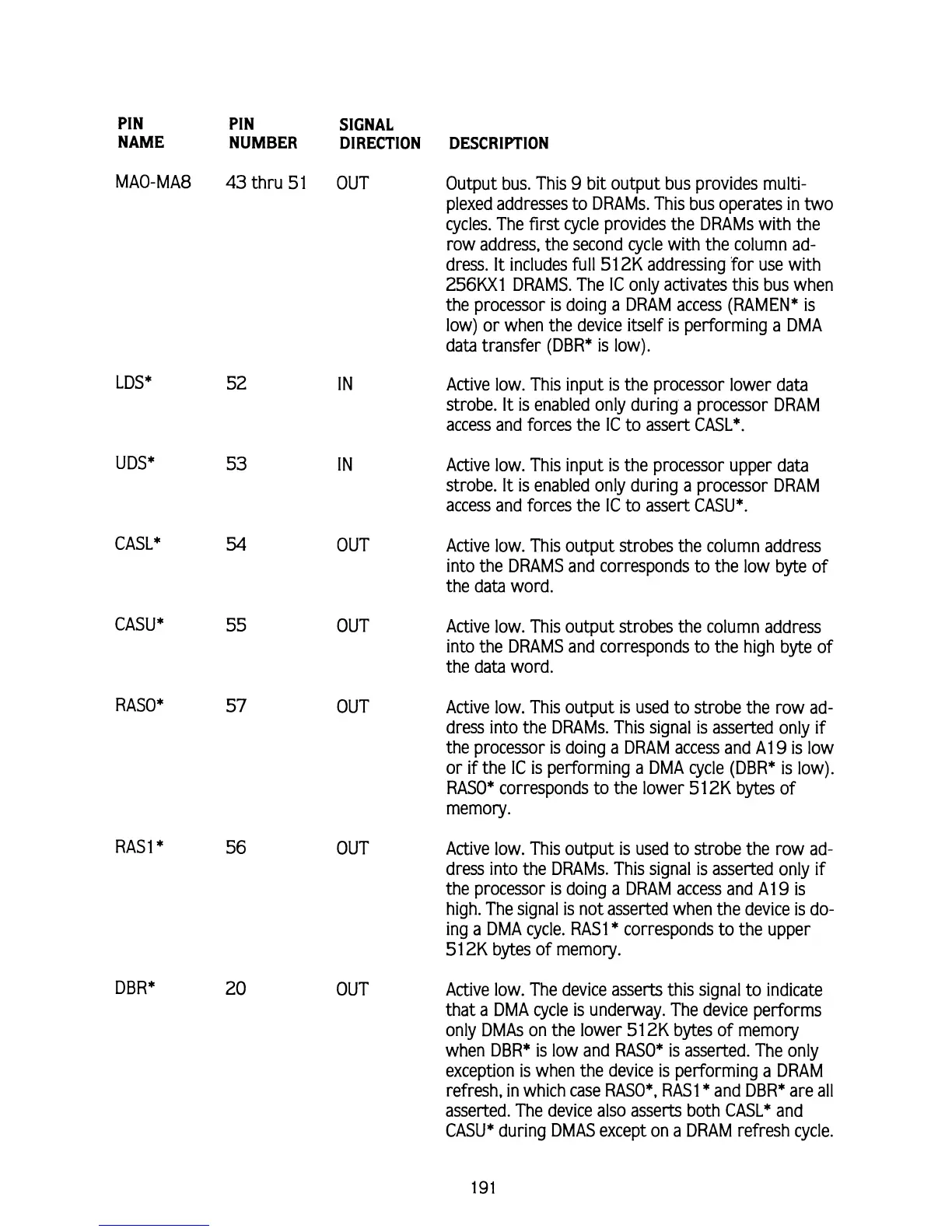

PIN PIN SIGNAL

NAME NUMBER DIRECTION DESCRIPTION

MAO-MA8

43

thru

5

1 OUT Output bus. This

9

bit output bus provides multi-

plexed addresses to DRAMs. This bus operates in two

cycles. The first cycle provides the DRAMs with the

row address, the second cycle with the column ad-

dress.

It

includes full 51 2K addressing for use with

256KX1 DRAMS. The IC only activates this bus when

the processor is doing a

DRAM

access (RAMEN* is

low) or when the device itself is performing a

DMA

data transfer

(DBR*

is low).

LDS* 52

IN

UDS*

53

IN

CASL*

54

OUT

CASU*

55

OUT

RASO*

57

OUT

RAS1

*

56

OUT

DBR*

20 OUT

Active low. This input is the processor lower data

strobe.

It

is enabled only during a processor

DRAM

access and forces the IC to assert CASL*.

Active low. This input is the processor upper data

strobe.

It

is enabled only during a processor DRAM

access and forces the

IC to assert CASU*.

Active low. This output strobes the column address

into the DRAMS and corresponds to the low byte of

the data word.

Active low. This output strobes the column address

into the DRAMS and corresponds to the high byte of

the data word.

Active low. This output is used to strobe the row ad-

dress into the DRAMs. This signal is asserted only if

the processor is doing a

DRAM

access and A1

9

is low

or if the

IC is performing a

DMA

cycle

(DBR*

is low).

RASO* corresponds to the lower 51 2K bytes of

memory.

Active low. This output is used to strobe the row ad-

dress into the DRAMs. This signal is asserted only if

the processor is doing a

DRAM

access and A1

9

is

high. The signal is not asserted when the device is do-

ing a

DMA

cycle. RASl

*

corresponds to the upper

51

2K bytes of memory.

Active low. The device asserts this signal to indicate

that a

DMA

cycle is underway. The device performs

only

DMAs

on

the lower 51 2K bytes of memory

when DBR* is low and RASO* is asserted. The only

exception is when the device is performing a

DRAM

refresh, in which case RASO*, RASl* and DBR* are all

asserted. The device also asserts both CASL* and

CASU* during DMAS except on a

DRAM

refresh cycle.

Loading...

Loading...