Force

Load

Input

Mode

TOD

A

strobe bit allows the timer latch to be loaded into the timer

counter at any time, whether the timer is running or not.

Control bits allow selection of the clock used to decrement the timer.

TIMER

A

can count 02 pulses or external pulses applied to the CNT

pin. TIMER

B

can count 02 pulses, external CNT pulses, TIMER

A

un-

derflow pulses or TIMER

A

underflow pulses while the CNT pin is

held high.

The timer latch is loaded into the timer on any timer underflow, on a

force load or following a write to the high byte of the prescaler while

the timer is stopped. If the timer is running, a write to the high byte

will load the timer latch, but not reload the counter.

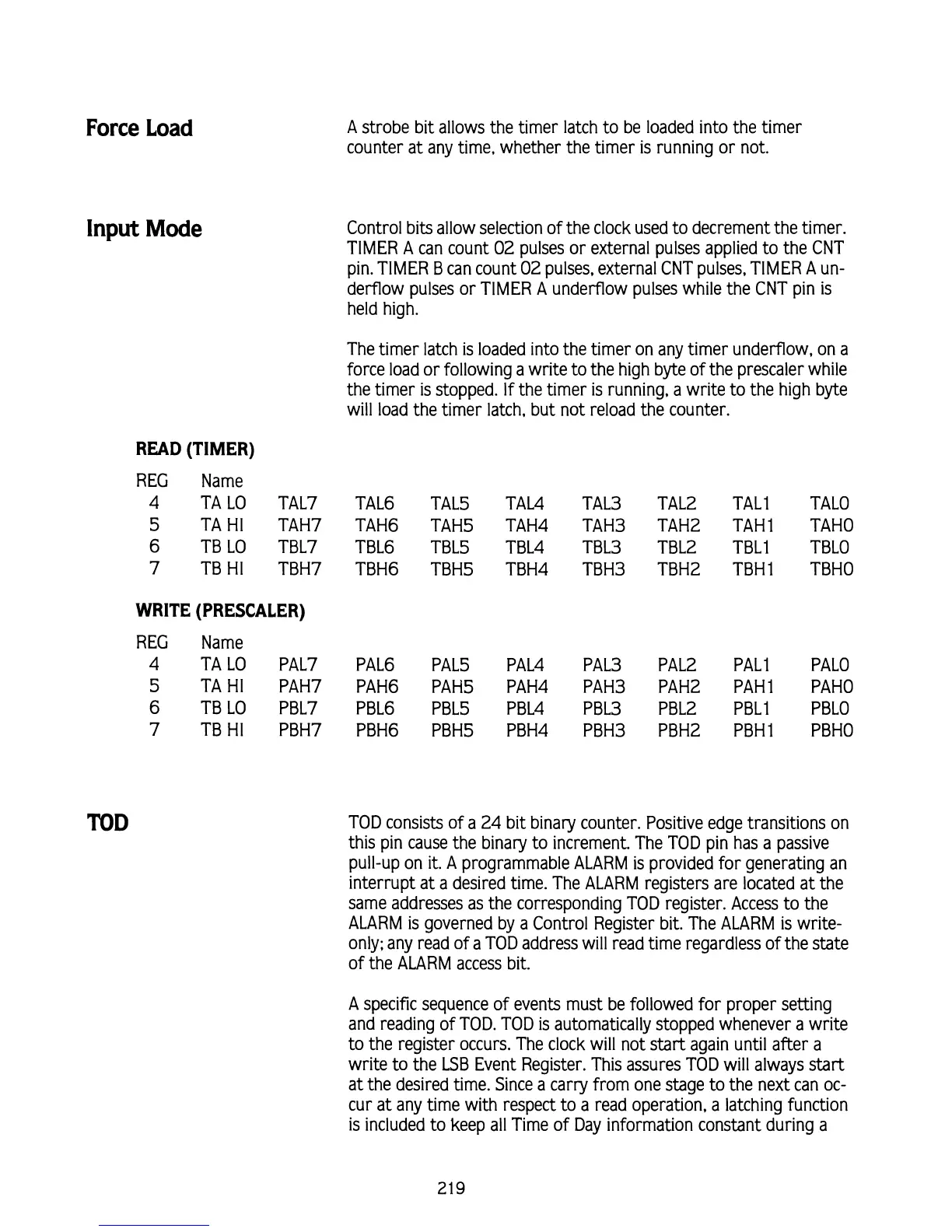

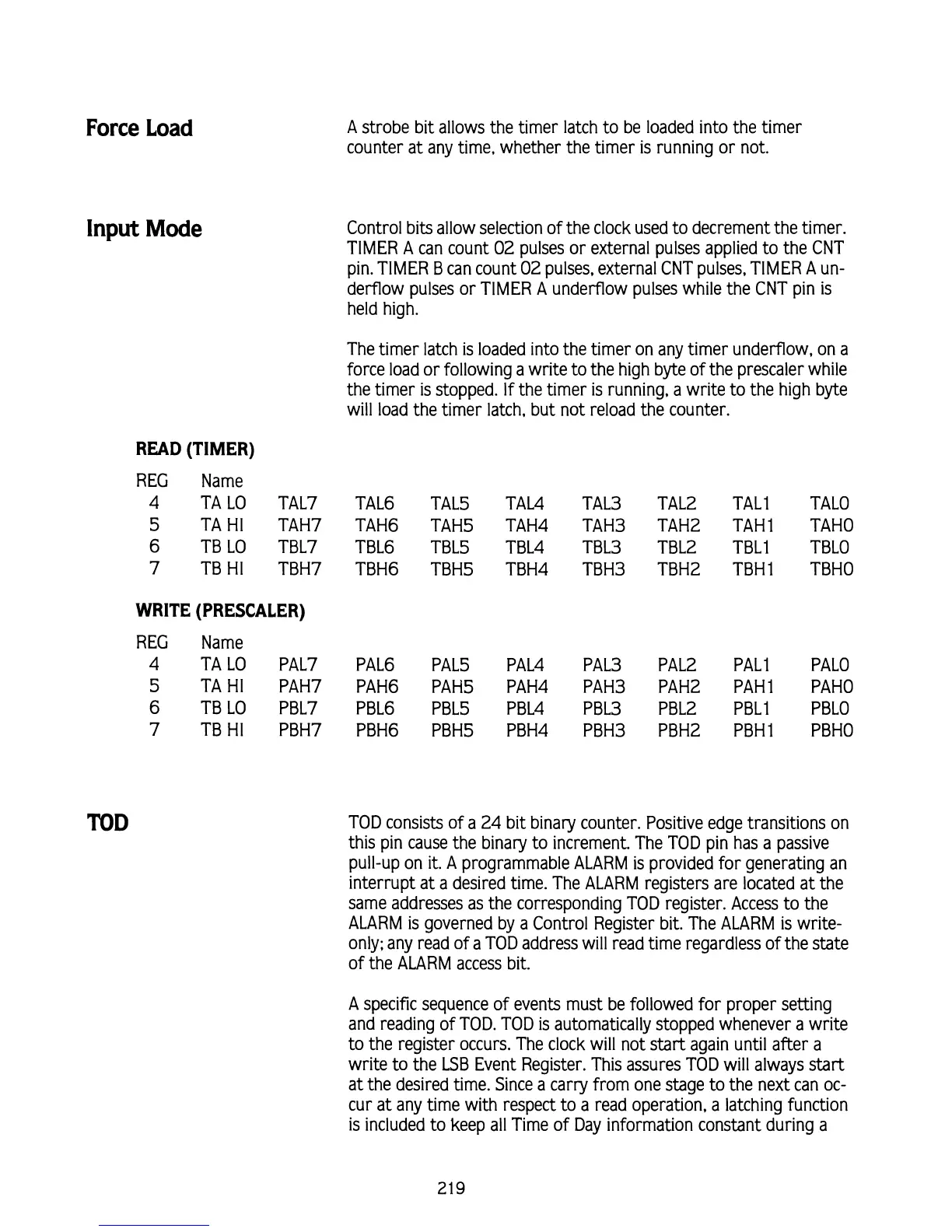

READ (TIMER)

REG Name

4 TA

L0

TA17

5

TAHI TAH7

6

TB

L0

TBL7

7

TB

HI

TBH7

WRITE (PRESCALER)

REG Name

4 TA

L0

PAL7

5

TA HI PAH7

6

TB

L0

PBL7

7

TB HI

PBH7

TA16

TA15 TA14

TAL3 TAL2

TAL1

TALO

TAH6 TAH5

TAH4

TAH3

TAH2

TAHl

TAHO

TBL6

TB15

TB14

TBL3 TBL2

TBLl

TBLO

TBH6

TBH5

TBH4

TBH3

TBH2

TBHl

TBHO

PAL6

PAL5

PAL4 PAL3

PAL2

PAL1

PAL0

PAH6 PAH5

PAH4

PAH3

PAH2

PAHl

PAHO

PBL6

PBL5

PBL4

PBL3

PBL2

PBLl

PBLO

PBH6

PBH5

PBH4

PBH3

PBH2

PBHl

PBHO

TOD consists of a 24 bit binary counter. Positive edge transitions on

this pin cause the binary to increment. The TOD pin has a passive

pull-up on it.

A

programmable

ALARM

is provided for generating an

interrupt at a desired time. The

ALARM

registers are located at the

same addresses as the corresponding TOD register. Access to the

ALARM

is governed by a Control Register bit. The

ALARM

is write-

only; any read of a TOD address will read time regardless of the state

of the

ALARM

access bit.

A

specific sequence of events must be followed for proper setting

and reading of

TOD. TOD is automatically stopped whenever a write

to the register occurs. The clock will not start again until after a

write to the LSB Event Register. This assures TOD will always start

at the desired time. Since a carry from one stage to the next can oc-

cur at any time with respect to

a

read operation, a latching function

is included to keep all Time of Day information constant during a

Loading...

Loading...