© DENAFRIPS CO. LTD. & VINSHINE AUDIO PTE. LTD. (SINGAPORE)

ALL RIGHTS RESERVED

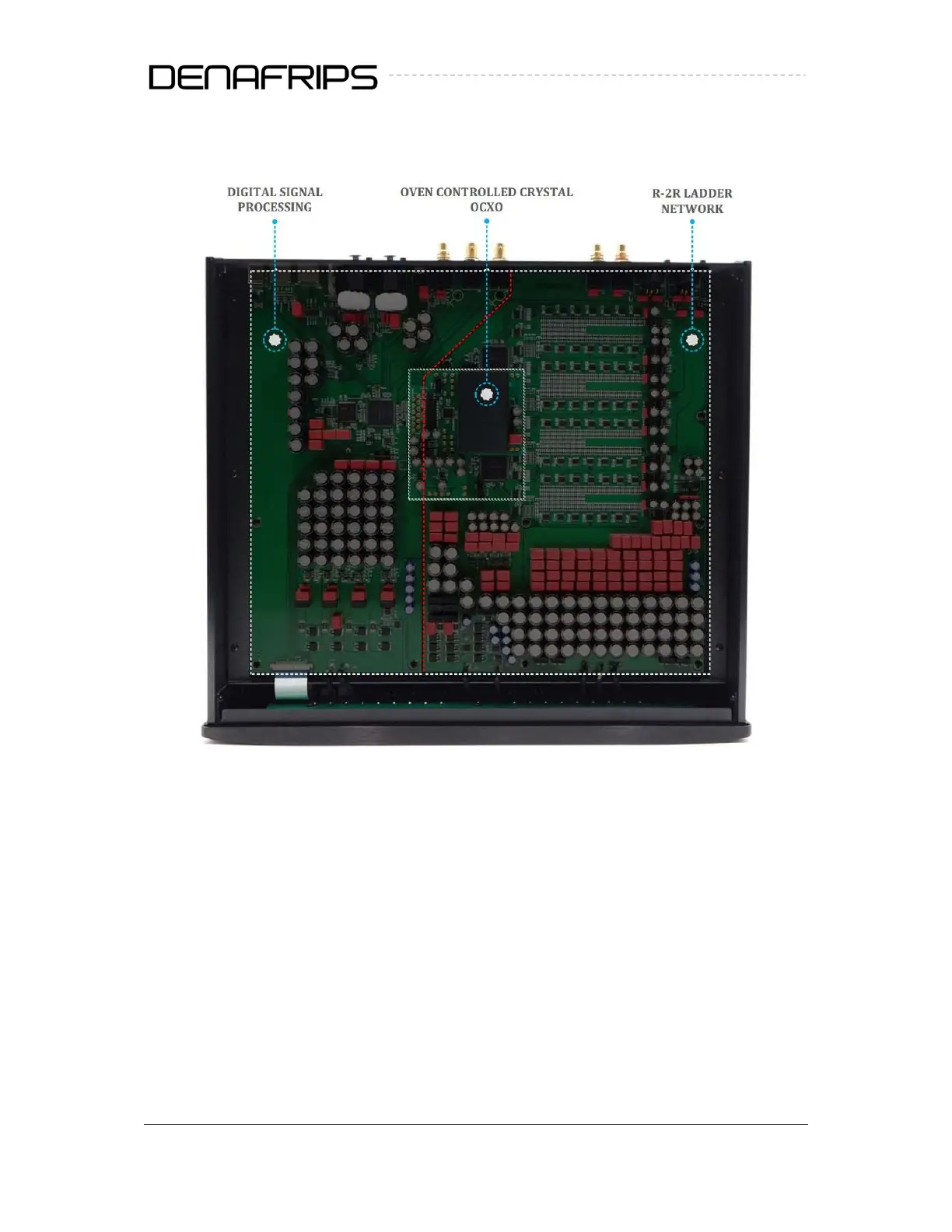

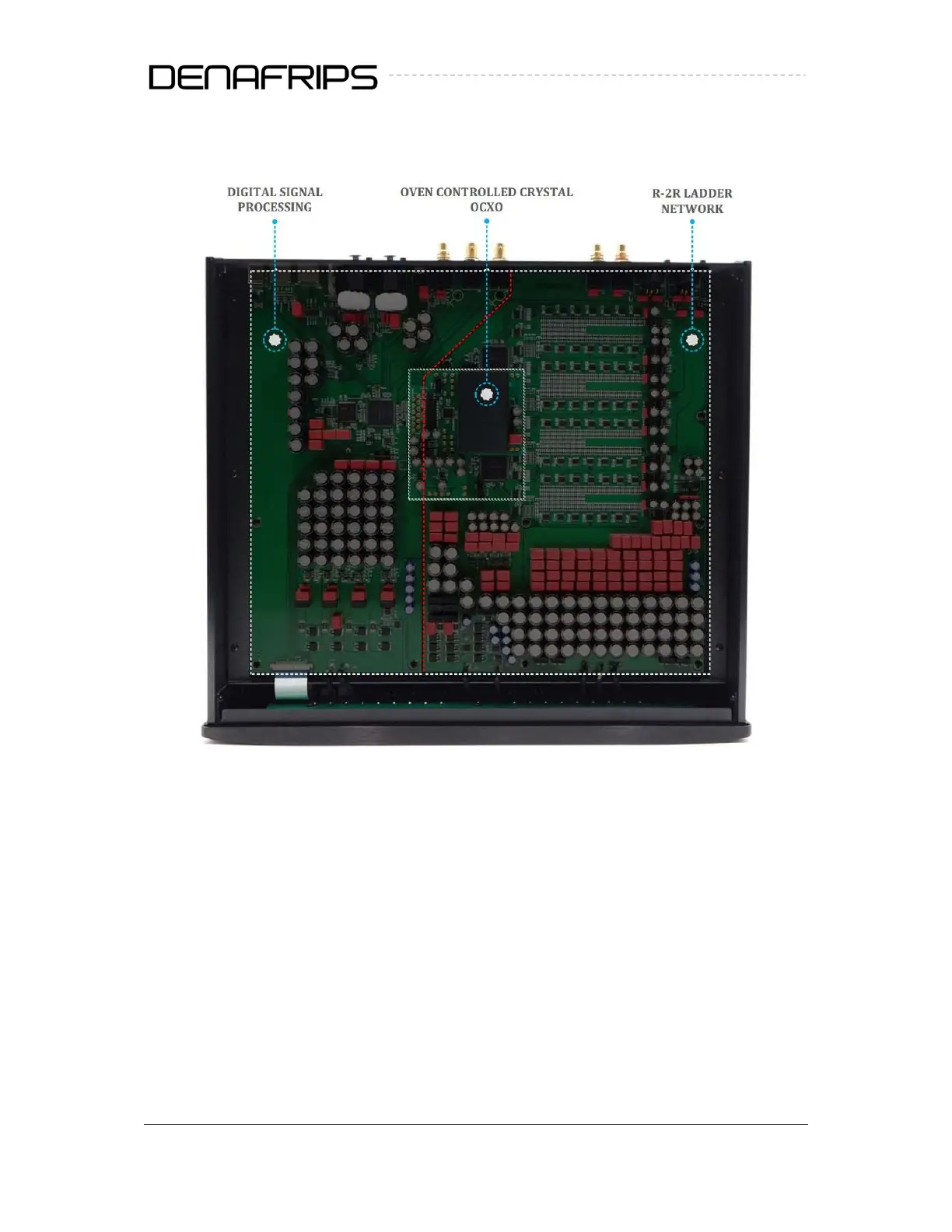

3.9 DAC ARCHITECTURE

DIGITAL SIGNAL PROCESSING – All digital input data are stored in the on-board FPGA high-

speed RAM.

OCXO – These data are read from the memory using the ultra-low phase noise, super

accurate OCXO, located right in the DAC. The processed data are sent to the final stage

Discrete R-2R for DA conversion.

R-2R LADDER NETWORK – The data bits are converted to analogue signal by the true

balanced R-2R ladder network arrays. The linearity of the conversion is guaranteed by the

high-precision thin film resistors, with low thermal effect temperature coefficient of the low

10/15ppm.

Loading...

Loading...