SERVICE MANUAL

¾ CGMS, Teletext, WSS, VPS and close caption

• On-Chip Peripherals

¾ 4 ASCs (UARTS)

¾ 4 parallel 8-bit I/O banks

¾ 2 smartcard interfaces and clock generators

¾ 3 SSCs for I²C/SPI master/slave interfaces

¾ Silicon Labs line side (DAA) interface

¾ High-speed USB OHCI/EHCI compliant host interface

¾ DiSEqC interface

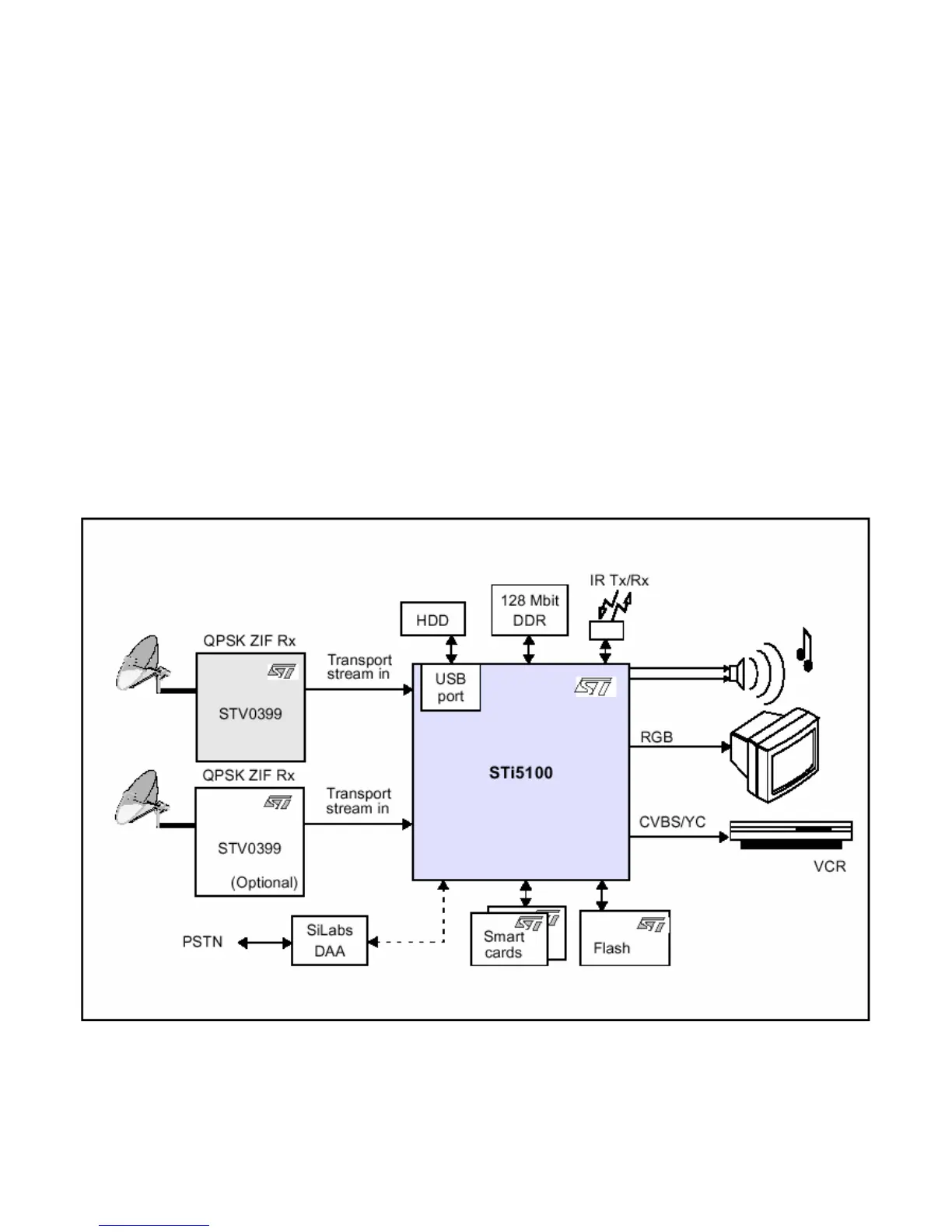

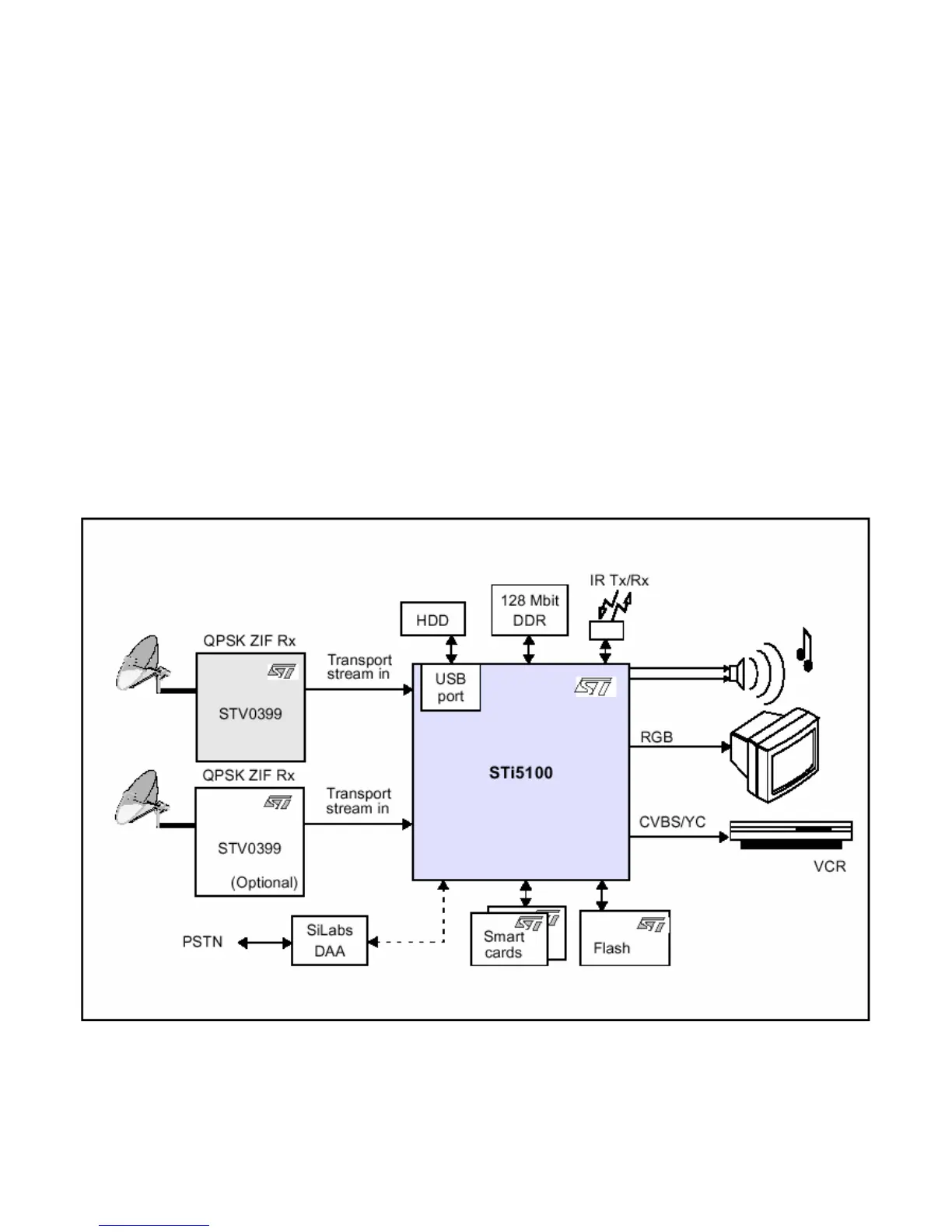

3. Architecture overview

The figure below shows the architecture of the Sti5100.

This chapter gives a brief overview of each of the functional blocks of the STi5100.

4. STi5100 functional modules

4.1 Memory subsystem

Page 6

Loading...

Loading...