Deskstar T7K500 Hard Disk Drive Specification

31

• In the event that a host reads the status register only before the sector or block transfer DRQ interval, the

DRQ interval 4.2 µs

• In the event that a host reads the status register after or both before and after the sector or block transfer,

the DRQ interval is 11.5 µs

6.8 Multi-word DMA timings

The Multiword DMA timings meet Mode 2 of the ATA/ATAPI-6 description.

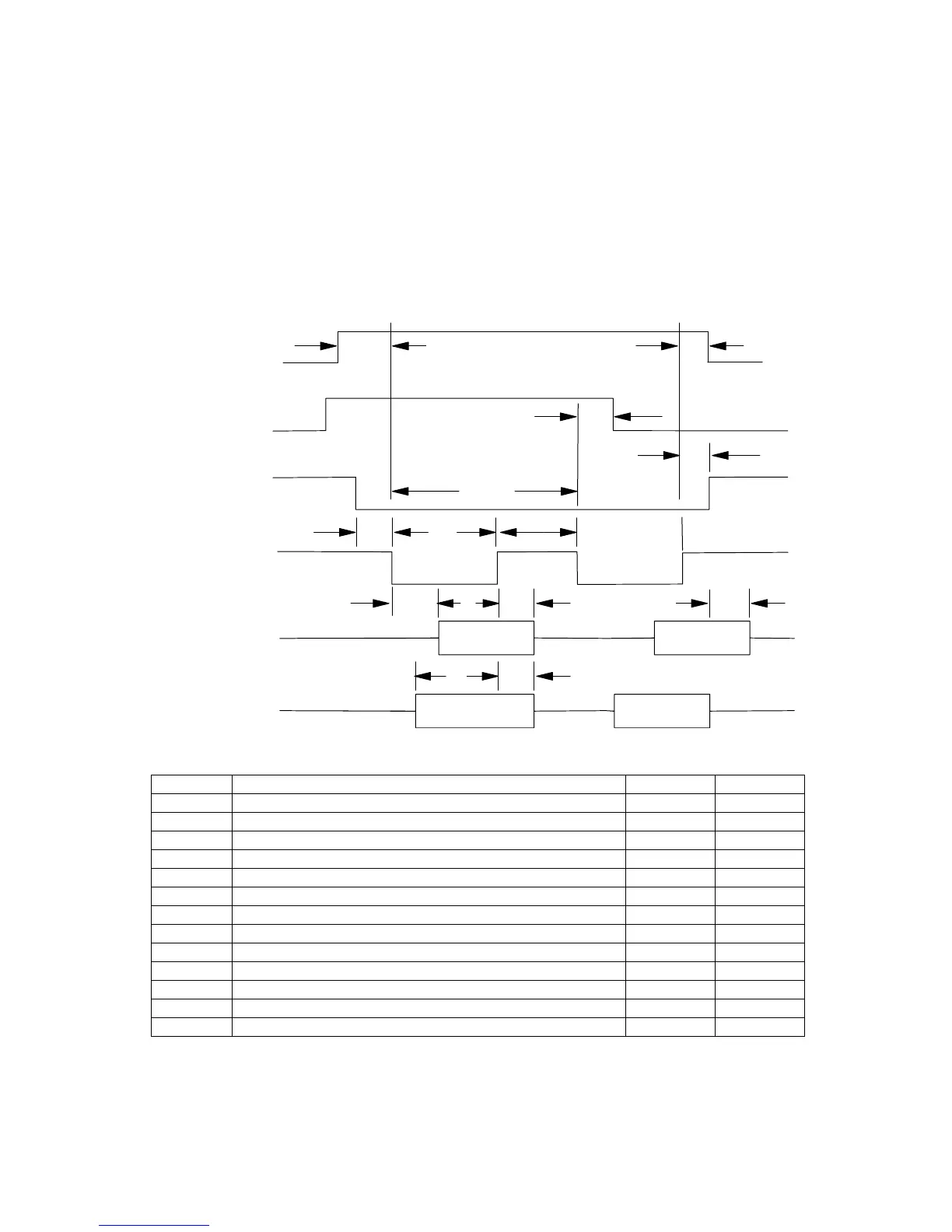

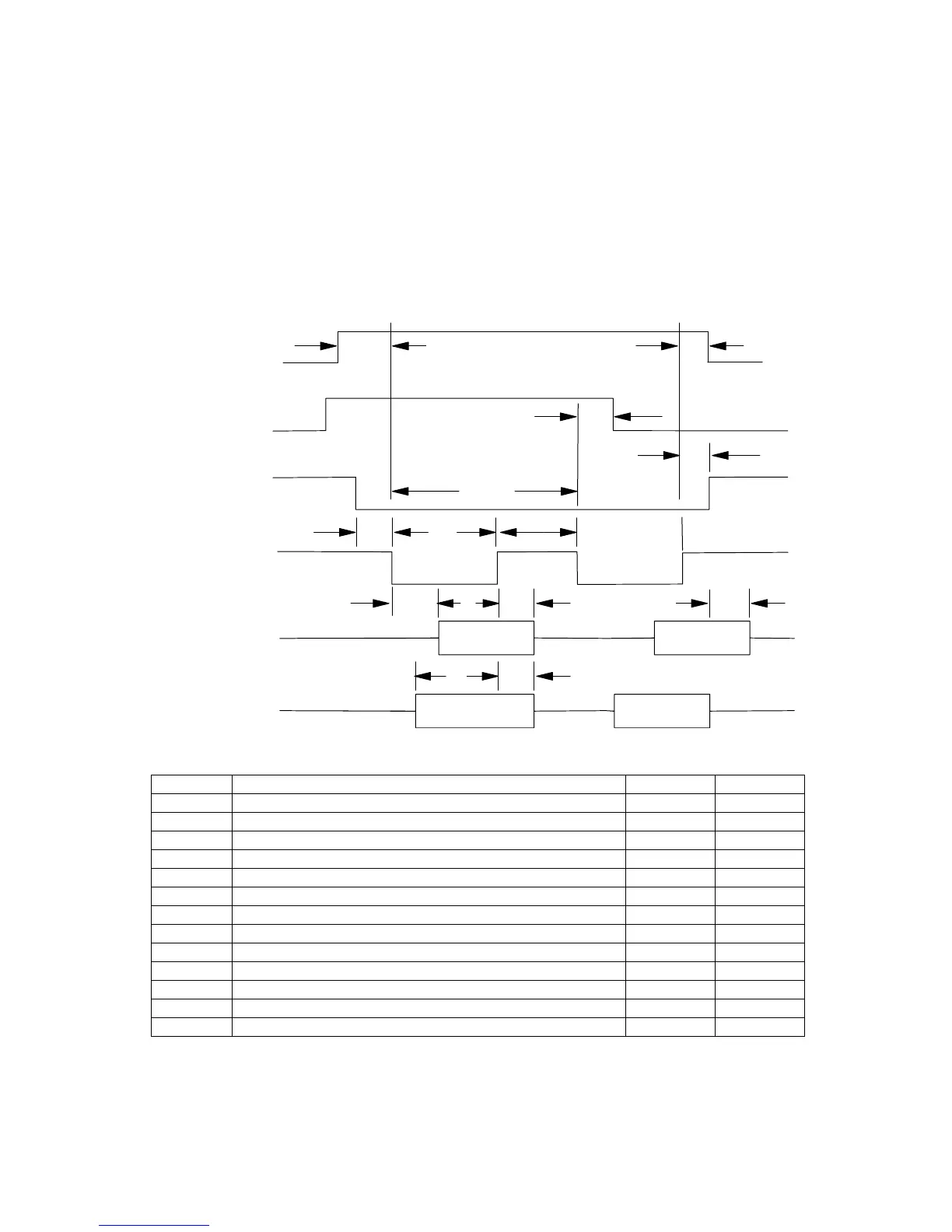

Table 18: Multiword DMA cycle timing chart

Table 19: Multiword DMA cycle timings

PARAMETER DESCRIPTION

MIN (ns) MAX (ns)

t0 Cycle time

120 –

tD DIOR-/DIOW- asserted pulse width

70 –

tE DIOR- data access

–50

tF DIOR- data hold

5–

tG DIOR-/DIOW- data setup

20 –

tH DIOW- data hold

10 –

tI DMACK- to -DIOR-/DIOW- setup

0–

tJ DIOR-/DIOW- to DMACK- hold

5–

tKR/tKW DIOR-/DIOW- negated pulse width

25 –

tLR/tLW DIOR-/DIOW- to DMARQ- delay

–35

tM CS (1:0) valid to DIOR-/DIOW-

25 -

tN CS (1:0)

10 -

tZ DMACK- to read data released

–25

WRITE DATA

READ DATA

DMACK-

DMARQ

DIOR-/DIOW-

t0

tLR/tLW

tJ

tI

tD

tKR/tKW

tF

tG

tH

tG

tZ

CS0-/CS1-

tM

tN

tE

Loading...

Loading...