106 IBM BladeCenter PS700, PS701, and PS702 Technical Overview and Introduction

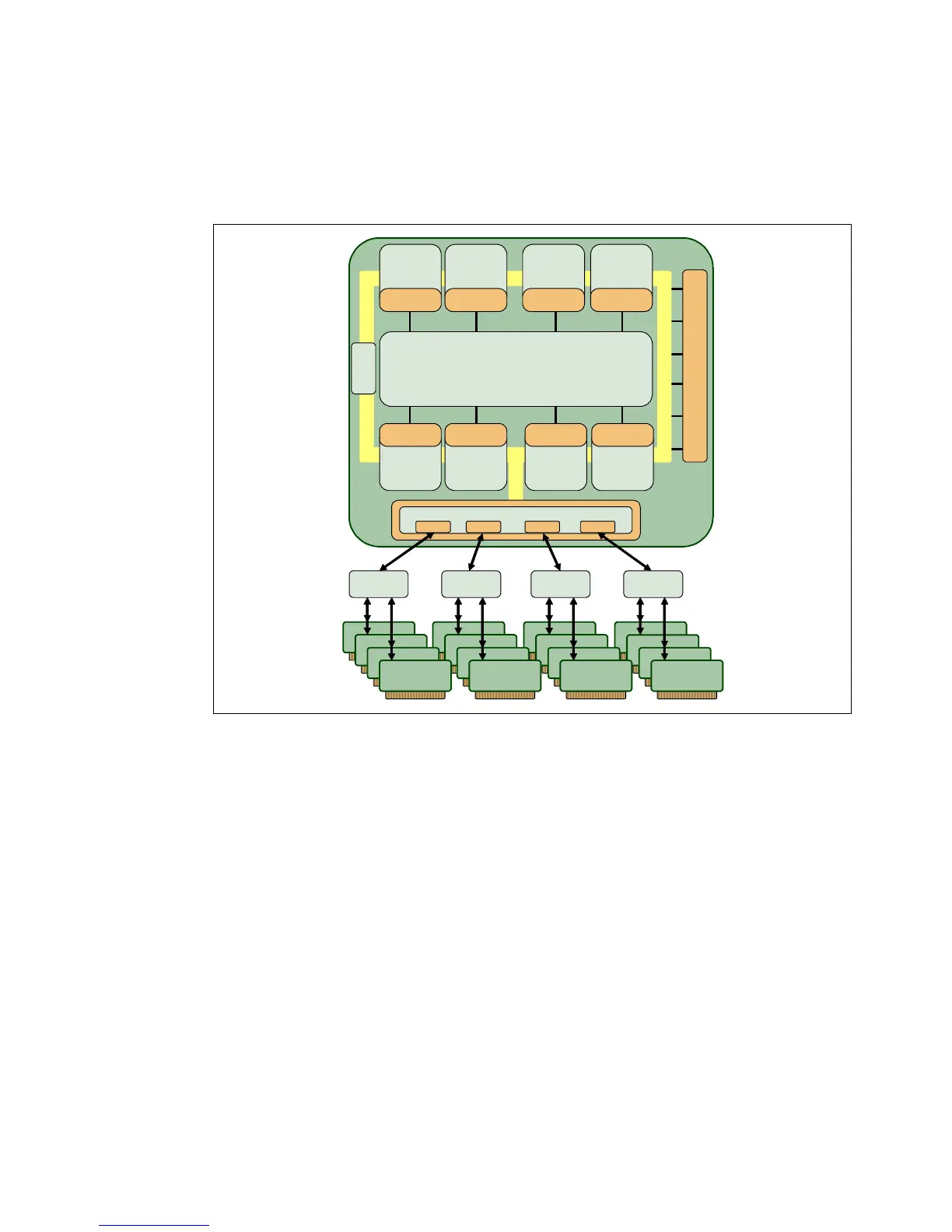

Figure 4-1 shows a POWER7 chip as implemented on a PS701 blade with its memory

interface comprised of one controller and four advanced memory buffers. Advanced memory

buffer chips are exclusive to IBM. They help to increase performance acting as read/write

buffers. The four advanced memory buffer chips are on the system planar and support four

DIMMs each.

Figure 4-1 PS701 memory subsystem

Memory page deallocation

Although coincident cell errors in separate memory chips are a statistical rarity, IBM POWER

processor-based systems can contain these errors using a memory page deallocation

scheme for partitions running IBM AIX and the IBM i operating systems, as well as for

memory pages owned by the POWER Hypervisor. If a memory address experiences an

uncorrectable or repeated correctable single cell error, the service processor sends the

memory page address to the POWER Hypervisor to be marked for deallocation. Pages used

by the POWER Hypervisor are deallocated as soon as the page is released.

In other cases, the POWER Hypervisor notifies the owning partition that the page should be

deallocated. Where possible, the operating system moves any data currently contained in that

memory area to another memory area and removes the page (or pages) associated with this

error from its memory map, no longer addressing these pages. The operating system

performs memory page deallocation without any user intervention and is transparent to users

and applications.

The POWER Hypervisor maintains a list of pages marked for deallocation during the current

platform IPL. During a partition IPL, the partition receives a list of all the bad pages in its

address space. In addition, if memory is dynamically added to a partition (through a dynamic

LPAR operation), the POWER Hypervisor warns the operating system when memory pages

are included that need to be deallocated.

GX

POWER7

Core

256 KB L2

POWER7

Core

256 KB L2

POWER7

Core

256 KB L2

POWER7

Core

256 KB L2

POWER7

Core

256 KB L2

32 MB L3 Cache

Memory Controller

SMP Fabric

Port Port Port Port

Memory

Buffer

Memory

Buffer

Memory

Buffer

POWER7

Core

256 KB L2

POWER7

Core

256 KB L2

POWER7

Core

256 KB L2

DDR3

DIMM

DDR3

DIMM

DDR3

DIMM

DDR3

DIMM

Memory

Buffer

Loading...

Loading...