17: USER COMMUNICATION INSTRUCTIONS

17-20 « FC4A MICROSMART USER’S MANUAL »

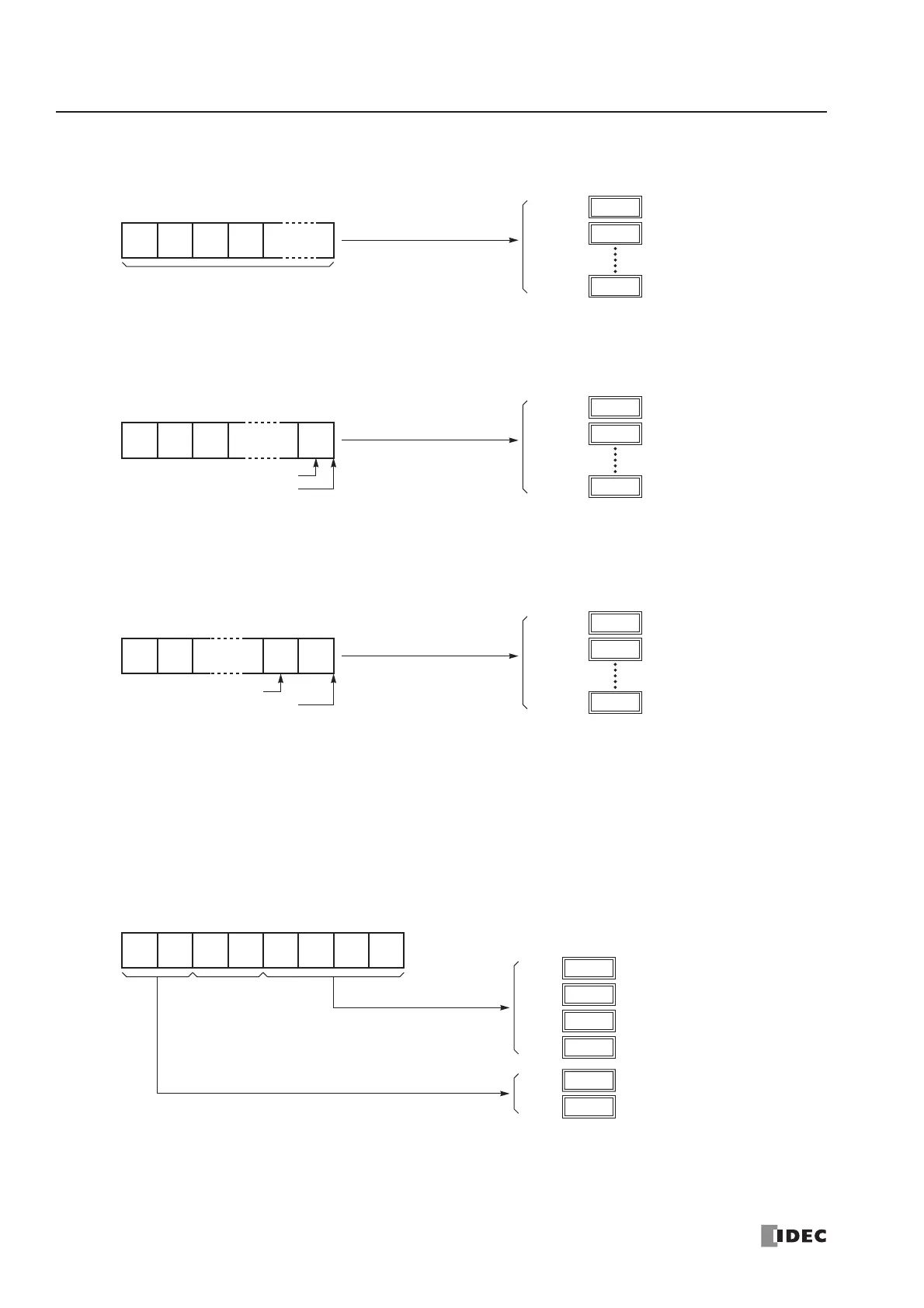

Example:

(1) When a RXD instruction without an end delimiter is executed

(2) When a RXD instruction with end delimiter ETX (03h) and without BCC is executed

(3) When a RXD instruction with end delimiter ETX (03h) and one-byte BCC is executed

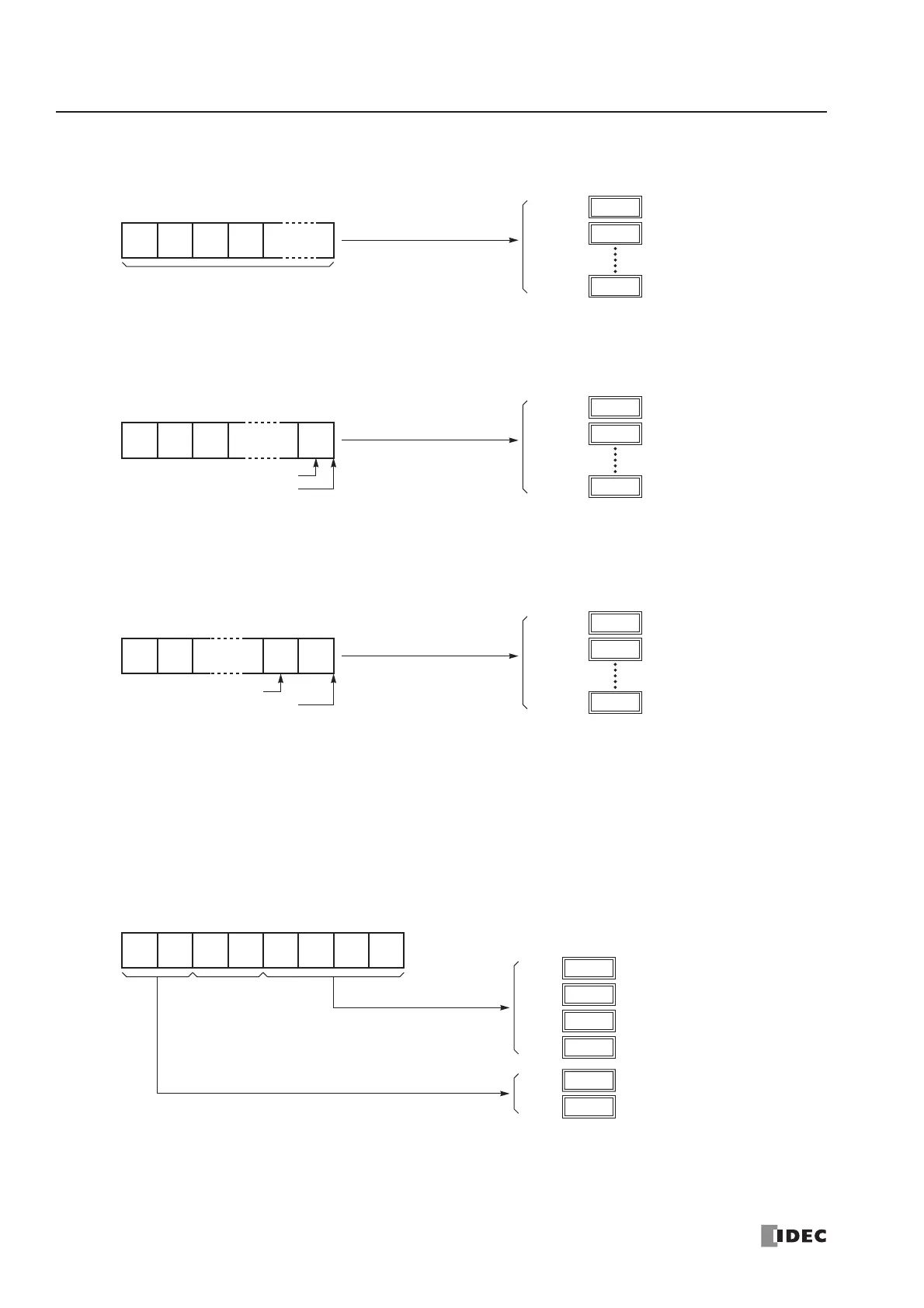

Skip

When “skip” is designated in the receive format, a specified quantity of digits in the incoming data are skipped and not

stored to data registers. A maximum of 99 digits (bytes) of characters can be skipped continuously.

Example: When a RXD instruction with skip for 2 digits starting at the third byte is executed

****

h

D100

When D100 is designated

“0”

(30h)

“1”

(31h)

Total of received characters

“2”

(32h)

“3”

(33h)

Incoming data

****

h

D100+n

****

h

D101

The incoming data is divided, converted, and stored to data registers according to the receive format.

Receive operation is completed when the total characters programmed in RXD are received.

as the first data register

****

h

D100

When D100 is designated

ETX

(03h)

“1”

(31h)

End delimiter

“2”

(32h)

“3”

(33h)

Incoming data

****

h

D100+n

****

h

D101

The incoming data is divided, converted, and stored to data registers according to the receive format.

The end delimiter is not stored to a data register.

Any data arriving after the end delimiter is discarded.

as the first data register

End of receiving data

****

h

D100

When D100 is designated

ETX

(03h)

“1”

(31h)

End delimiter

“2”

(32h)

BCC

Code

Incoming data

****

h

D100+n

****

h

D101

The incoming data is divided, converted, and stored to data registers according to the receive format.

The end delimiter and BCC code are not stored to data registers.

After receiving the end delimiter, the MicroSmart receives only the one-byte BCC code.

as the first data register

End of receiving data

0035h

D102

“1”

(31h)

“2”

(32h)

Skipped

“3”

(33h)

“4”

(34h)

Incoming Data

0038h

D105

0036h

D103

“5”

(35h)

“6”

(36h)

“7”

(37h)

“8”

(38h)

0031h

D100

0032h

D101

0037h

D104

When D100 is designated

as the first data register

Loading...

Loading...