MEMORY INTERFACING

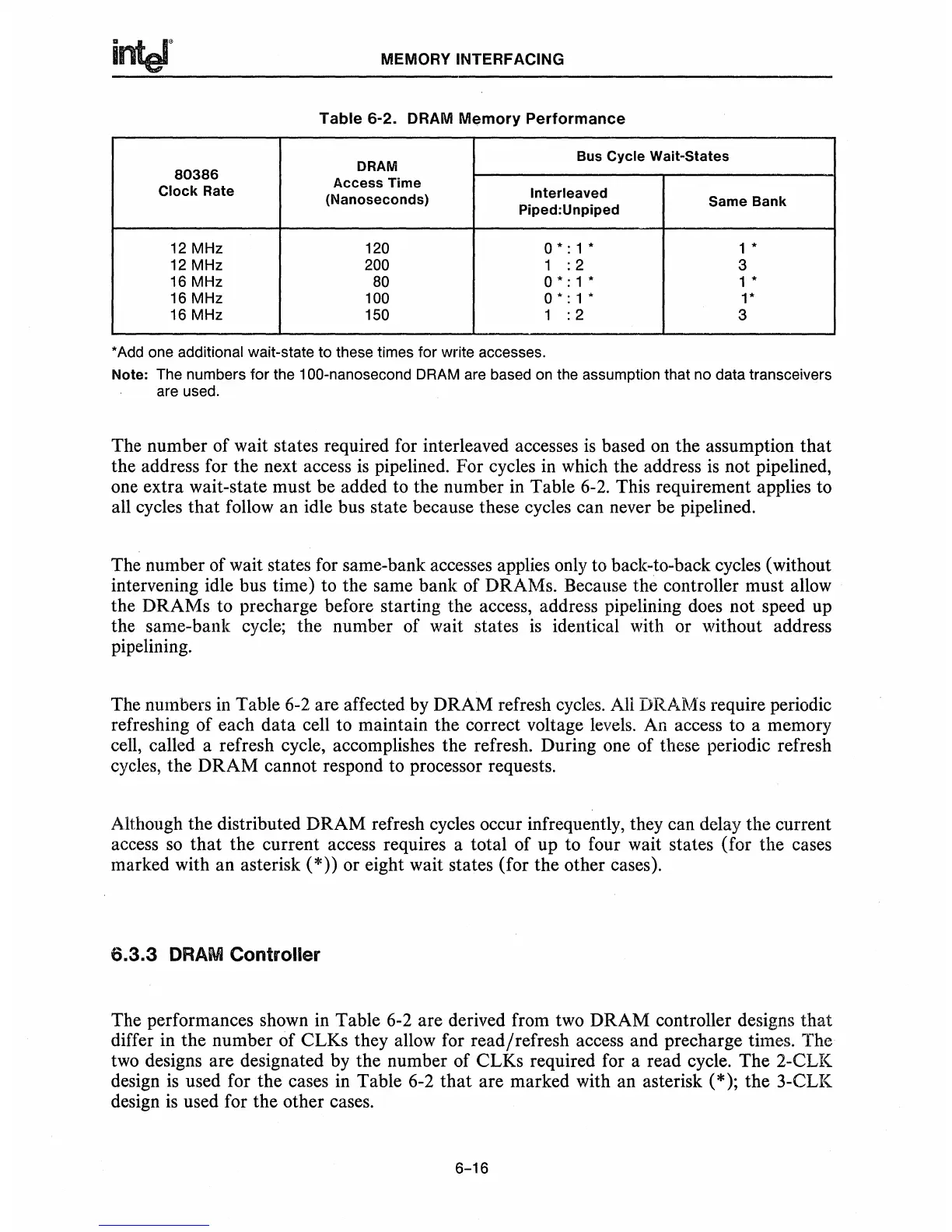

Table

6-2. DRAM

Memory

Performance

DRAM

Bus

Cycle Wait-States

80386

Access Time

Clock Rate

(Nanoseconds)

Interleaved

Same

Bank

Piped:Unpiped

12 MHz 120

0'

: 1 '

1 '

12 MHz 200

1

:2

3

16 MHz

80

0'

: 1 '

1 '

16 MHz 100

o • : 1 '

l'

16 MHz 150

1

:2

3

'Add one additional wait-state to these times for write accesses.

Note: The numbers

for

the 100-nanosecond DRAM are based on the assumption that no data transceivers

are used.

The number of wait states required for interleaved accesses

is

based

on

the assumption

that

the address for the next access

is

pipelined. For cycles in which the address

is

not pipelined,

one extra wait-state must be added to the number in Table 6-2. This requirement applies to

all cycles

that

follow an idle bus state because these cycles can never be pipelined.

The number of wait states for same-bank accesses applies only to back-to-back cycles (without

intervening idle bus time) to the same bank of DRAMs. Because the controller must allow

the DRAMs to precharge before starting the access, address pipelining does not speed up

the same-bank cycle; the number of wait states

is

identical with or without address

pipelining.

The numbers

in

Table 6-2 are affected by DRAM refresh cycles. All DRAMs require periodic

refreshing of each data cell to maintain the correct voltage

levels.

An access to a memory

cell, called a refresh cycle, accomplishes the refresh. During one of these periodic refresh

cycles, the

DRAM

cannot respond to processor requests.

Although the distributed DRAM refresh cycles occur infrequently, they can delay the current

access

so

that

the current access requires a total of up to four wait states (for the cases

marked with an asterisk (*» or eight wait states (for the other cases).

6.3.3

DRAM

Controller

The performances shown in Table 6-2 are derived from two DRAM controller designs

that

differ in the number of CLKs they allow for read/refresh access and precharge times. The

two designs are designated by the number of CLKs required for a read cycle. The 2-CLK

design

is

used for the cases in Table 6-2

that

are marked with an asterisk (*); the 3-CLK

design

is

used for the other cases.

6-16

Loading...

Loading...