CACHE SUBSYSTEMS

• In a power failure, the data in the cache

is

lost,

so

there

is

no

way to tell which locations

of the main memory contain stale data. Therefore, the main memory

as

well

as

the cache

must be considered volatile and provisions must be made to save the data in the cache in

the case of a power failure.

7.3.4 Cache Coherency

Write-through and write-back eliminate stale data in the main memory caused by cache

write operations. However, if caches are used in a system in which more than one device has

access to the main memory (multi-processing systems or

DMA

systems, for example), another

stale data problem

is

introduced.

If

new

data

is

written to main memory by one device, the

cache maintained by another device will contain stale data. A system

that

prevents the stale

cache data problem

is

said to maintain cache coherency. Four cache coherency approaches

are described below:

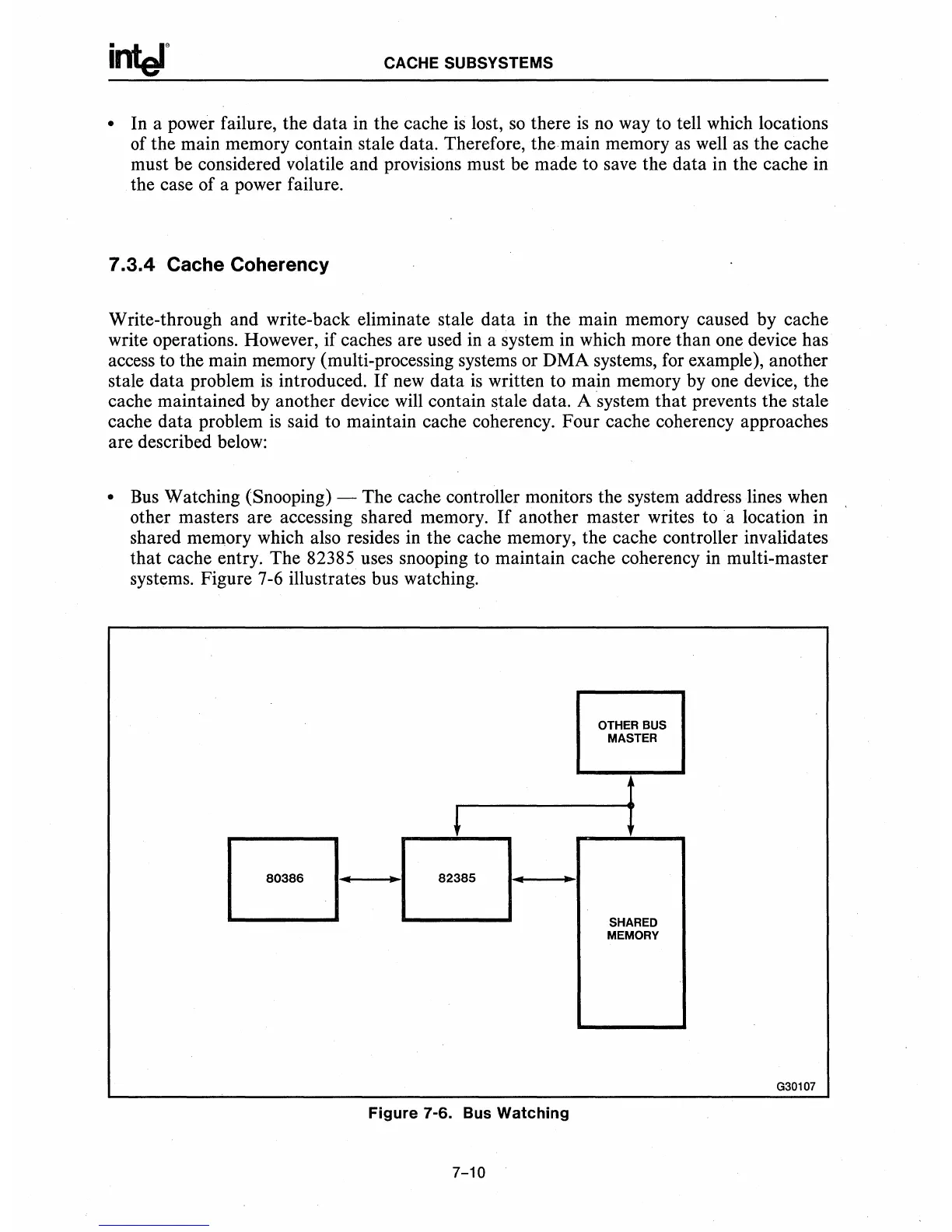

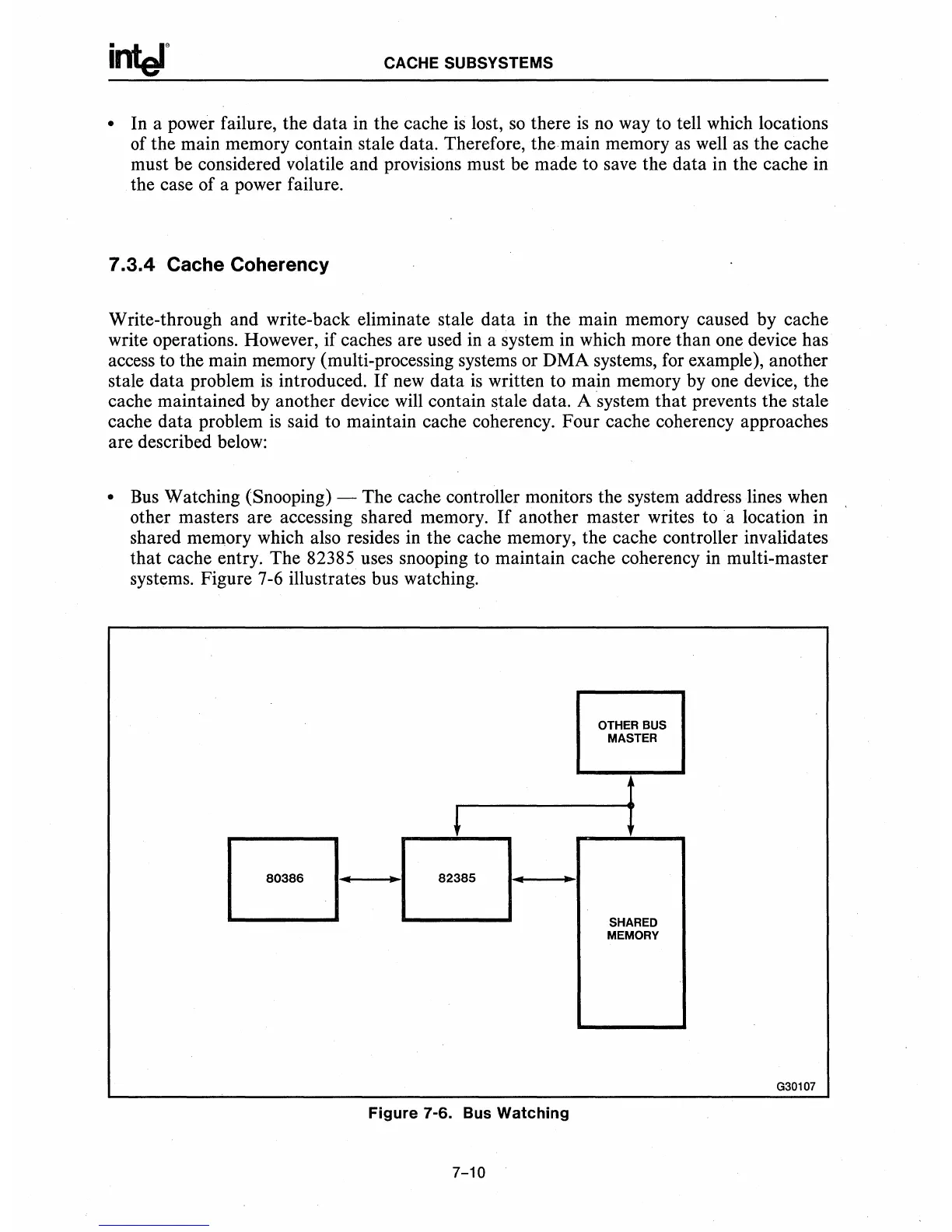

•

Bus

Watching (Snooping) - The cache controller monitors the system address lines when

other masters are accessing shared memory.

If

another master writes to a location in

shared memory which also resides in the cache memory, the cache controller invalidates

that cache entry. The 82385 uses snooping to maintain cache coherency in multi-master

systems. Figure 7-6 illustrates bus watching.

Figure

7-6. Bus

Watching

7-10

OTHER BUS

MASTER

I

SHARED

MEMORY

G30107

Loading...

Loading...