CACHE SUBSYSTEMS

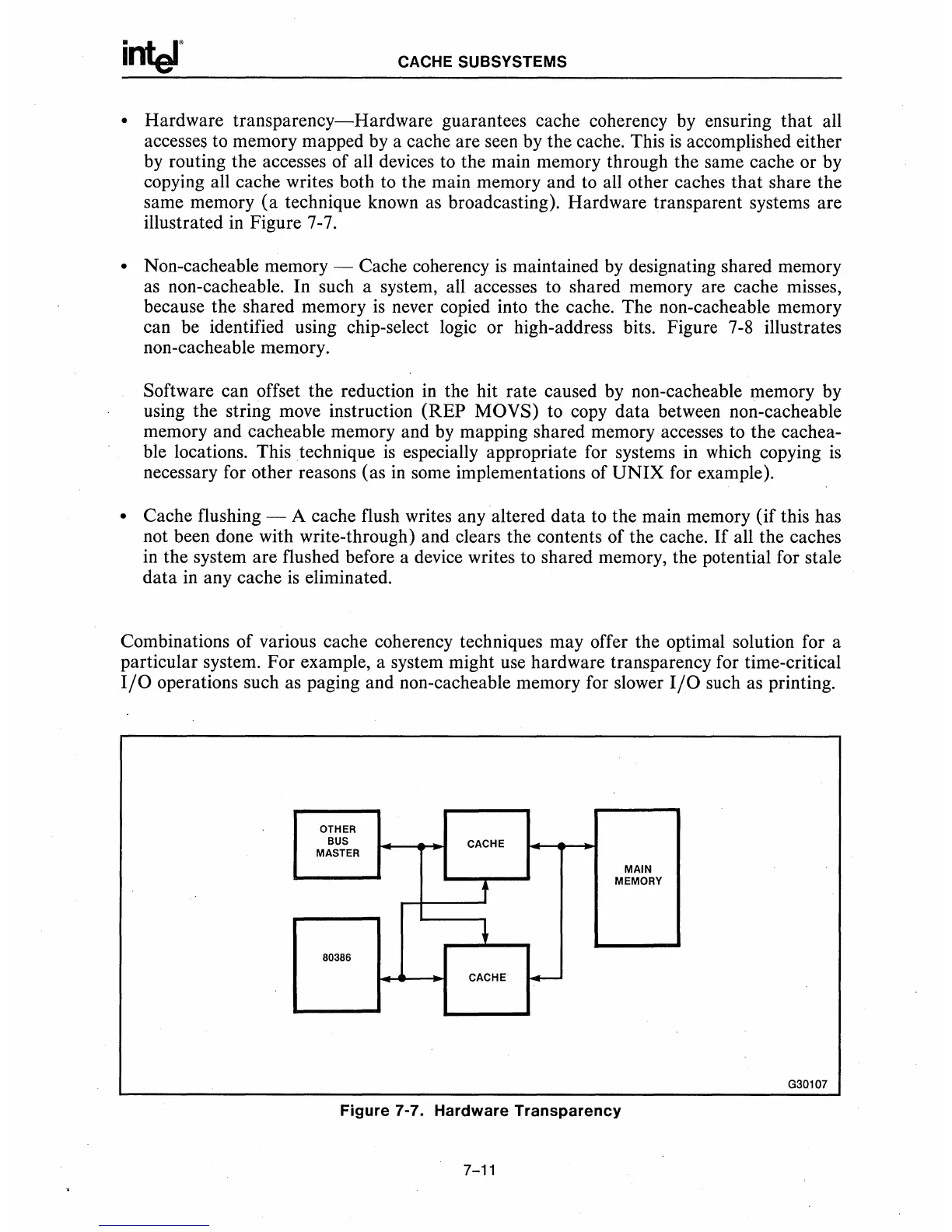

• Hardware

transparency-Hardware

guarantees cache coherency by ensuring

that

all

accesses to memory mapped by a cache are seen by the cache. This

is

accomplished either

by routing the accesses of all devices to the main memory through the same cache or by

copying all cache writes both to the main memory and to all other caches

that

share the

same memory

(a

technique known as broadcasting). Hardware transparent systems are

illustrated

in

Figure 7-7.

• Non-cacheable memory - Cache coherency

is

maintained

by

designating shared memory

as

non-cacheable. In such a system, all accesses to shared memory are cache misses,

because the shared memory

is

never copied into the cache. The non-cacheable memory

can be identified using chip-select logic or high-address bits. Figure

7-8

illustrates

non-cacheable memory.

Software can offset the reduction in the hit rate caused by non-cacheable memory by

using the string move instruction

(REP

MOVS) to copy data between non-cacheable

memory and cache able memory and by mapping shared memory accesses to the cachea-

ble locations. This technique

is

especially appropriate for systems in which copying

is

necessary for other reasons (as in some implementations of

UNIX

for example).

• Cache flushing - A cache flush writes any altered data to the main memory (if this has

not been done with write-through) and clears the contents of the cache.

If

all the caches

in the system are flushed before a device writes to shared memory, the potential for stale

data in any cache

is

eliminated.

Combinations of various cache coherency techniques may offer the optimal solution for a

particular system. For example, a system might use hardware transparency for time-critical

I/O

operations such as paging and non-cacheable memory for slower

I/O

such

as

printing.

OTHER

BUS

CACHE

MASTER

MAIN

t

MEMORY

,

80386

CACHE

I-

G30107

Figure

7-7.

Hardware Transparency

7-11

Loading...

Loading...