1/0

INTERFACING

...

II

BYTE ENABLES

~

AOIA1

LOGIC

...

ADDRESS

LATCHED ADDRESS

LATCH

~

...

80386 ADDRESS

'---

~

ADDRESS

~

DECODER

"

80386

A

~

DATA

80386 DATA

TRANSCEIVER

DATA

N

"

'4

,

80386 STATUS

SO#/S1#

l-

v'

LOGIC

~

82288

~r---

BUS

CONTROLLER

!

WAIT·STATE

GENERATOR

~

I

82289

-

BUS

ARBITER

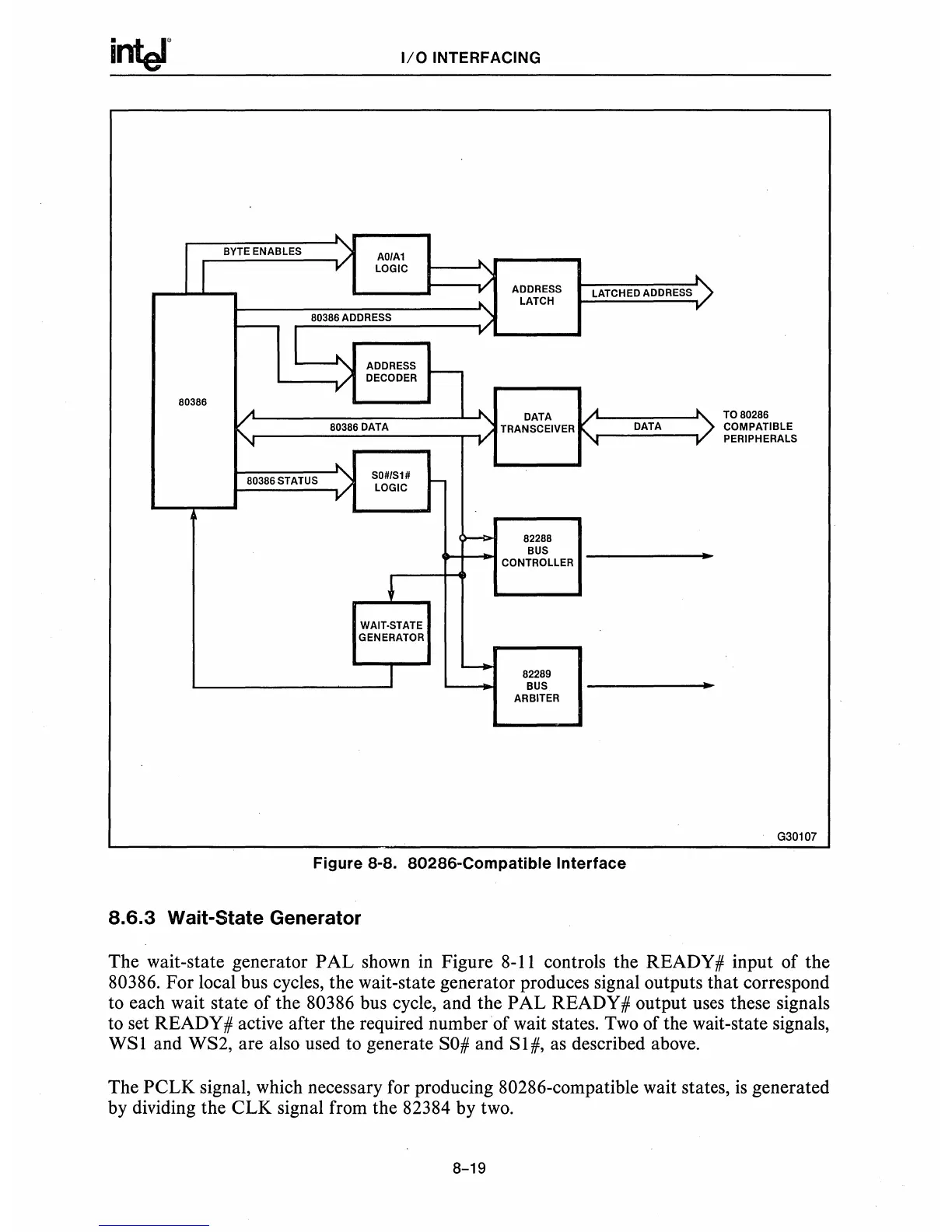

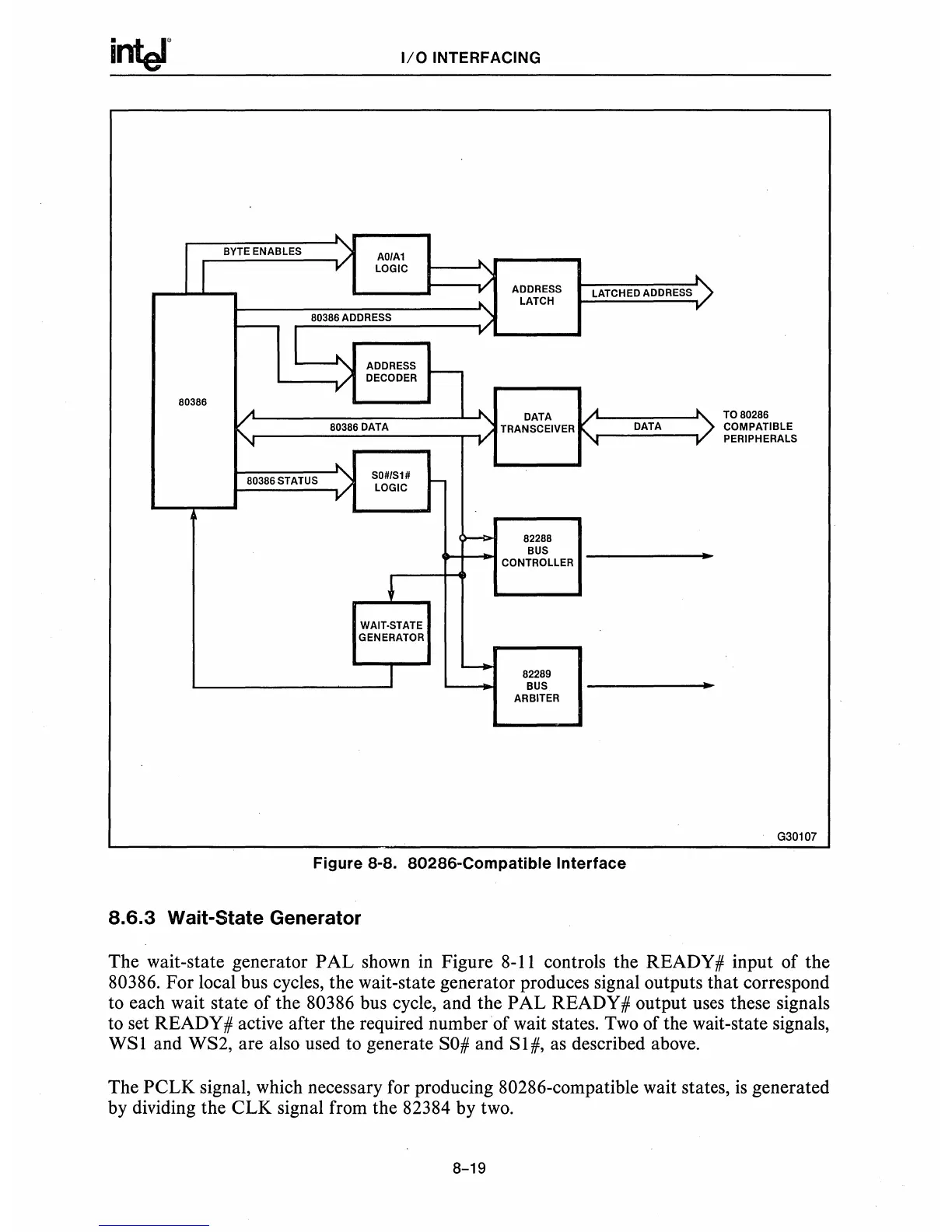

Figure 8-8. 80286-Compatible Interface

8.6.3

Wait-State Generator

....

...

...

...

•

..

TO 80286

COMPATIBLE

PERIPHERALS

G30107

The wait-state generator

PAL

shown in Figure

8-11

controls the READY# input of the

80386. For local bus cycles, the wait-state generator produces signal outputs that correspond

to each wait state of the

80386 bus cycle, and the

PAL

READY # output uses these signals

to set READY # active after the required number of wait states. Two of the wait-state signals,

WS1 and WS2, are also used to generate

SO#

and

Sl#,

as described above.

The

PCLK

signal, which necessary for producing 80286-compatible wait states,

is

generated

by dividing the

CLK

signal from the 82384 by two.

8-19

Loading...

Loading...