MUL TIBUS® I AND

80386

W/R#

-------,

:~:---~';w.

elK

WS2

RD#

WRH

....

-----

ASTBH

DSTBH

READY#

-~o---t-'

RESET

IlBXEN#

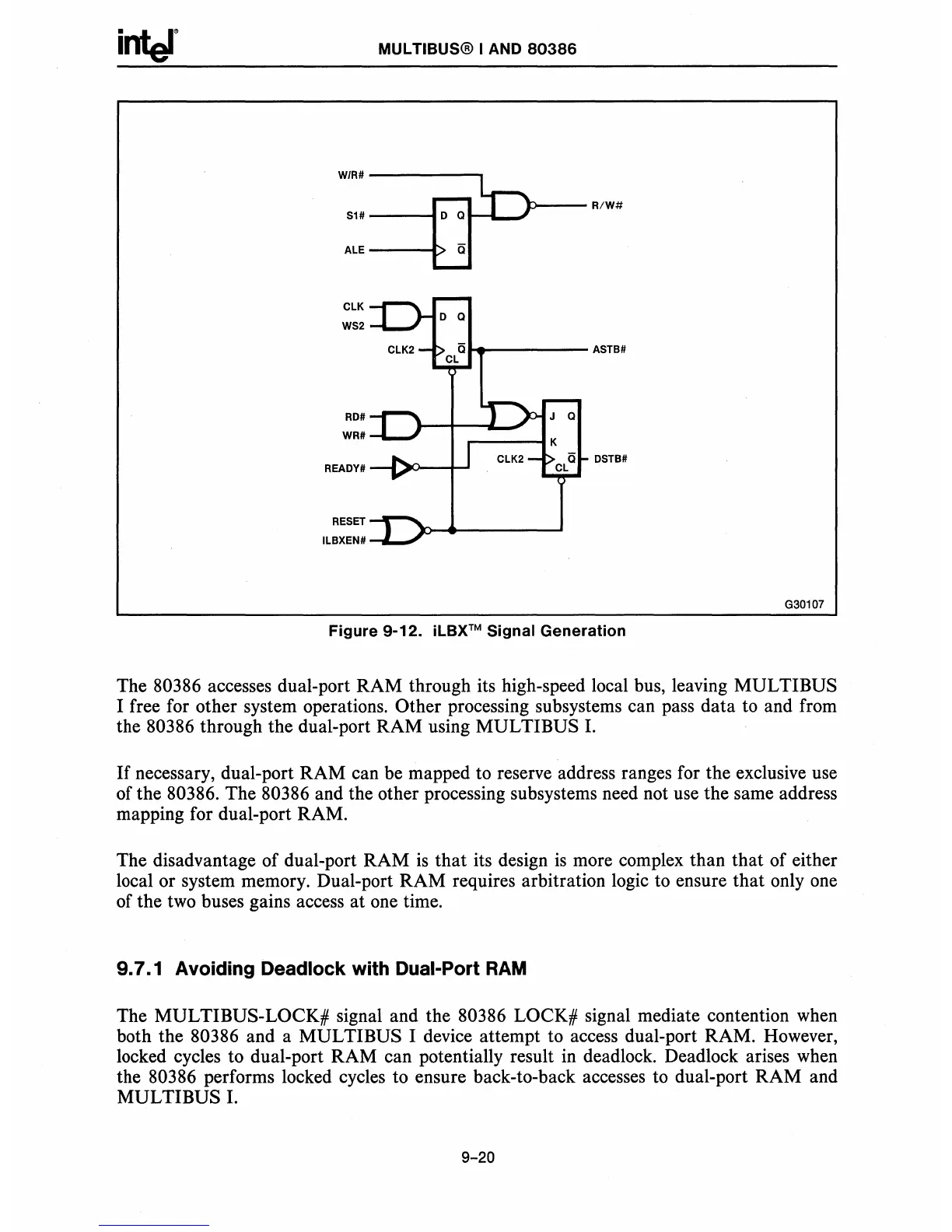

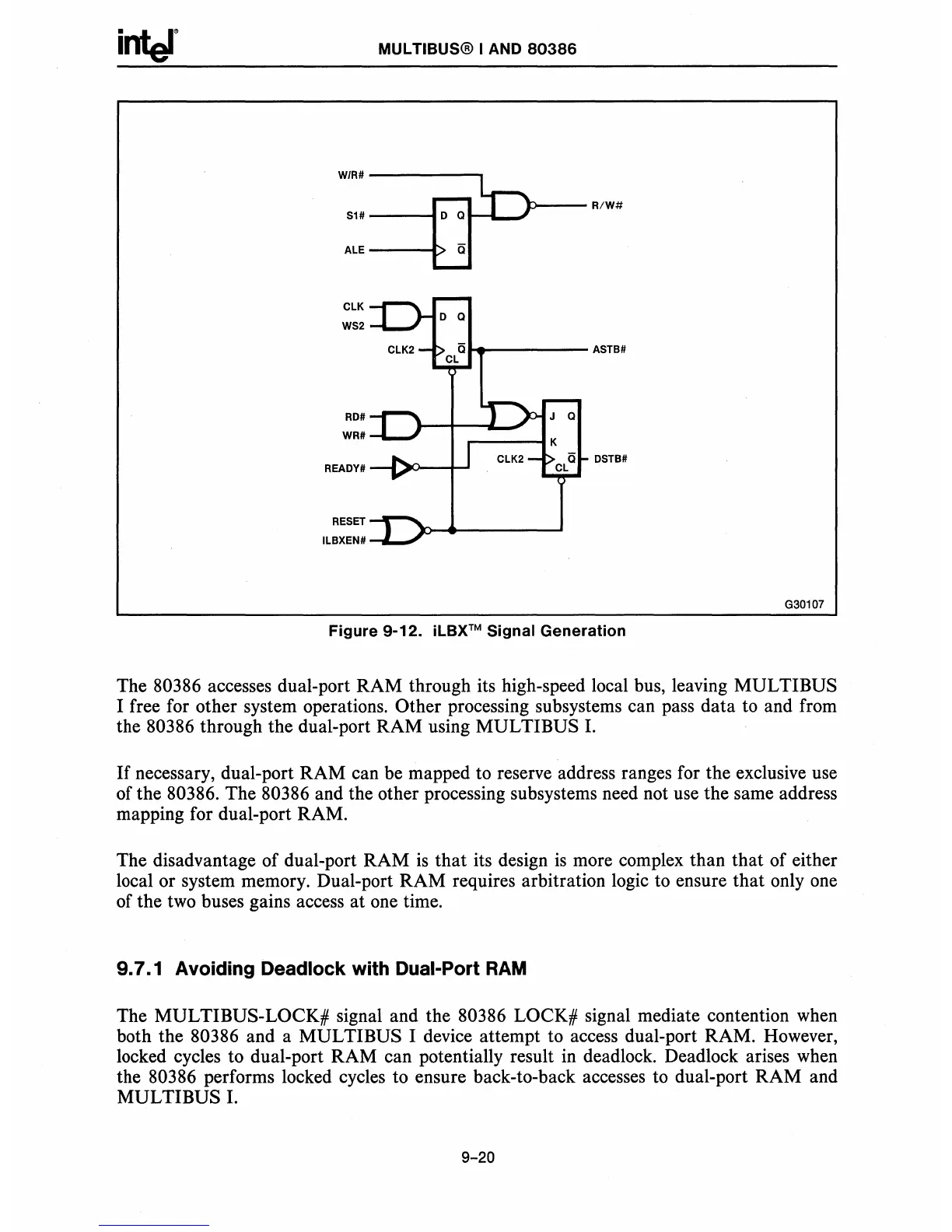

Figure

9-12. iLBX™ Signal

Generation

G30107

The 80386 accesses dual-port RAM through its high-speed local bus, leaving MUL TIBUS

I free for other system operations. Other processing subsystems can pass data to and from

the

80386 through the dual-port RAM using

MUL

TIBUS

I.

If

necessary, dual-port RAM can be mapped to reserve address ranges for the exclusive use

of the

80386. The 80386 and the other processing subsystems need not use the same address

mapping for dual-port RAM.

The disadvantage of dual-port RAM

is

that its design

is

more complex than that of either

local or system memory. Dual-port RAM requires arbitration logic to ensure that only one

of the two buses gains access

at

one time.

9.7.1 Avoiding Deadlock with Dual-Port

RAM

The MULTIBUS-LOCK# signal and the 80386 LOCK# signal mediate contention when

both the

80386 and a MULTI BUS I device attempt to access dual-port RAM. However,

locked cycles to dual-port RAM can potentially result

in

deadlock. Deadlock arises when

the

80386 performs locked cycles to ensure back-to-back accesses to dual-port RAM and

MULTIBUS

I.

9-20

Loading...

Loading...