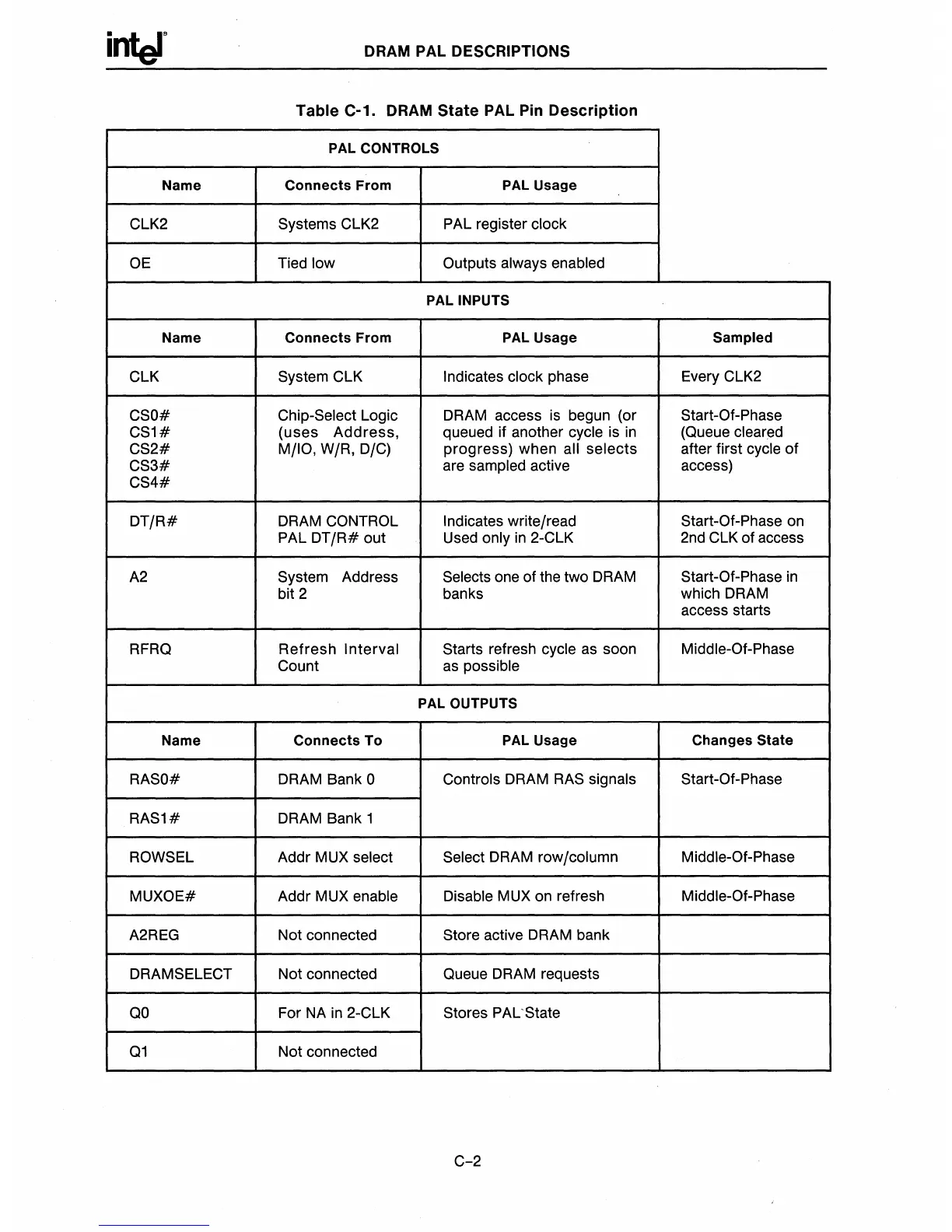

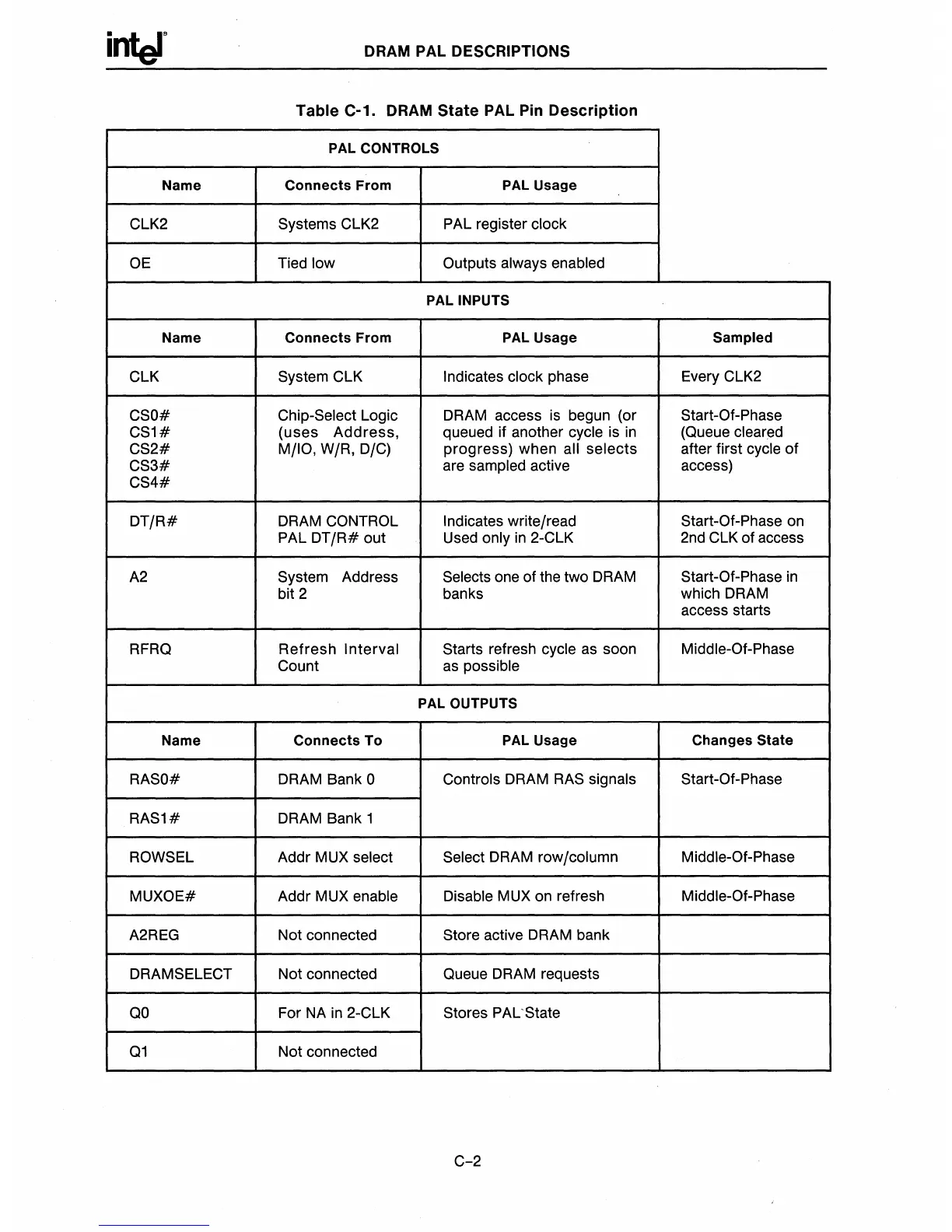

DRAM PAL DESCRIPTIONS

Table

C-1. DRAM

State

PAL Pin

Description

PAL

CONTROLS

Name

Connects From

PAL

Usage

ClK2

Systems

ClK2

PAL register clock

OE

Tied low Outputs always enabled

PAL

INPUTS

Name Connects From

PAL

Usage

Sampled

ClK

System

ClK

Indicates clock phase

Every

ClK2

CSO# Chip-Select

logic

DRAM access

is

begun (or

Start-Of-Phase

CS1#

(uses

Address,

queued if another cycle is

in

(Queue cleared

CS2#

M/IO, W/R, D/G)

progress) when

all selects after first cycle of

CS3#

are sampled active

access)

CS4#

DT/R#

DRAM

CONTROL Indicates write/read

Start-Of-Phase on

PAL

DT/R#

out

Used only

in

2-ClK

2nd

ClK

of access

A2

System Address Selects one of the two

DRAM

Start-Of-Phase

in

bit 2 banks which DRAM

access starts

RFRQ Refresh

Interval

Starts refresh cycle

as

soon Middle-Of-Phase

Count

as possible

PAL

OUTPUTS

Name

Connects To

PAL

Usage Changes State

RASO#

DRAM Bank 0 Controls DRAM

RAS

signals Start-Of-Phase

RAS1#

DRAM Bank 1

ROWSEl

Addr MUX select Select DRAM row/column

Middle-Of-Phase

MUXOE# Addr MUX enable

Disable MUX on refresh Middle-Of-Phase

A2REG Not connected

Store active DRAM bank

DRAMSElECT

Not connected Queue DRAM requests

QO

For

NA

in

2-ClK

Stores

PAl'State

Q1

Not connected

C-2

Loading...

Loading...