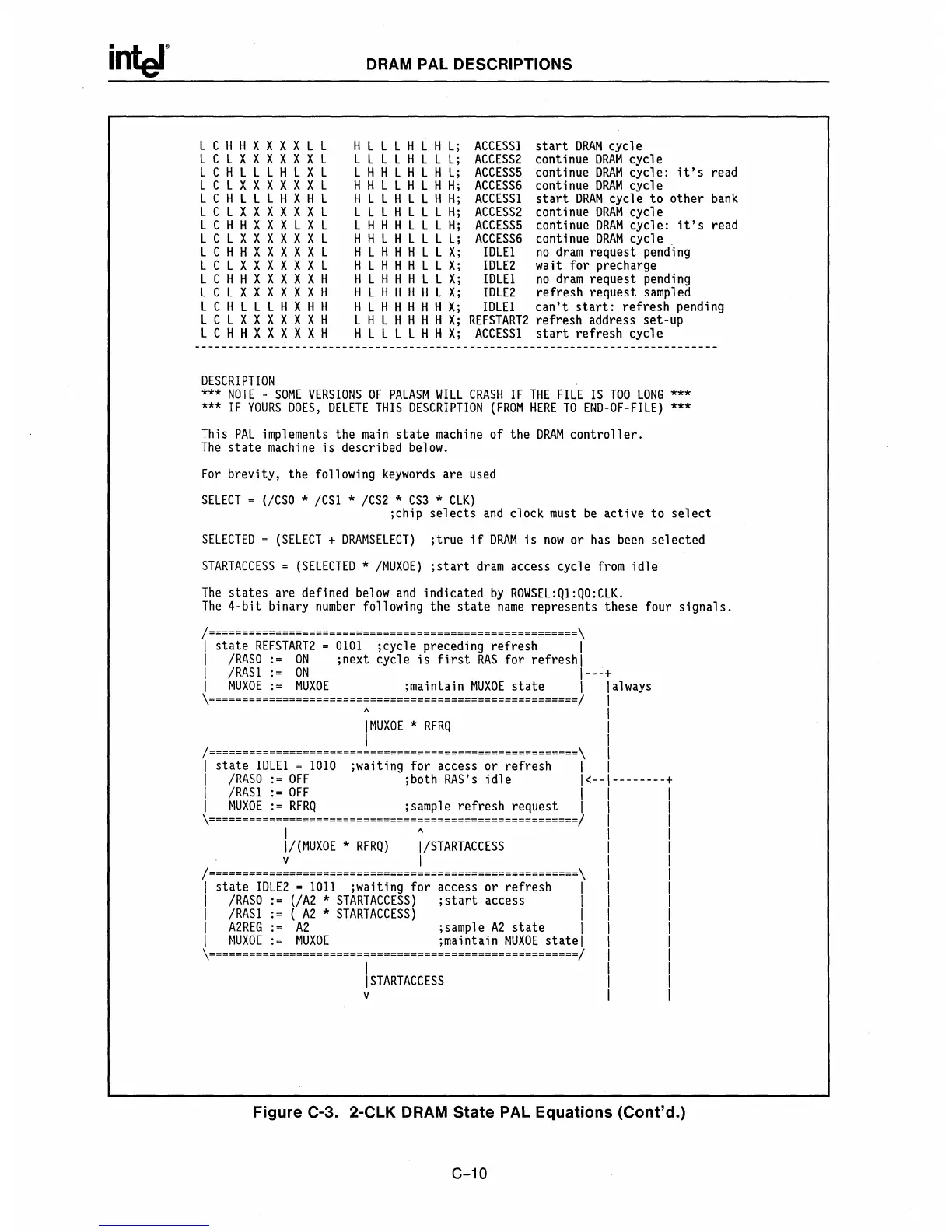

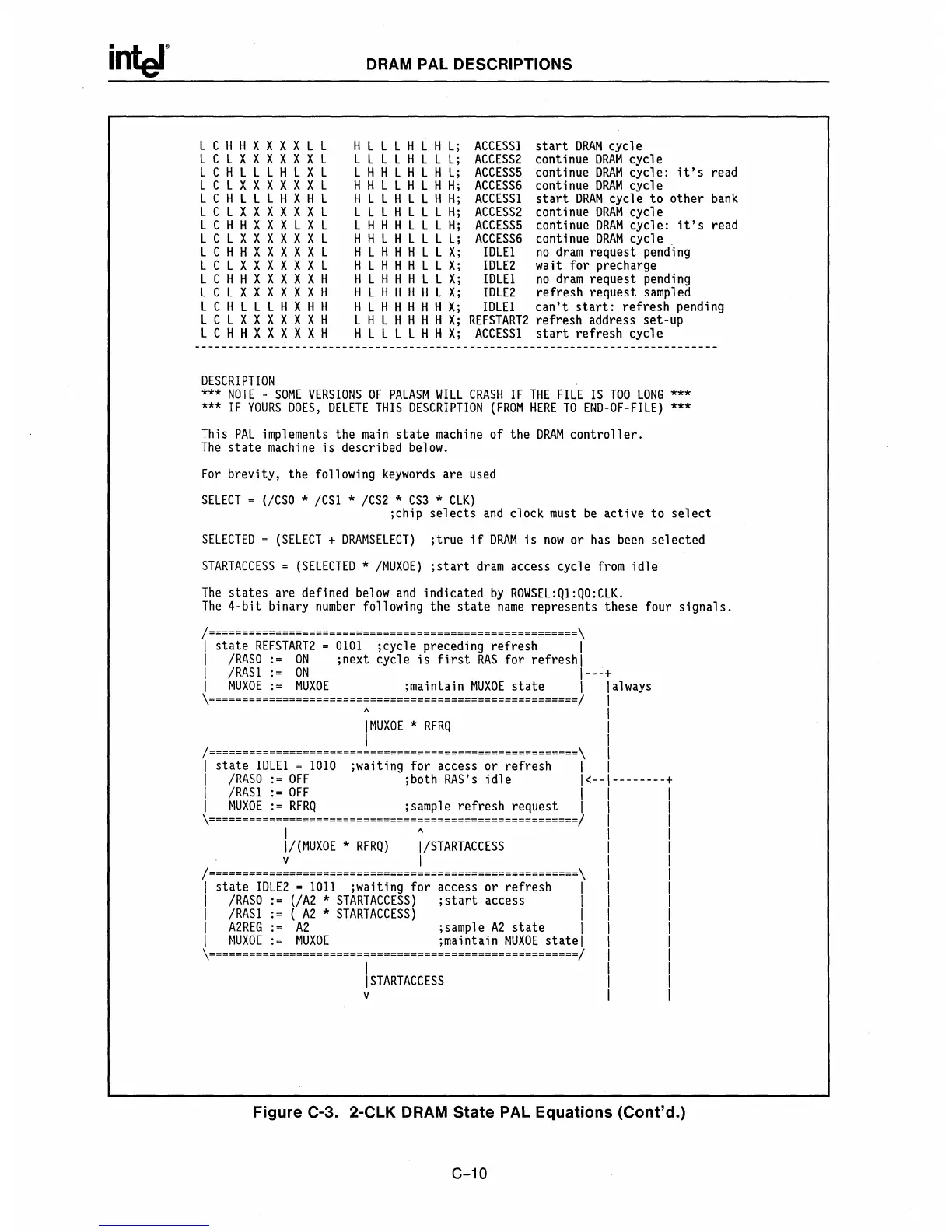

DRAM PAL DESCRIPTIONS

ACCESSI

start

DRAM

cycle

ACCESS2

continue

DRAM

cycle

LCHHXXXXLL

LCLXXXXXXL

LCHLLLHLXL

L C L X X X X X X L

L

C H L L L H X H L

L

C L X X X X X X L

LCHHXXXLXL

LCLXXXXXXL

L C H H X X X X X L

L

C L X X X X X X L

L

C H H X X X X X H

LCLXXXXXXH

LCHLLLHXHH

LCLXXXXXXH

LCHHXXXXXH

HLLLHLHL;

LLLLHLLL;

L H H L H L H L;

H H L L H L H

H;

H L L H L L H

H;

L L L H L L L

H;

L H H H L L L

H;

H H L H L L L L;

H L H H H L L

x;

H L H H H L L

X;

H L H H H L L

X;

H L H H H H L

X;

H L H H H H H

X;

L H L H H H H

X;

H L L L L H H

X;

ACCESS5

continue

DRAM

cycle:

it's

read

ACCESS6

continue

DRAM

cycle

ACCESSI

start

DRAM

cycle

to

other

bank

ACCESS2

continue

DRAM

cycle

ACCESS5

continue

DRAM

cycle:

it's

read

ACCESS6

continue

DRAM

cycle.

IDLE!

no

dram

request pending

IDLE2

wait

for

precharge

IDLE

1

no

dram

request pending

IDLE2

refresh

request sampled

IDLE

1

can't

start:

refresh

pending

REFSTART2

refresh

address set-up

ACCESSI

start

refresh

cycl

e

DESCRIPTION

***

NOTE

-

SOME

VERSIONS

OF

PALASM

WILL

CRASH

IF

THE

FILE

IS

TOO

LONG

***

***

IF

YOURS

DOES,

DELETE

THIS

DESCRIPTION

(FROM

HERE

TO

END-OF-FILE)

***

This

PAL

implements the

main

state

machine

of

the

DRAM

controller.

The

state

machine

is

described below.

For

brevity,

the

following

keywords are

used

SELECT

=

(lCSO

* /CSI *

/CS2

*

CS3

*

CLK)

;chip

selects

and

clock

must

be

active

to

select

SELECTED

=

(SELECT

+

DRAMSELECT)

;true

if

DRAM

is

now

or

has

been

selected

STARTACCESS

=

(SELECTED

*

/MUXOE)

;start

dram

access

cycle

from

idle

The

states

are

defined

below

and

indicated

by

ROWSEL:Ql:QO:CLK.

The

4-

bi

t

bi

nary

number

foll

owi

ng

the

state

name

represents these

four

signals.

/=======================================================\

1

state

REFSTART2

=

0101

;cycle

preceding

refresh

1

1 /RASO:=

ON

;next

cycle

is

first

RAS

for

refresh

1

1

/RASl:=

ON

I--~+

1

MUXOE:=

MUXOE

;maintain

MUXOE

state

1 always

\=======================================================/

A

1

MUXOE

*

RFRQ

1

/=======================================================\

1

state

IDLE! =

1010

;waiting

for

access

or

refresh

1

1 /RASO:=

OFF

;both

RAS's

idle

1<--

1

/RASl:=

OFF

1

1

MUXOE:=

RFRQ

;sample

refresh

request 1

\=======================================================/

1 A

I/(MUXOE

*

RFRQ)

I/STARTACCESS

v 1

/=======================================================\

1

state

IDLE2

=

1011

;waiting

for

access

or

refresh

1

1 /RASO:=

(lA2

*

STARTACCESS)

;start

access 1

1

/RASl:

= (

A2

*

STARTACCESS)

1

1 A2REG:=

A2

;sample

A2

state

1

1

MUXOE:=

MUXOE

;maintain

MUXOE

statel

\=======================================================/

1

1

STARTACCESS

v

--------+

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Figure C-3. 2-CLK DRAM State PAL Equations (Cont'd.)

C-10

Loading...

Loading...