DRAM

PAL

DESCRIPTIONS

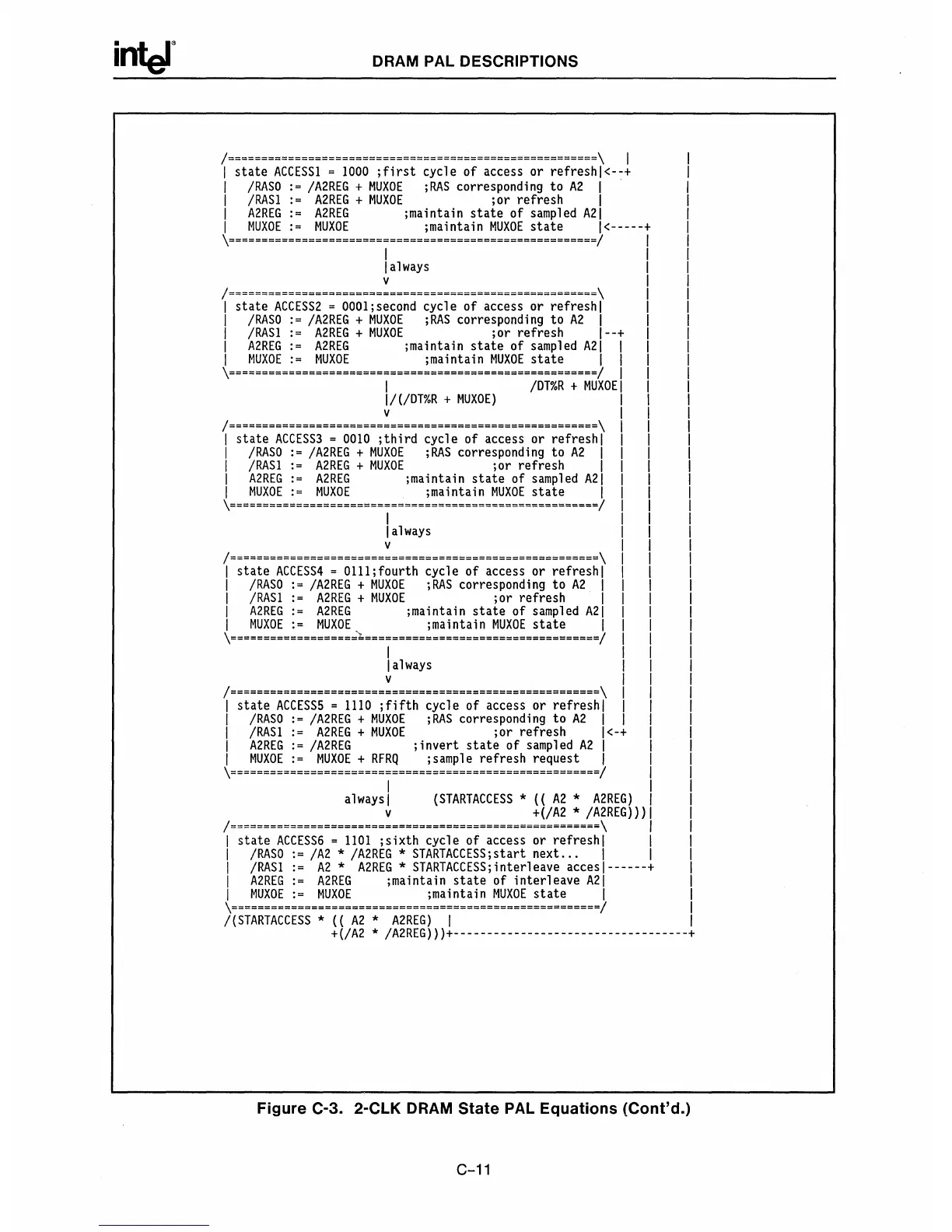

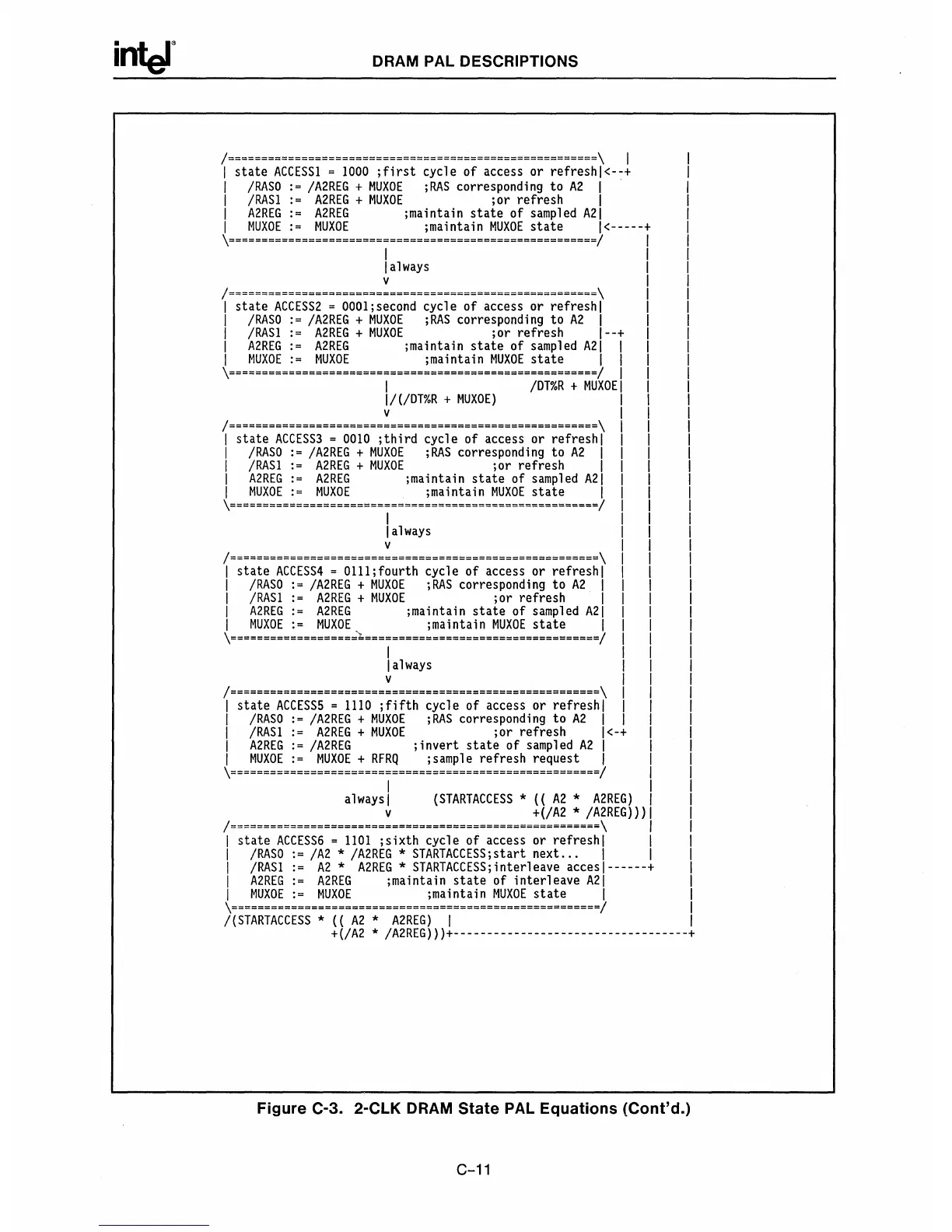

1=====================================================

==\ I

I

state

ACCESSI

= 1000

;first

cycle

of

access

or

refreshl<--+

I IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASI:=

A2REG

+

MUXOE

;or

refresh

I

I

A2REG:

=

A2REG

;ma

i

nta

instate

of

sampled

A21

I

MUXOE:=

MUXOE

;maintain

MUXOE

state

1<-----+

\=====================================================

==1

I

lalways

v

1==

==

=====

=====================

=

========================

\

I

state

ACCESS2

= 0001; second cycl e

of

access

or

refresh

I

I IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASI:

=

A2REG

+

MUXOE

;

or

refresh

1--+

I

A2REG:

=

A2REG

;ma

i

nta

instate

of

sampled

A21

I

I

MUXOE:

=

MUXOE

;ma

i

nta

in

MUXOE

state

I I

\=====================================================

==1

I

I

IDT%R

+

MUXOE

I

I/UDT%R

+

MUXOE)

I

v I

1==

==

======

=

======

=====

= =

=====

==========================

\

I

state

ACCESS3

= 0010

;third

cycle

of

access

or

refresh

I

I IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASI:=

A2REG

+

MUXOE

;or

refresh

I

I

A2REG:=

A2REG

;maintain

state

of

sampled

A21

I

MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\=====================================================

==1

I

lalways

v

1=

==

====================================================

\

I

state

ACCESS4

= 0 111;

fourth

cycle

of

access

or

refresh

I

I IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I

I

IRASI:=

A2REG

+

MUXOE

;or

refresh

I

I

A2REG:=

A2REG

;maintain

state

of

sampled

A21

I

MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\==================,;,,=================================

==1

I

I

always

v

1==

==============

==============

=

====== ======

============

\

I

state

ACCESS5

= 1110

;fifth

cycle

of

access

or

refresh

I

I

IRASO:=

IA2REG

+

MUXOE

;RAS

corresponding

to

A2

I I

I

IRASI:=

A2REG

+

MUXOE

;or

refresh

1<-+

I

A2REG:=

IA2REG

;invert

state

of

sampled

A2

I

I

MUXOE:

=

MUXOE

+

RFRQ

;

samp

1 e

refresh

request

I

\=====================================================

==1

I

always I

(STARTACCESS

*

((

A2

*

A2REG)

v

+UA2

*

IA2REG)))

1=====================================================

==\

I

state

ACCESS6

= 1101

;sixth

cycle

of

access

or

refresh

I

I

IRASO:= IA2 *

IA2REG

*

STARTACCESS;start

next...

I

I

IRASI:=

A2

*

A2REG

*

STARTACCESS;interleave

accesl------+

I

A2REG:=

A2REG

;maintain

state

of

interleave

A21

I

MUXOE:=

MUXOE

;maintain

MUXOE

state

I

\=====================================================

==1

I(STARTACCESS

*

((

A2

*

A2REG)

I

+UA2 *

IA2REG)))+-----------------------------------+

Figure C-3. 2-CLK

DRAM

State

PAL

Equations (Cont'd.)

C-11

Loading...

Loading...