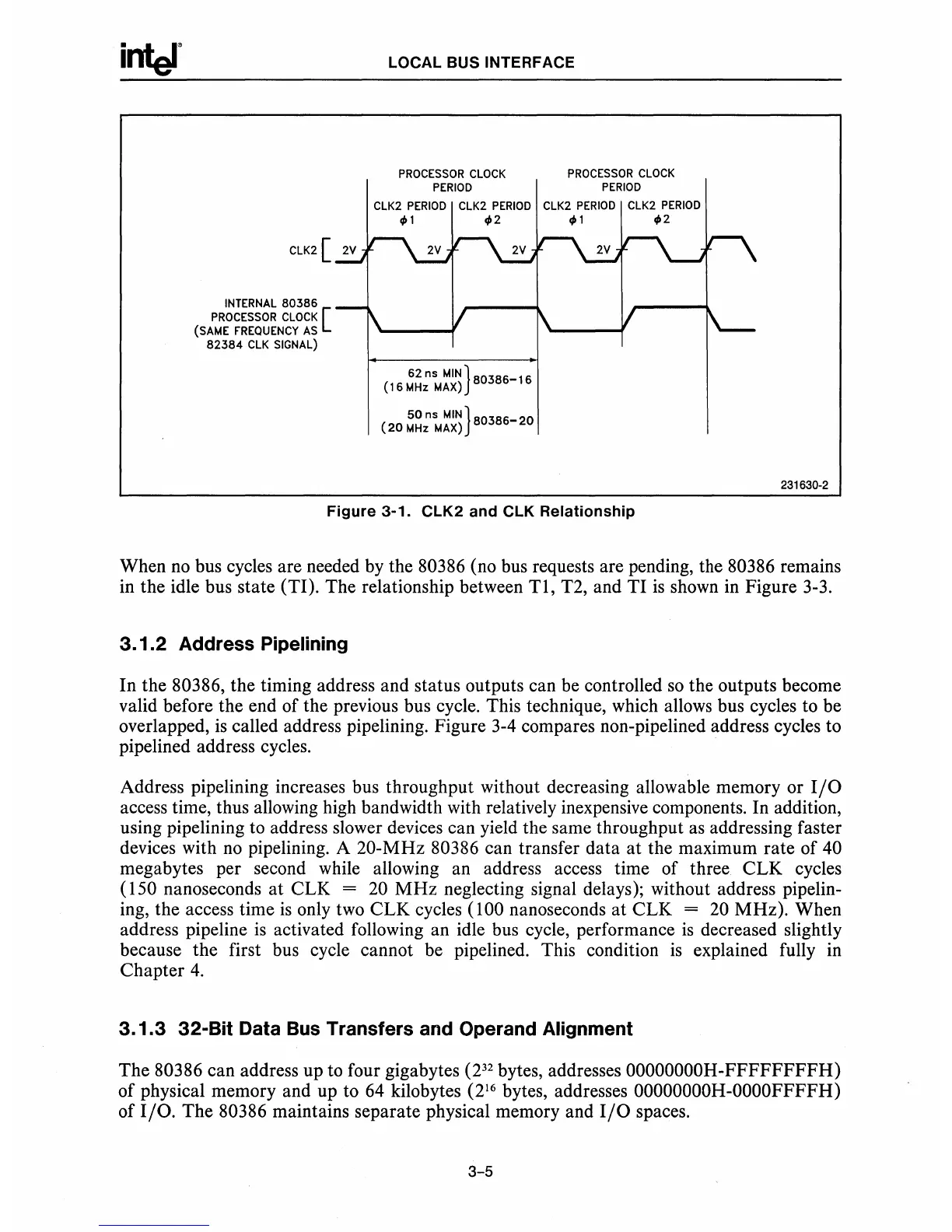

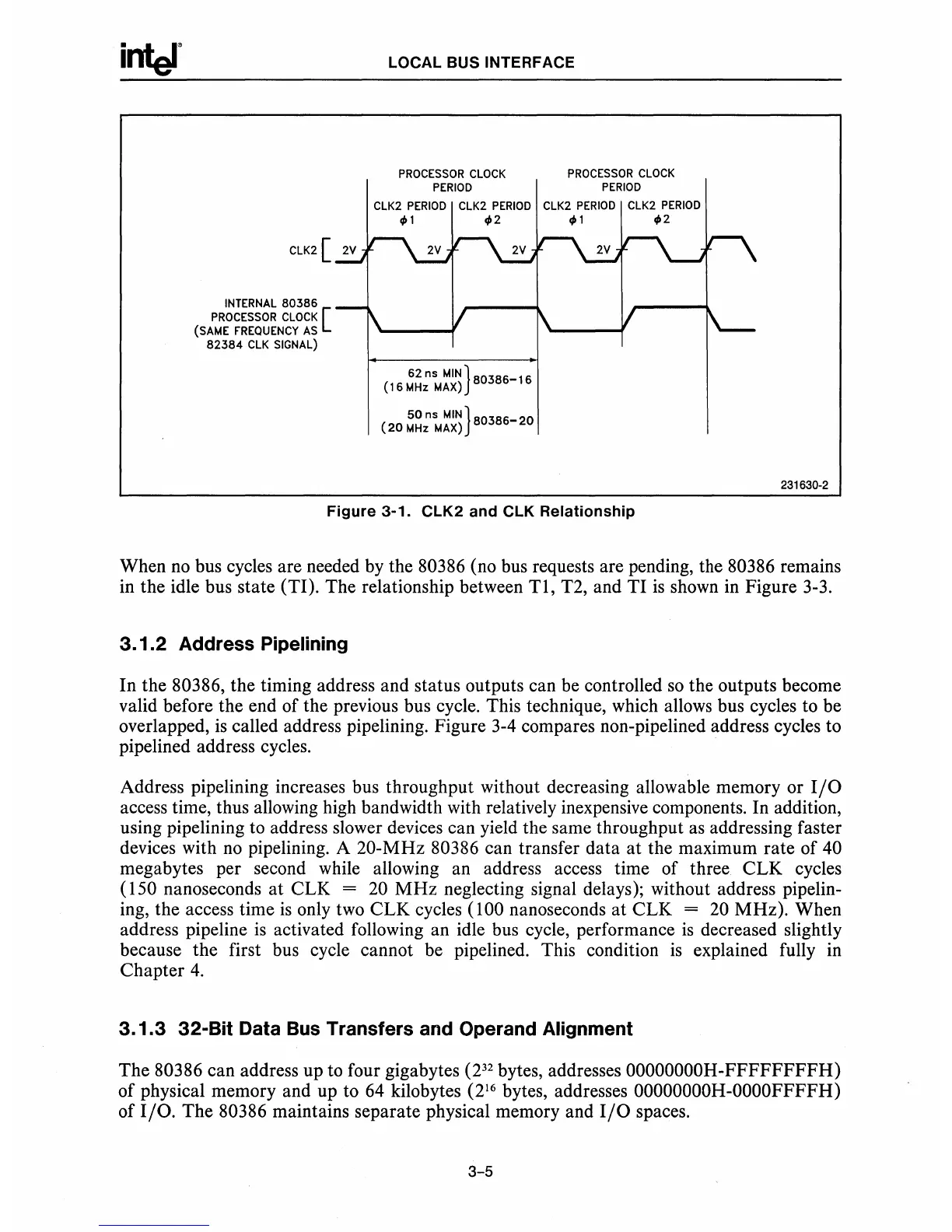

CLK2 [

INTERNAL

80386

PROCESSOR

CLOCK

[

(SAME

FREQUENCY

AS

82384

CLK SIGNAL)

lOCAL

BUS

INTERFACE

PROCESSOR

CLOCK

PERIOD

PROCESSOR

CLOCK

PERIOD

CLK2

PERIOD

CLK2

PERIOD

CLK2

PERIOD

CLK2

PERIOD

1/>1

1/>2

1/>1

1/>2

62ns

MIN}

(16

MHz MAX)

80386-16

SOns

MIN}

(20

MHz MAX)

80386-

20

Figure

3-1.

ClK2

and

ClK

Relationship

231630-2

When

no

bus cycles are needed by the 80386 (no bus requests are pending, the 80386 remains

in the idle bus state (TI). The relationship between

Tl,

T2, and

TI

is

shown in Figure 3-3.

3.1.2

Address Pipelining

In

the 80386, the timing address and status outputs can be controlled so the outputs become

valid before the end of the previous bus cycle. This technique, which allows bus cycles to be

overlapped,

is

called address pipelining. Figure 3-4 compares non-pipelined address cycles to

pipelined address cycles.

Address pipelining increases bus throughput without decreasing allowable memory or

I/0

access time, thus allowing high bandwidth with relatively inexpensive components.

In

addition,

using pipelining to address slower devices can yield the same throughput

as

addressing faster

devices with

no

pipelining. A 20-MHz 80386 can transfer data

at

the maximum rate of 40

megabytes per second while allowing an address access time of three

CLK

cycles

(150 nanoseconds

at

CLK

= 20

MHz

neglecting signal delays); without address pipelin-

ing, the access time

is

only two

CLK

cycles (100 nanoseconds

at

CLK

= 20 MHz). When

address pipeline

is

activated following an idle bus cycle, performance

is

decreased slightly

because the first bus cycle cannot be pipelined. This condition

is

explained fully in

Chapter

4.

3.1.3

32-Bit Data

Bus

Transfers and Operand Alignment

The

80386 can address up to four gigabytes (2

32

bytes, addresses

OOOOOOOOH-FFFFFFFFH)

of physical memory and up to 64 kilobytes

(216

bytes, addresses

OOOOOOOOH-OOOOFFFFH)

of

I/O.

The 80386 maintains separate physical memory and

I/O

spaces.

3-5

Loading...

Loading...