ClK2[

(82384 ClK) [

BEl

#.

BE2#.

BE3#

[

BED#.

A3-A31. [

101/10#.

D/C#. W

/R#

lOCK# [

ADS#

[

BSI

6#

[

08-031

[

LOCAL BUS INTERFACE

INTERRUPT

ACKNOWLEDGE

CYCLE

I

PREVIOUS

I

CYCLE

T2

TI

T2

T2

TI

_1.Il

nIL

1.Il

nIL

n..rL

-V

V V V

V

XXXXX

.XX

XXXXX)'

XXX

XXXXXY

,{XXX

XXXXX

~/

XX

Xv,

~XX

XX

XX

XX

X

IGNORED

XX

XX XX

Xy

~\

~X

IGNORED

- ----

.---

-----

--0--

IGNORED

- ---- ----

-----

--cp--

IDLE

(4

BUS

STATES)

TI

n

n..rL

nn

V

V

XX

.XX

X X

Xx

XX

.XX

XX

.XX

XX

.XX

----

-----

----

-----

n

rut

V

.XX

X

.XX

.XX

.XX

-----

-----

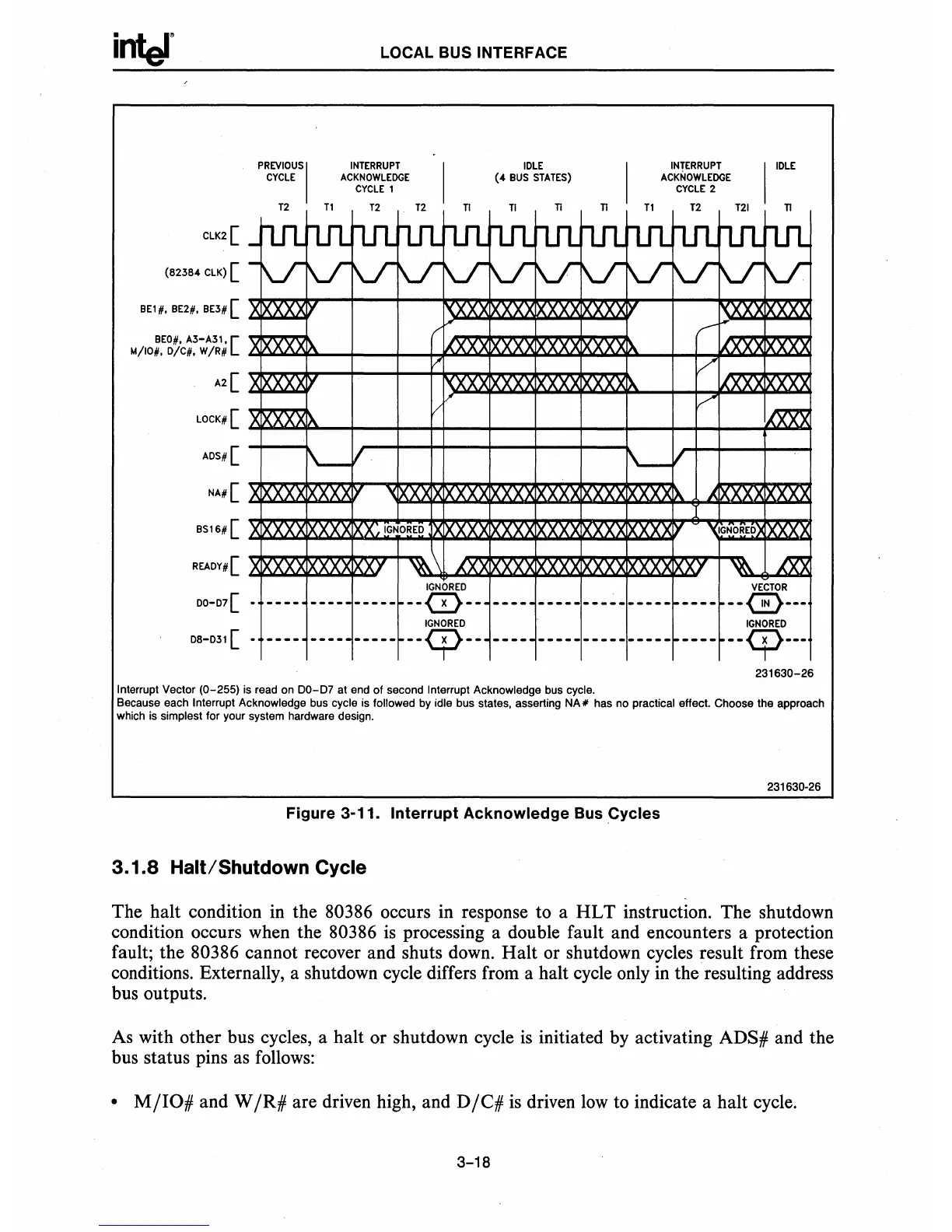

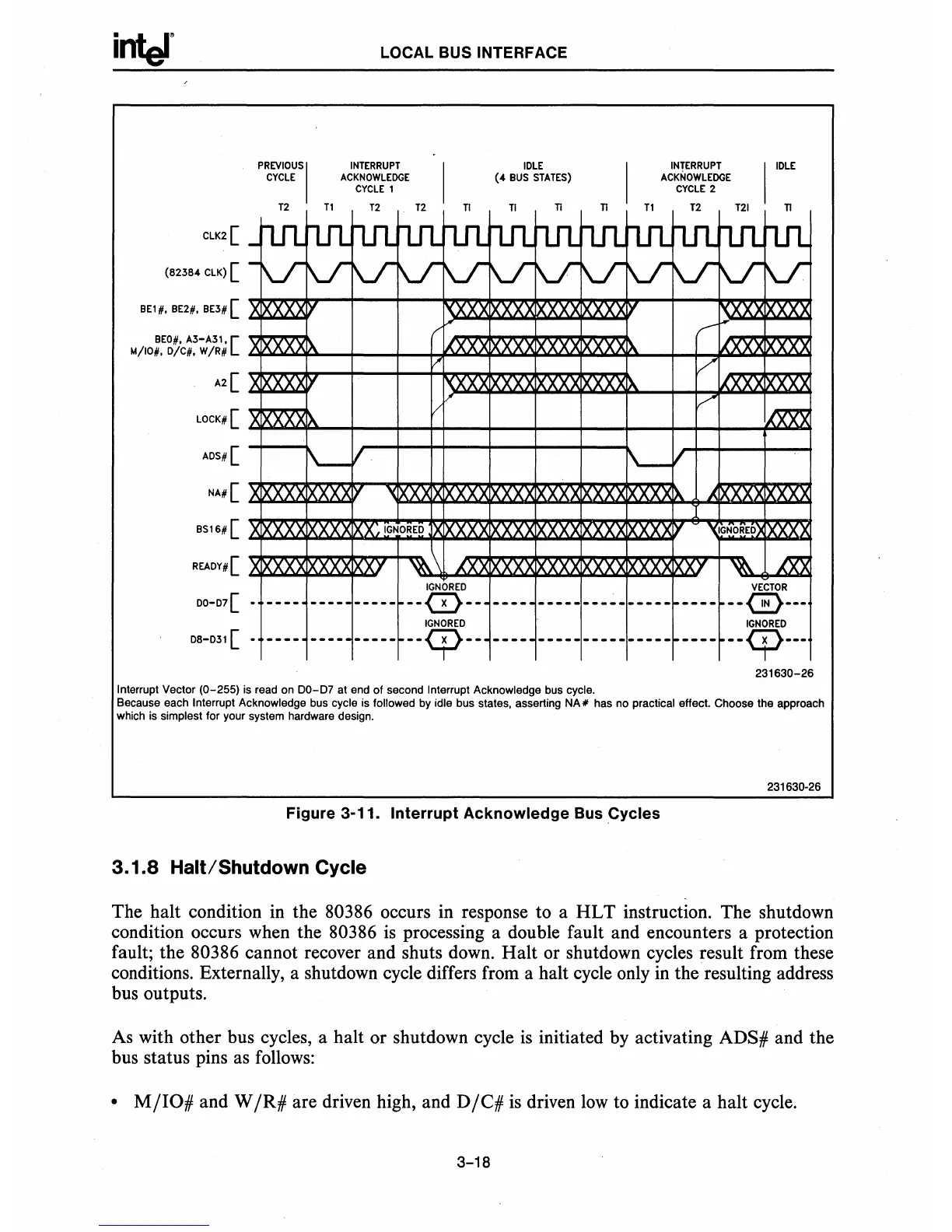

Interrupl Vector

(0-255)

is read on

00-07

at end of second Interrupt Acknowledge bus cycle.

INTERRUPT

ACKNOWLEDGE

CYCLE

2

IDLE

TI

T2

T21

n

rut rut

n..rL n..rL

V V

V V

XX

XX

r

XX

XX

V

XX

X

V

mY..

~V

XX

I~

-<XXX

XX

.XX

IY

,<IGNORED

XXXX

XX

Xy

~

m

VECTOR

-----

----

--@---

IGNORED

-----

----

--cp---

231630-26

Because each Interrupt Acknowledge bus cycle is followed by idle bus states. asserting

NA#

has no practical effect. Choose the approach

which is

simplest for your system hardware design.

231630-26

Figure

3-11.

Interrupt

Acknowledge

Bus

Cycles

3.1.8

Halt/Shutdown

Cycle

The halt condition

in

the 80386 occurs in response to a

HLT

instruction. The shutdown

condition occurs when the 80386

is

processing a double fault and encounters a protection

fault; the 80386 cannot recover and shuts down. Halt or shutdown cycles result from these

conditions. Externally, a shutdown cycle differs from a halt cycle only

in

the resulting address

bus outputs.

As with other bus cycles, a halt or shutdown cycle

is

initiated by activating ADS# and the

bus status pins as

follows:

•

MjIO#

and W

jR#

are driven high, and

DjC#

is

driven

low

to indicate a halt cycle.

3-18

Loading...

Loading...