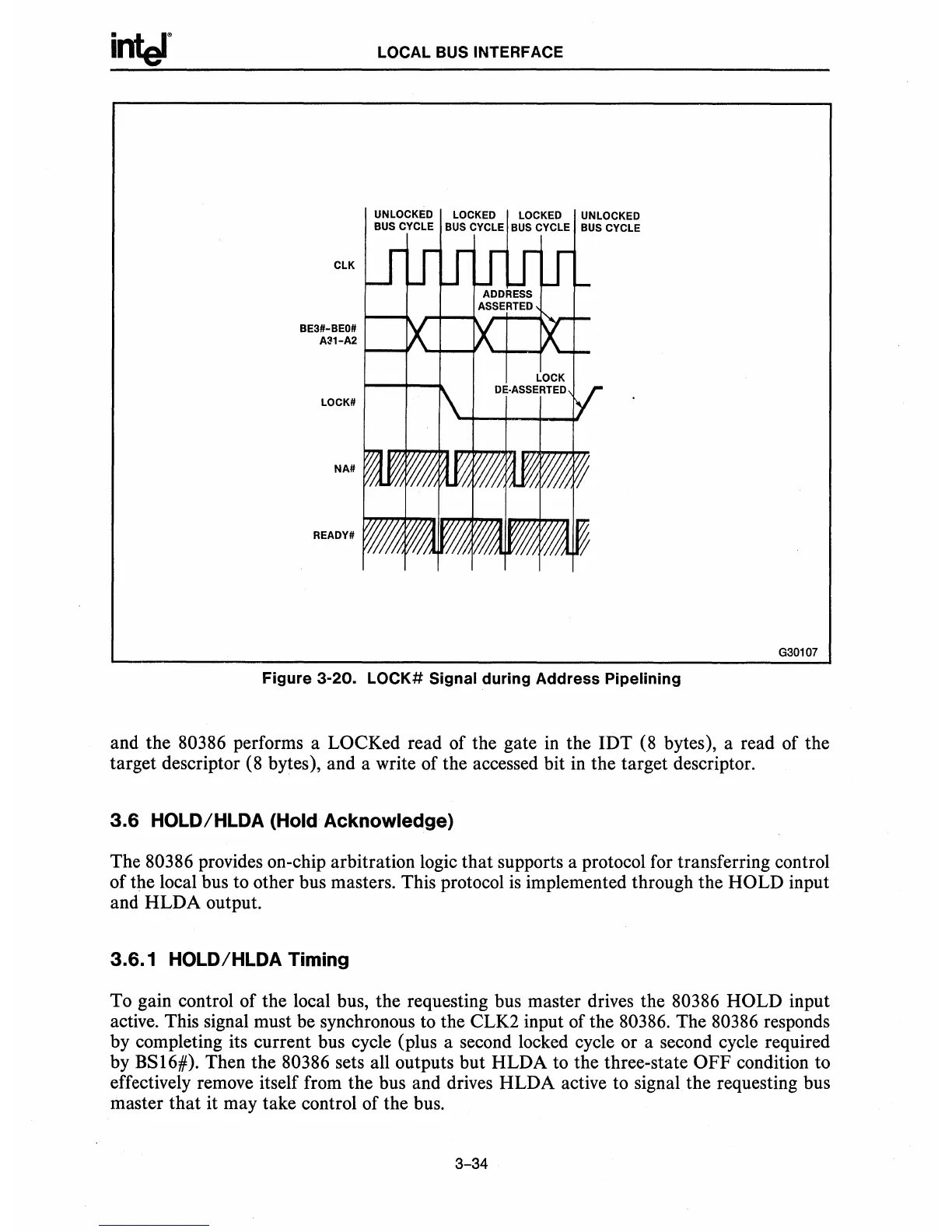

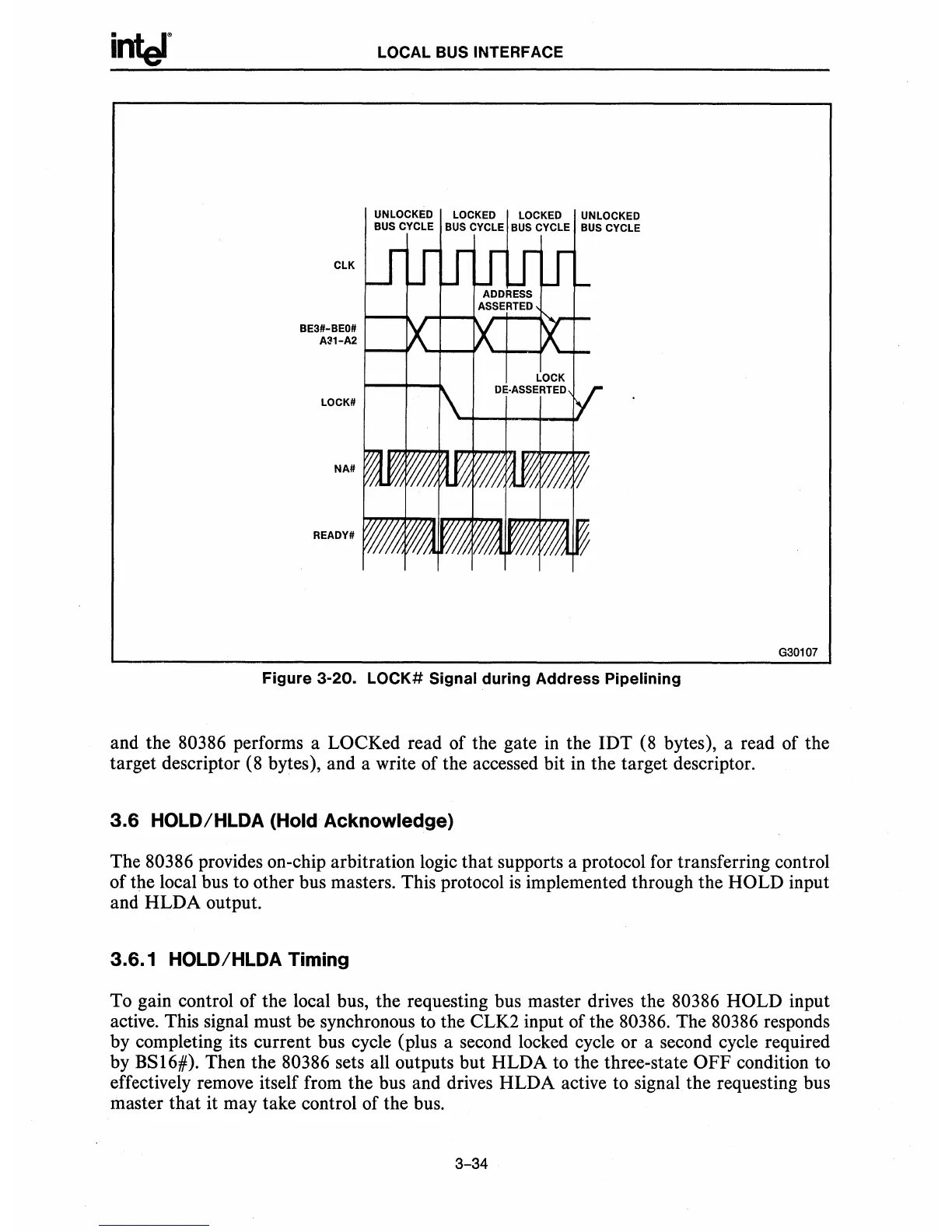

ClK

BE3#-BEO#

A31-A2

lOCK#

NAn

READY"

LOCAL BUS INTERFACE

UNLOCKED lOCKED

lOCKED

UNLOCKED

BUS

CYCLE

BUS

CYCLE

BUS

CYCLE

BUS

CYCLE

Figure

3-20.

LOCK#

Signal

during

Address

Pipelining

G30107

and the 80386 performs a LOCKed read of the gate

in

the IDT (8 bytes), a read of the

target descriptor (8 bytes), and a write of the accessed bit in the target descriptor.

3.6

HOLD/HLDA (Hold Acknowledge)

The 80386 provides on-chip arbitration logic that supports a protocol for transferring control

of the local bus to other bus masters. This protocol

is

implemented through the HOLD input

and HLDA output.

3.6.1 HOLD/HLDA Timing

To gain control of the local bus, the requesting bus master drives the 80386 HOLD input

active. This signal must be synchronous to the CLK2 input of the 80386. The

80386 responds

by completing its current bus cycle (plus a second locked cycle or a second cycle required

by BS16#). Then the

80386 sets all outputs but HLDA to the three-state OFF condition to

effectively remove itself from the bus and drives HLDA active to signal the requesting bus

master that it may take control of the bus.

3-34

Loading...

Loading...