82384

CLOCK

GENERATOR

CLK2

RESET

l

1

t

CLK2 RESET

BUSY

ERROR

PEREQ

M/iO

A31

A2

80386

CPU

015:0

--

READY

ADS,

M/iO

Ole,

W/R

COPROCESSOR HARDWARE INTERFACE

r------------,

I

I

I

74F373

I

I

LATCH

I I

I

IL!

I

t

I -

I

A I

I

A I

...

I

74F245

'4

I

,-

~i

I

I

t

I

I

lOR

I

LOCAL

I

~

BUS

CONTROLLER

lOW

I

--pi

I

I

LOCAL BUS LOGIC

II

SHARED WITH OTHER I

.....

__

M~O~

~D

J!..O

__

...J

II.

,-

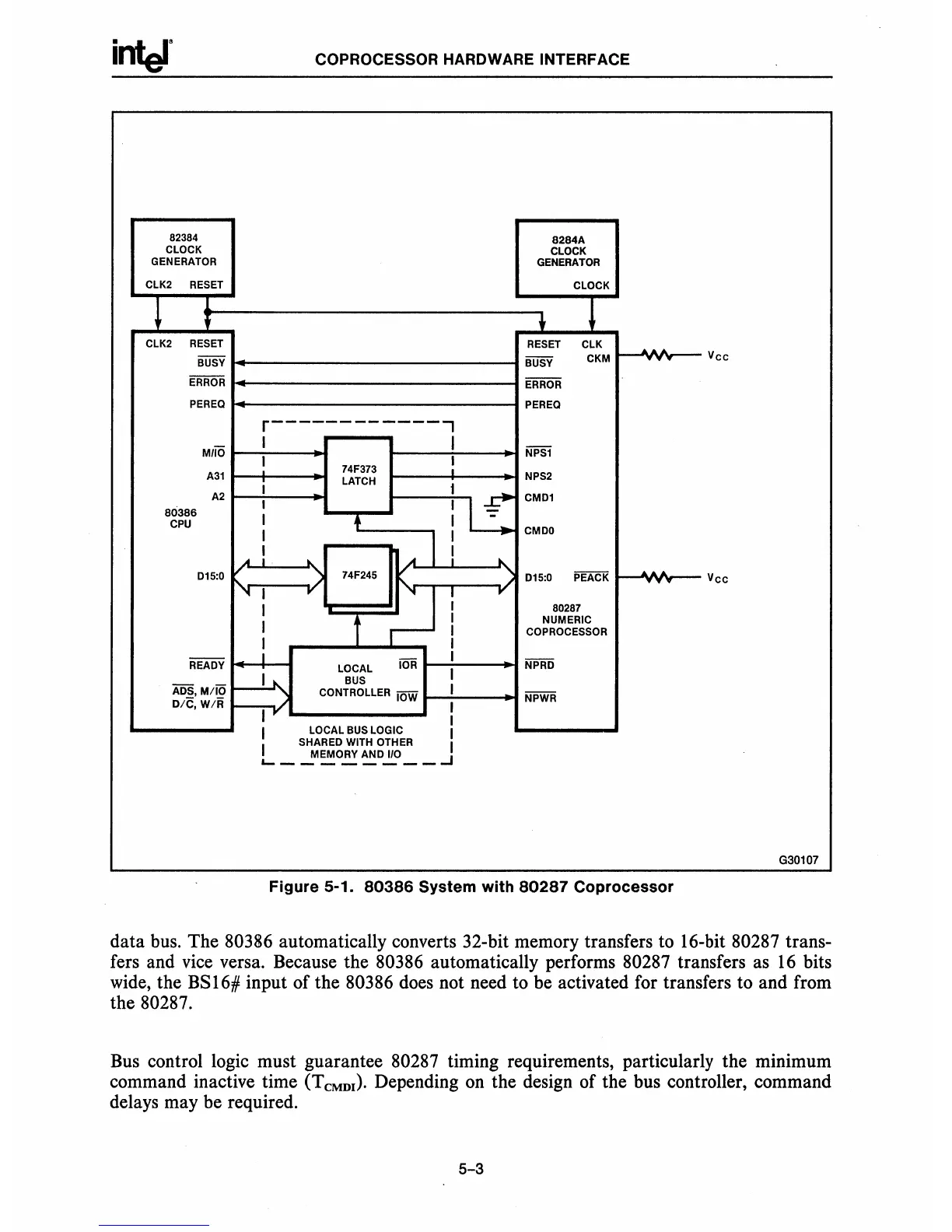

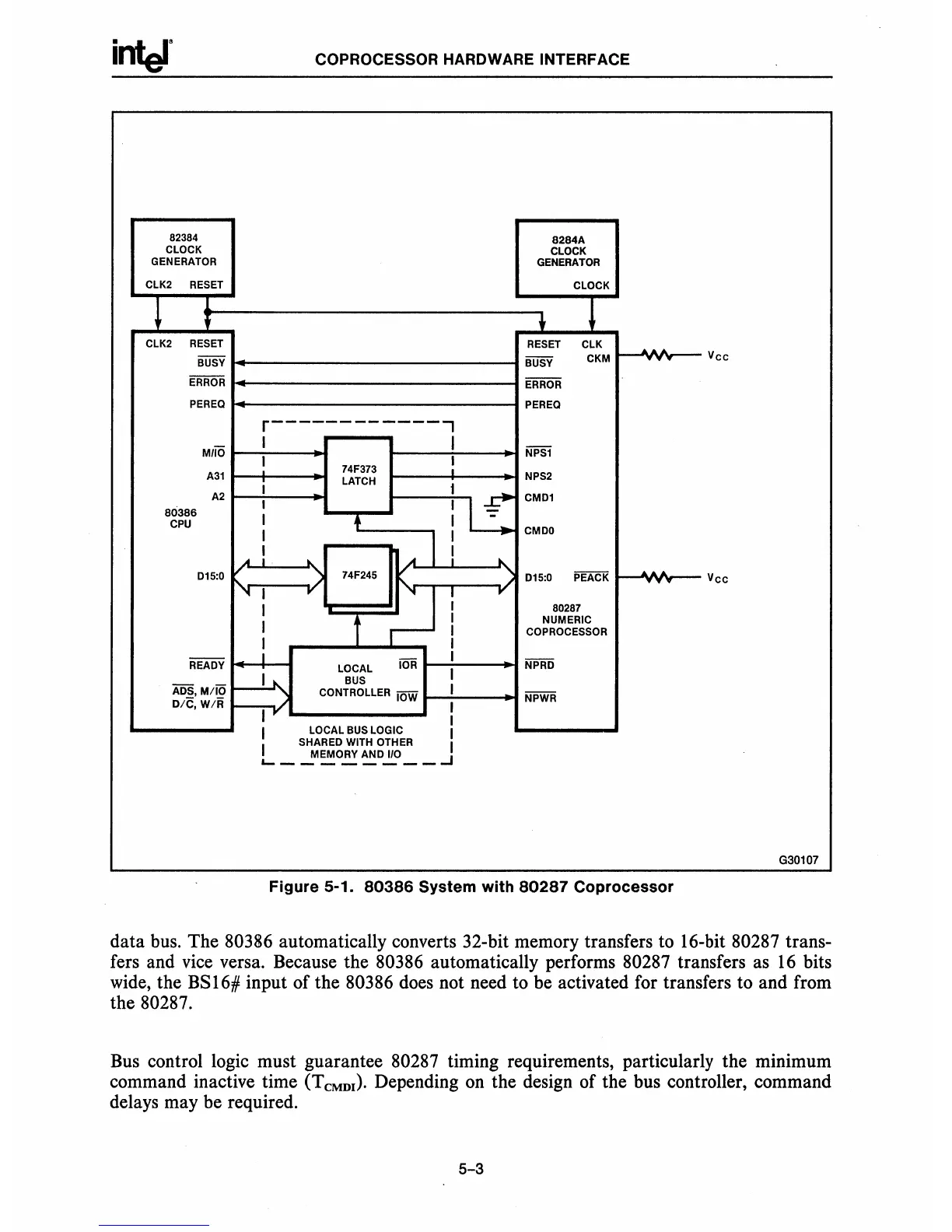

8284A

CLOCK

GENERATOR

CLOCK

+

l

RESET

CLK

BUSY

CKM

ERROR

PEREQ

NPS1

NPS2

CM01

CMDO

015:0 PEACK

80287

NUMERIC

COPROCESSOR

NPRO

NPWR

--..

..

Figure 5-1.

80386

System with

80287

Coprocessor

Vee

Vee

G30107

data bus. The 80386 automatically converts 32-bit memory transfers to 16-bit 80287 trans-

fers and vice versa. Because the 80386 automatically performs 80287 transfers as

16

bits

wide, the

BSI6# input of the 80386 does not need to be activated for transfers to and from

the

80287.

Bus

control logic must guarantee 80287 timing requirements, particularly the minimum

command inactive time

(T

CMDI

).

Depending

on

the design of the bus controller, command

delays may be required.

5-3

Loading...

Loading...