COPROCESSOR HARDWARE INTERFACE

J

L

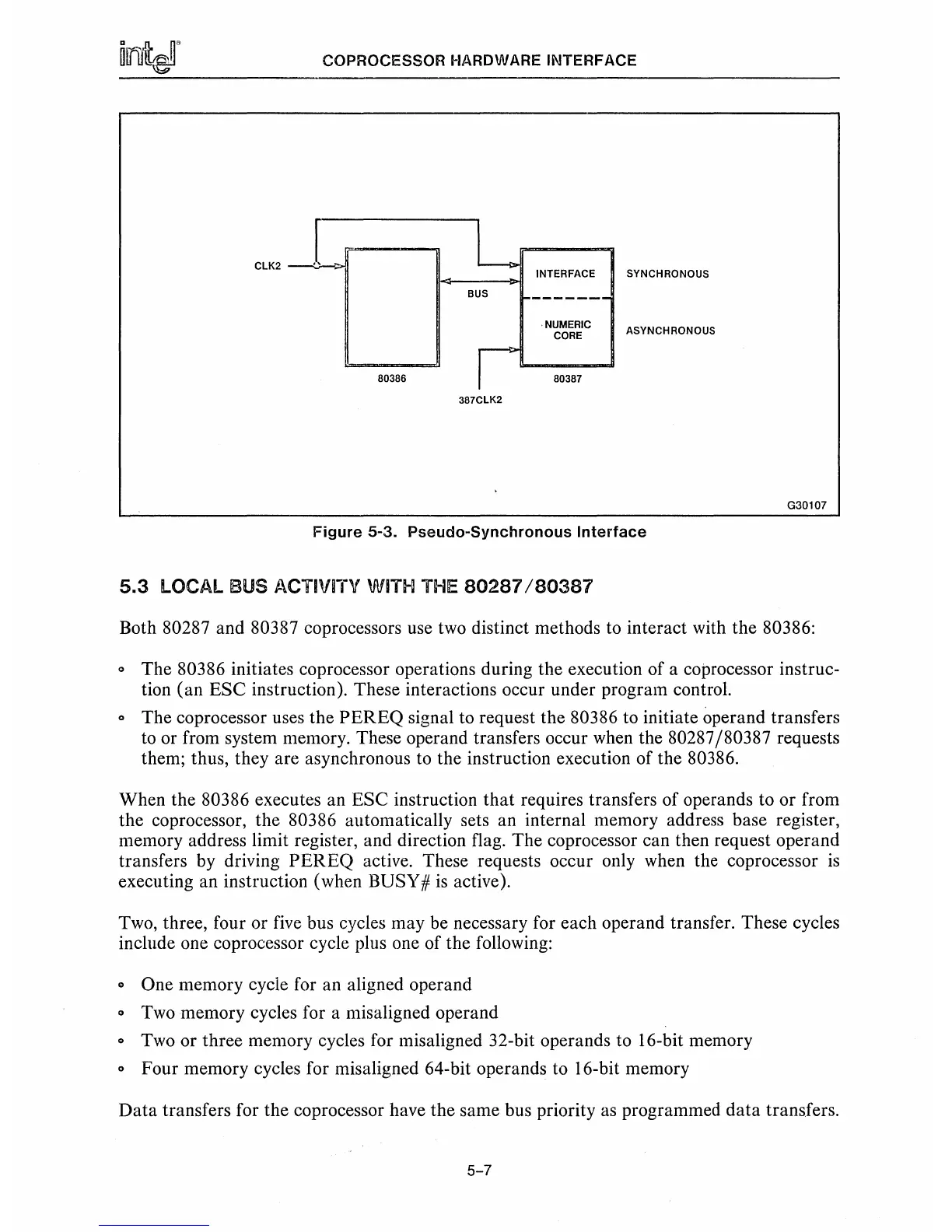

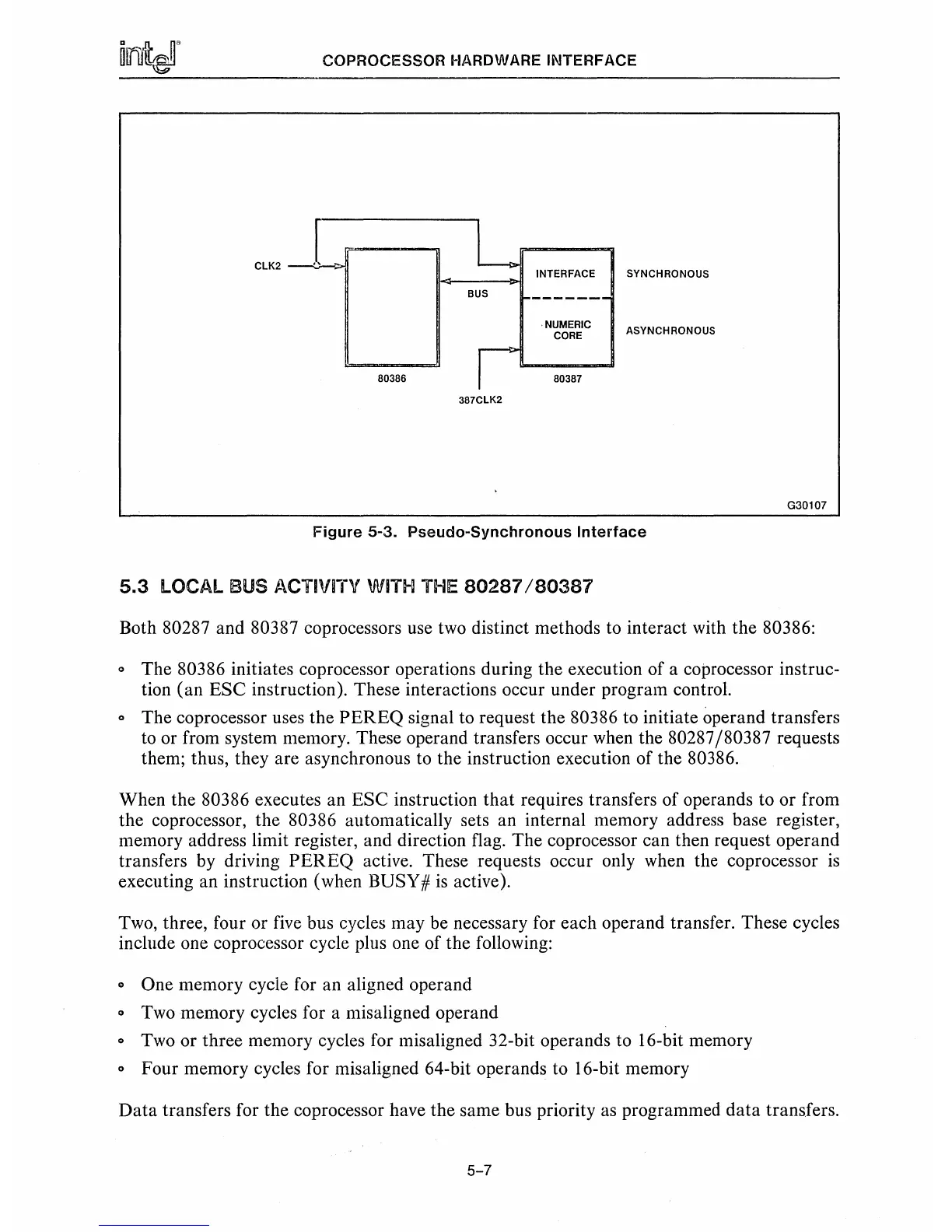

CLK2

INTERFACE SYNCHRONOUS

BUS

------

. NUMERIC

ASYNCHRONOUS

CORE

80386 80387

387CLK2

G30107

Figure

5-3.

Pseudo-Synchronous

Interface

5.3

LOCAL BUS ACTIViTV WiTH THE

80287/80387

Both 80287 and 80387 coprocessors use two distinct methods to interact with the 80386:

o The 80386 initiates coprocessor operations during the execution of a coprocessor instruc-

tion (an

ESC instruction). These interactions occur under program control.

o The coprocessor uses the

PEREQ

signal to request the 80386 to initiate operand transfers

to

or from system memory. These operand transfers occur when the 80287(80387 requests

them; thus, they are asynchronous to the instruction execution of the 80386.

When the

80386 executes an ESC instruction that requires transfers of operands to or from

the coprocessor, the

80386 automatically sets an internal memory address base register,

memory address limit register, and direction flag. The coprocessor can then request operand

transfers

by

driving

PEREQ

active. These requests occur only when the coprocessor

is

executing an instruction (when BUSY #

is

active).

Two, three, four or five bus cycles may be necessary for each operand transfer. These cycles

include one coprocessor cycle plus one of the following:

• One memory cycle for an aligned operand

• Two memory cycles for a misaligned operand

o Two or three memory cycles for misaligned 32-bit operands to 16-bit memory

o Four memory cycles for misaligned 64-bit operands to 16-bit memory

Data

transfers for the coprocessor have the same bus priority

as

programmed data transfers.

5-7

Loading...

Loading...