(No.YF139)2-37 2-38(No.YF139)

LCD_OPEN

R401

10k

CHRG_LED

D402

SMLA12BC4T-X

DRV_ACES

R405

10k

R406

3.3k

POFF_SW

KEY_C

D401

SML-A12UT-X

POW/CHRG

S412

NSW0198-001X

TRASH

21

34

REC_SW

PLAY_SW

S411

NSW0198-001X

LIGHT/INFO

21

34

ACES_LED

SJIG_RST

R407

6.8k

P_MEDIA

GND

KEY_A

REG_3.1V

D403

UDZS6.8B-X

S402

NSW0161-001X

LCD_OPEN

12

S403

NSW0099-001X

MOV/STIL

1

2

3

AUTO

NSW0198-001X

S404

21

34

LED_4.9V

S413

QSW1153-001

RESET

12

S401

NSW0260-001X

1

REC

2

PLAY

345

OFF

6

D404

SML-A12UT-X

USB HOST

HOST_LED

MENU

NSW0198-001X

S405

21

34

R408

22k

78

910

45

67

D406

OPEN

D407

OPEN

D405

OPEN

R409

OPEN

FRONT

UPPER

BOTTOM

REAR

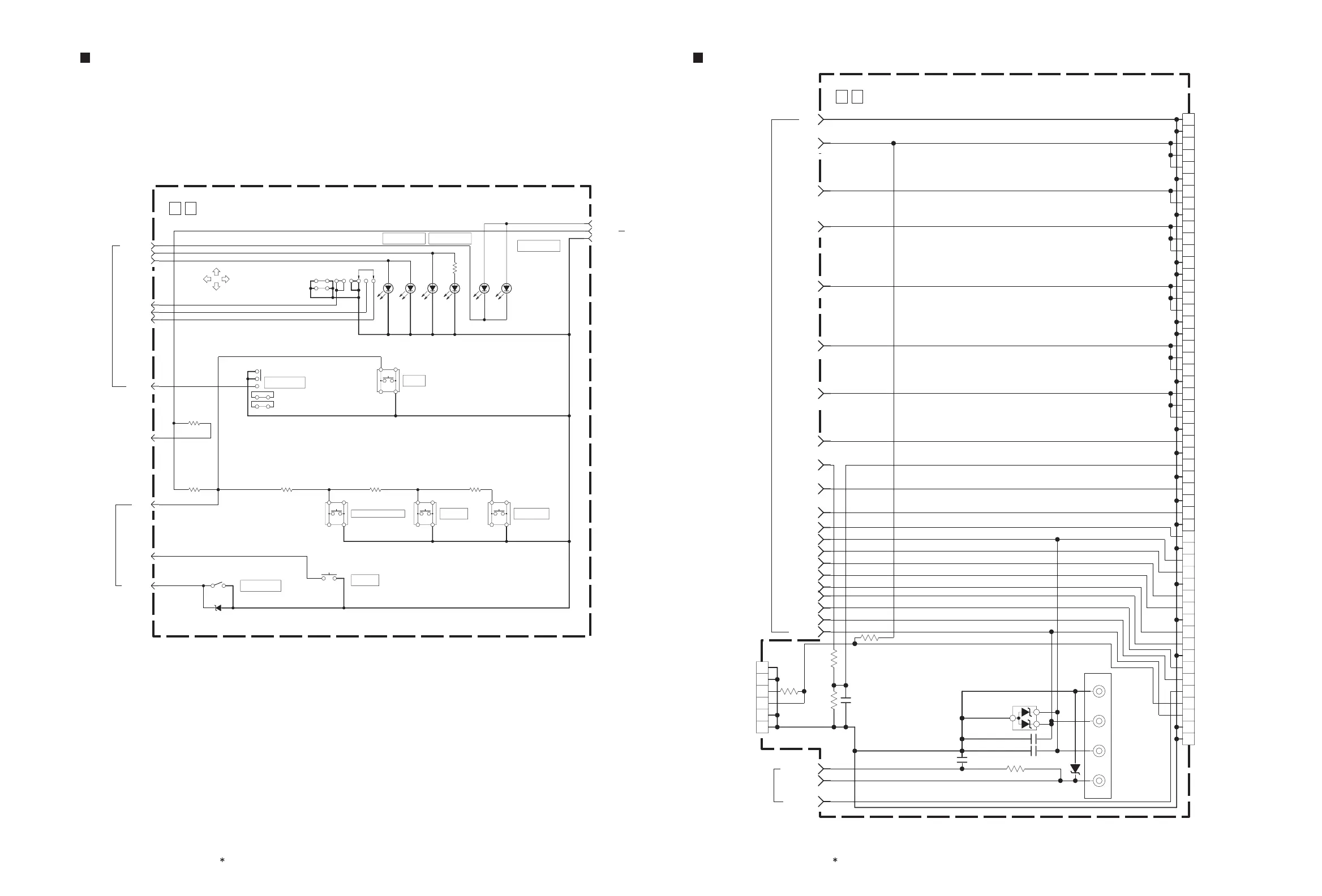

OPERATION

40

yf139_y30343001a_rev0.1

TO OPE IF(CN401)

TO OPE IF(CN401)

TO OPE IF(CN401)

TO OPE IF

(CN401,402)

TO OPE IF

(CN401,402)

OPERATION SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

[-]

[D]

[T]

[+]

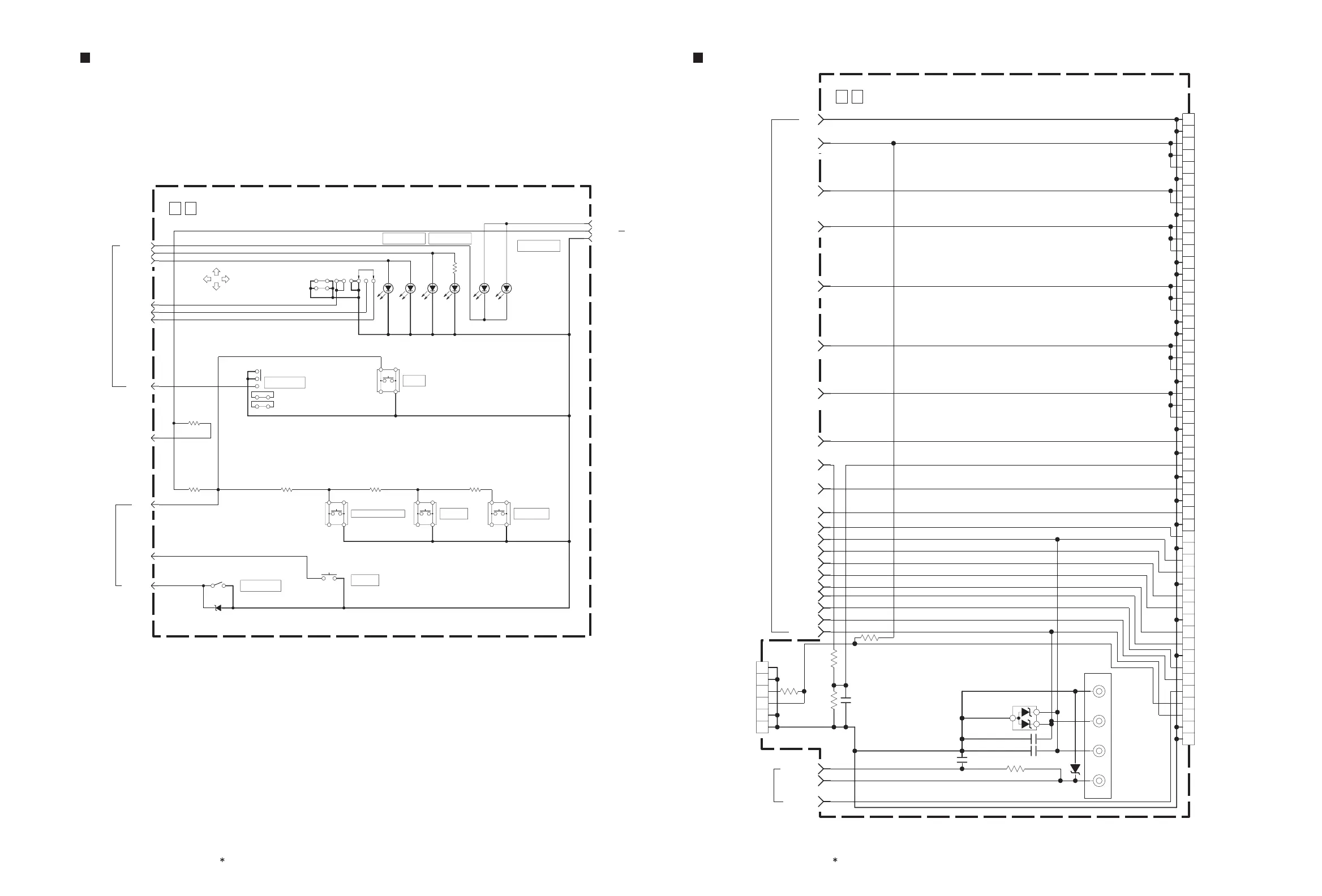

REG-CCD

SJIG_RST

DRV_3.3V

DATA_OUT

CAM_3.1V

REG_1.5V

REG_4.9V

ADP_L

CHRG_EVR

GND

D_BATT

REG_1.2V

T_BATT

CLK_OUT

REG_3.1V

AL_3.1V

REG_CS

I_MTR

UNREG

V_BATT

R601 10k

R602

3.3k

TP4

TP3

TP1

LY34726-001A

TP2

D601

EMZ6.8N-X

1

2

3

BATT+

BATT_CHK

R603 0

C601

0.1

C602

OPEN

C603

0.1

CN6001

QGF0508F1-53X

1 GND

2 GND

3 REG_3.1V

4 REG_3.1V

5 REG_3.1V

6 GND

7 CAM_3.1V

8 CAM_3.1V

9 GND

10 REG_4.9V

11 REG_4.9V

12 REG_4.9V

13 GND

14 GND

15 REG_1.5V

16 REG_1.5V

17 REG_1.5V

18 GND

19 GND

20 REG_1.2V

21 REG_1.2V

22 REG_1.2V

23 GND

24 DRV_3.3V

25 DRV_3.3V

26 DRV_3.3V

27 GND

28 AL_3.1V

29 GND

30 UNREGCHK

31 GND

32 REG+CCD

33 GND

34 REG-CCD

35 GND

36 ADP_L

37 GND

38 T_BATT

39 V_BATT

40 GND

41 I_MTR

42 SJIG_RST

43 GND

44 DATA_OUT

45 CLK_OUT

46 GND

47 REG_CS

48 CHRG_EVR

49 DC_CHEK

50 KEY_B

51 D_BATT

52 GND

53 GND

D602

UDZS16B-X

REG+CCD

R605

39k

R604

150k

C604

OPEN

DC_CHEK

CN6002

QGF0534F2-06X

1GND

2GND

3HARF_SW

4FULL_SW

5GND

6GND

BATTERY TERM

_0.5%

_0.5%

yf139_y40166001a_rev0.1

REAR(REAR IF)

50

TO TRIG SW

TO REG

TO REG

TO MAIN

(CN103)

REAR(REAR IF) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked () is not used.

Loading...

Loading...