XV-S40BK/XV-S42SL/XV-S45GD

XV-S30BK/XV-E100SL

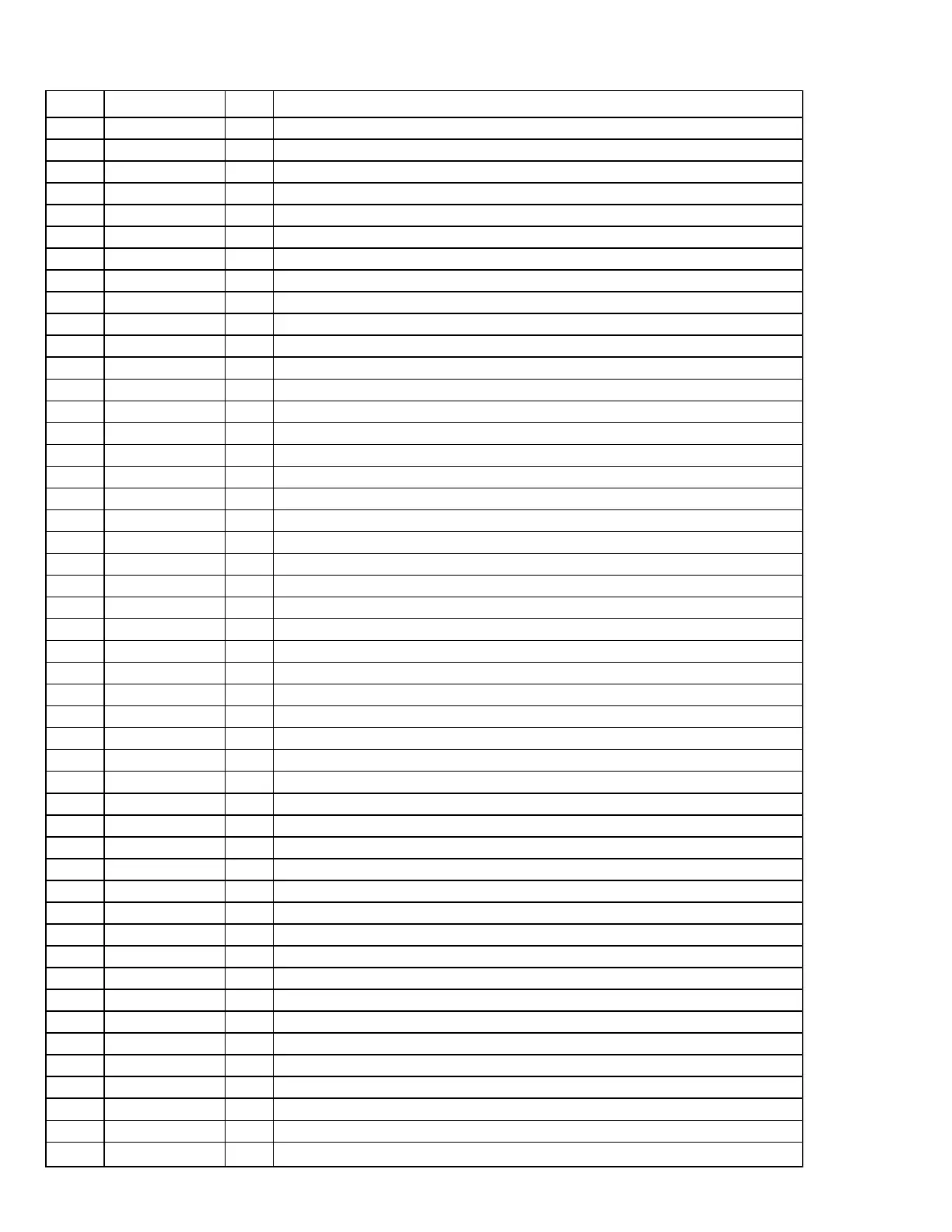

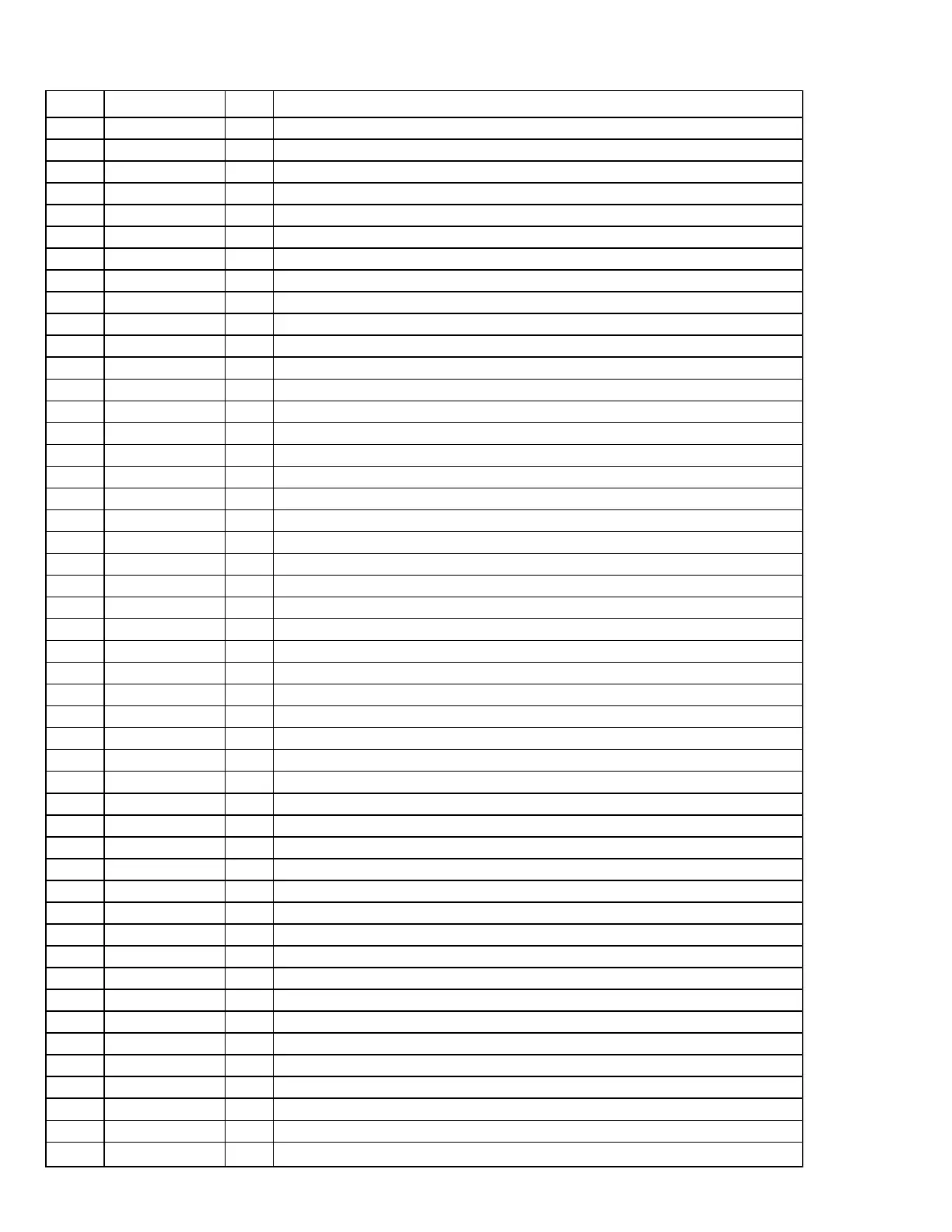

1-42

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

-

-

-

-

-

-

I/O

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

-

-

I/O

I/O

I/O

I/O

I/O

-

-

I/O

O

O

I

O

O

-

-

O

Pin No.

Symbol

VSS

NC

NC

NC

NC

NC

PIO0

VSS

VDD

PIO1

PIO2

PIO3

PIO4

PIO5

PIO6

PIO7

MDATA 0

MDATA 1

VDD

VSS

MDATA 2

MDATA 3

MDATA 4

MDATA 5

MDATA 6

MDATA 7

MDATA15

VDD

VSS

MDATA14

VDD

VSS

MDATA13

MDATA12

MDATA11

MDATA10

MDATA 9

VDD

VSS

MDATA 8

LDQM

SD-CLK

CLKSEL

MADDR9

MADDR8

VDD

VSS

MADDR7

I/O

Description

2.Pin function (ZIVA-4.1-PA2 : 2/5)

Connect to ground

Non connect

Non connect

Non connect

Non connect

Non connect

Programmable I/O terminal

Connect to ground

Power supply terminal 3.3V

Programmable I/O terminal

Programmable I/O terminal

Programmable I/O terminal

Programmable I/O terminal

Programmable I/O terminal

Programmable I/O terminal

Programmable I/O terminal

SDRAM data

SDRAM data

Power supply terminal 3.3V

Connect to ground

SDRAM data

SDRAM data

SDRAM data

SDRAM data

SDRAM data

SDRAM data

SDRAM data

Power supply terminal 3.3V

Connect to ground

SDRAM data

Power supply terminal 2.5

Connect to ground

SDRAM data

SDRAM data

SDRAM data

SDRAM data

SDRAM data

Power supply terminal 3.3V

Connect to ground

SDRAM data

SDRAM Lower or upper mask

SDRAM Clock

Selects SYSCLK or VCLK as clock source. Normal operation is to tie HIGH.

SDRAM address

SDRAM address

Power supply terminal 3.3V

Connect to ground

SDRAM address

Loading...

Loading...