84

Pin

#

Pin Name Type

Function

in Slave Mode

Function

in Master Mode

Notes

1 LSDP_TXRX

S=In

M=Out

Low Speed Data Port Output Low Speed Data Port Input LVTTL S/T

3 SC_TX_OUT

S=Out

M=Out

System Controller Bus (CBM)

Transmit Data Out

System Controller Bus (CBM)

Transmit Data Out

4mA, SLC

5 SC_RX_IN

S=In

M=In

System Controller Bus (CBM)

Receive Data In

System Controller Bus (CBM)

Receive Data In

LVTTL S/T

7 COMMAND_SEL

S=In

M=In

Command Mode Select In

(1= Command Mode,

0=Normal Mode)

Command Mode Select In

(1= Command Mode,

0=Normal Mode)

LVTTL S/T

9 IRQ#

S=Out

M=Out

Interrupt Request Out

(Active Low)

Interrupt Request Out

(Active Low)

4mA Open

Drain

11 RESET#

S=In

M=In

Asynchronous Reset In,

(Active Low)

Asynchronous Reset In,

(Active Low)

LVTTL S/T

12 SLAVE_SEL

S=In

M=In

M/S Mode Select In

(High = Slave Mode)

M/S Mode Select In

(Low=MasterMode)

LVTTL S/T

13 COMM_RX_DIG

S=In

M=In

DT Comm Bus External

Transceiver Receive Data In

DT Comm Bus External

Transceiver Receive Data In

LVTTL S/T

14 COMM_TX_DIG Output

DT Comm Bus External

Transceiver Transmit Data

Out

DT Comm Bus External

Transceiver Transmit Data

Out

LVTTL S/T

15 COMM_TX_EN Output

DT Comm Bus External

Transceiver Direction Out

(1=Transmit, 0=Receive)

DT Comm Bus External

Transceiver Direction Out

(1=Transmit, 0=Receive)

LVTTL S/T

18 COMM_RX_P

S=In

M=In

DT Comm Bus Internal

Receiver Differential Positive

In

DT Comm Bus Internal

Receiver Differential Positive

In

LVDS in+

19 COMM_RX_M

S=In

M=In

DT Comm Bus Internal

Receiver Differential

Negative In

DT Comm Bus Internal

Receiver Differential

Negative In

LVDS in–

22 COMM_TX_M Output

DT Comm Bus Internal

Transmitter Differential

Negative Out

DT Comm Bus Internal

Transmitter Differential

Negative Out

LVDS out–

23 COMM_TX_P Output

DT Comm Bus Internal

Transmitter Differential

Positive Out

DT Comm Bus Internal

Transmitter Differential

Positive Out

LVDS out+

26 OSC_OUT Output Crystal Output Crystal Output Crystal Buffer

28 OSC_IN

S=In

M=In

Crystal Input Crystal Input Crystal Buffer

30 TEST

S=In

M=In

Factory Test Mode Select

(1=Test, 0= Normal Oper.)

Factory Test Mode Select

(1=Test, 0= Normal Oper.)

LVTTL S/T

32 HSDP_DATA

S=In

M=Out

High Speed Data Port Data

Input

High Speed Data Port Data

Output

Out= 4mA, SLC

In=LVTTL S/T

34 HSDP_CLK

S=In

M=Out

High Speed Data Port Clock

Input

High Speed Data Port Clock

Output

Out= 4mA, SLC

In=LVTTL S/T

36 HSDP_EN

S=Out

M=In

High Speed Data Port Enable

Output

High Speed Data Port Enable

Input

Out= 4mA, SLC

In=LVTTL S/T

37 I2S_DATA

S=In

M=Out

I2S Digital Port Data In

I2S Digital Audio Port Data

Out

Out= 4mA, SLC

In=LVTTL S/T

Pin

#

Pin Name Type

Function

in Slave Mode

Function

in Master Mode

Notes

39 I2S_SCLK

S=In

M=Out

I2S Digital Audio Port Bit

Clock In

I2S Digital Audio Port Bit

Clock Out

Out= 4mA, SLC

In=LVTTL S/T

41 I2S_LRCLK

S=In

M=Out

I2S Digital Audio Port

Left/Right Clock In

I2S Digital Audio Port

Left/Right Clock Out

Out= 4mA, SLC

In=LVTTL S/T

43 I2S_OCLK

S=In

M=Out

I2S Digital Audio Port

Oversample Clock

(not used - connect to Gnd???)

I2S Digital Audio Port

Oversample Clock Out

Out= 4mA, SLC

45 SAII_CLK

S=Out

M=In

SAII Port Clock Output SAII Port Clock Input

Out= 4mA, SLC

3.3V S/T

47 SAII_DATA

S=Out

M=In

SAII Port Data Output SAII Port Data Input

Out= 4mA, SLC

In=LVTTL S/T

48 SAII_REQ

S=In

M=Out

SAII Port Request Input SAII Port Request Output

Out= 4mA, SLC

In=LVTTL S/T

Pin# Pin Name Type

Function

in Slave Mode

Function

in Master Mode

Notes

4, 8, 17, 20,

27, 33, 40, 46

VDD PWR +3.3V Supply Voltage +3.3V Supply Voltage

2, 6, 10, 16,

21, 24, 25, 29,

31, 25, 38, 42,

44

VSS GND Digital Ground Digital Ground

Notes: All Inputs are 3.3V LVTTL compatible; S/T = Schmitt Trigger inputs; SLC = Slew Rate Controller Output

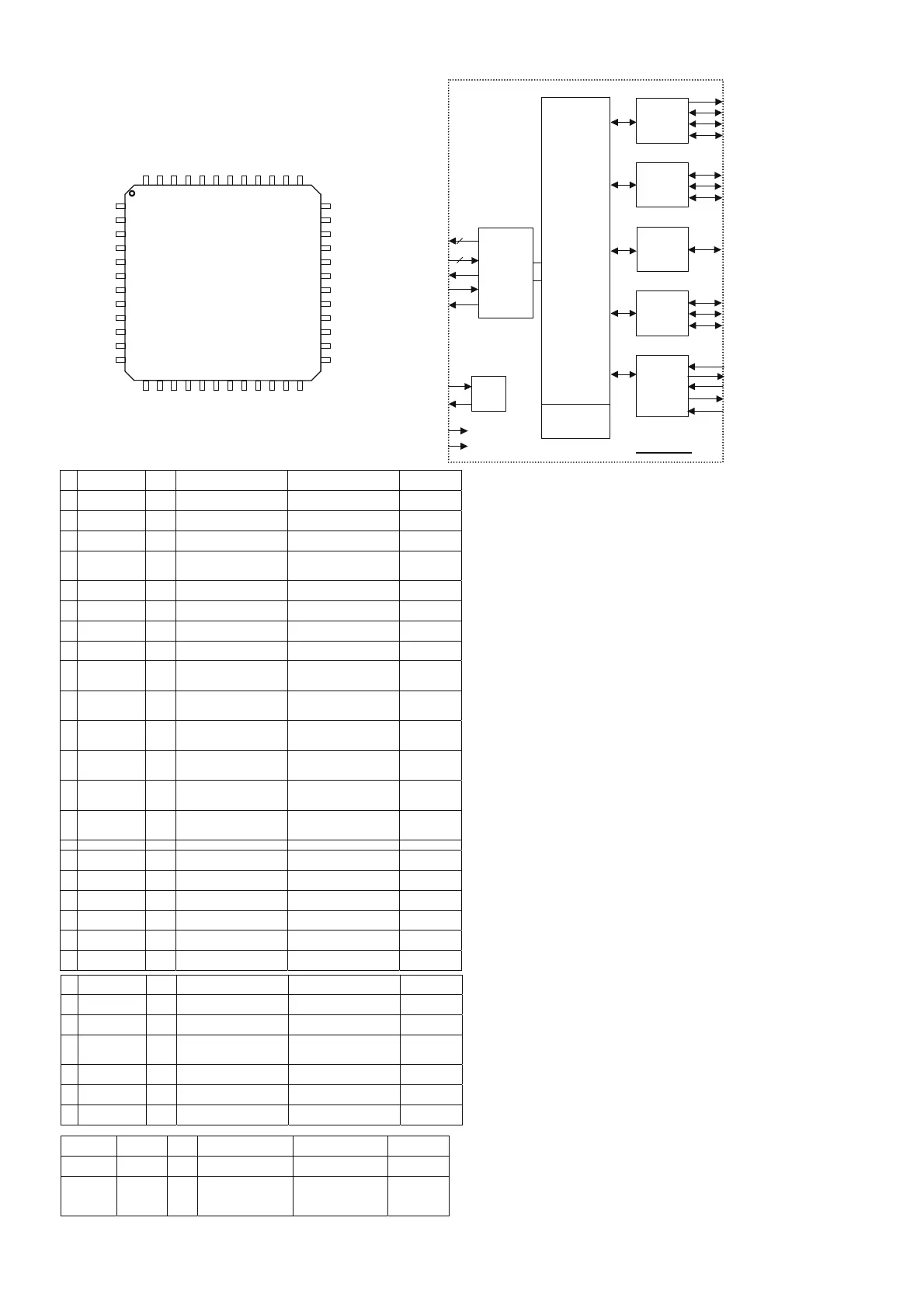

COMM ENGINE

Inter-IC

Sound

(I2S)

High Spd

Data Port

(HSDP)

Low Spd

Data Port

(LSDP)

Sys Ctrlr

(CBM)

Bus I/F

SAII

I2S_OCLK (Mstr only)

I2S_LRCLK (M=o; S=i)

I2S_SCLK (M=o; S=i)

I2S_DATA (M=o; S=i)

HSDP_EN (M=o; S=i)

HSDP_CLK (M=o; S=i)

HSDP_DATA (M=o; S=i)

LSDP_TXRX (M=o; S=i)

SAII_EN (M=i; S=o)

SAII_CLK (M=o; S=i)

SAII_DATA (M=o; S=i)

SC_RX_IN

SC_TX_OUT

RESET~

ERR_IRQ~

COMMAND_SEL

TX+ / TX-

SLAVE_ SEL

OSC_OUT

RAM

TX_DIGL_OUT

TX_EN~

RX_DIGL_IN

RX+ / RX-

OSC_IN

OSC

COMM I/F

TEST

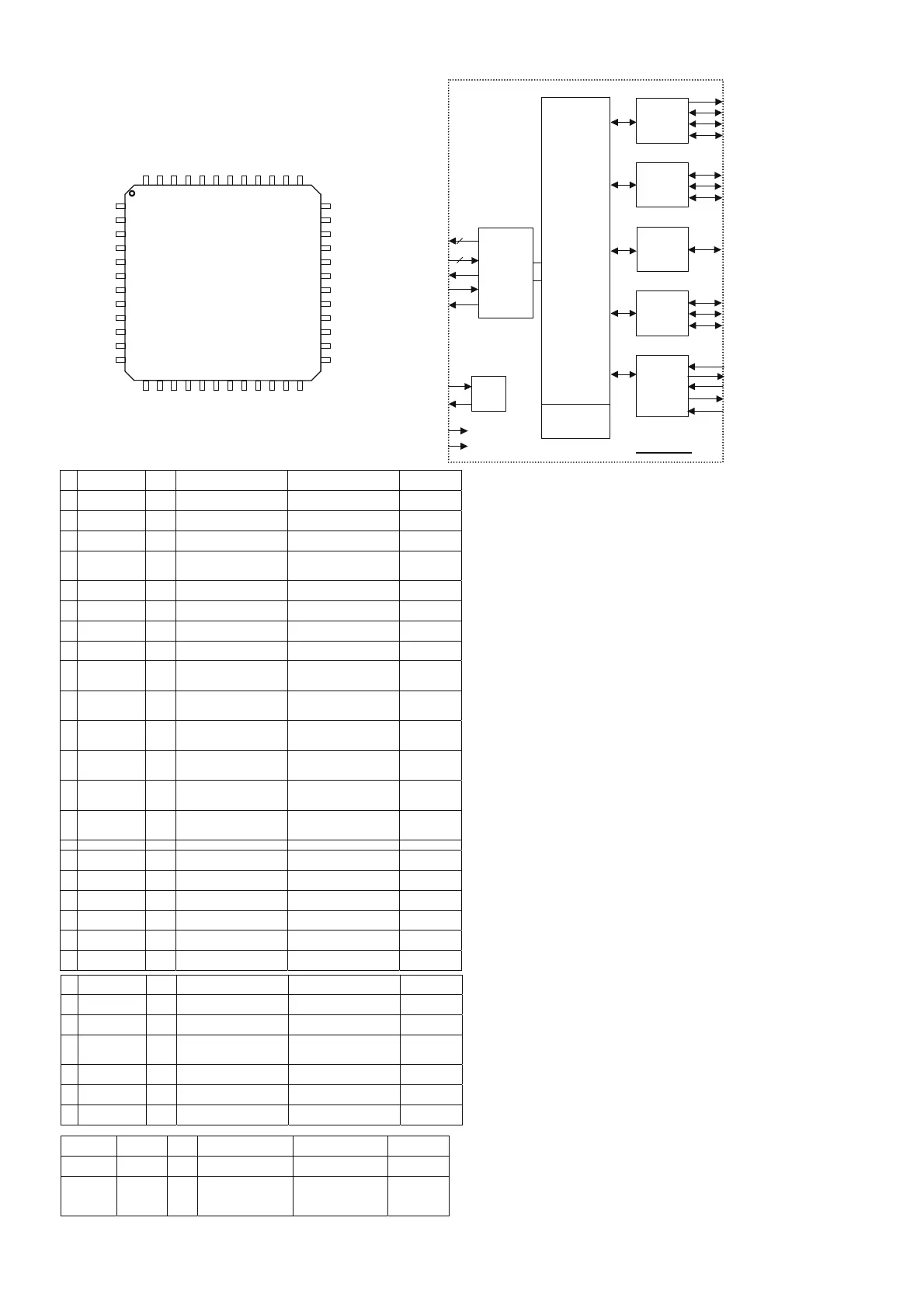

2

2

XMDTIC

13

14

15

16

17

18

19

20

21

22

23

24

COMM_RX_DIG

COMM_TX_DIG

COMM_RX_P

COMM_RX_M

COMM_TX_M

COMM_TX_P

VDD

VDD

VSS

VSS

VSS

COMM_TX_EN

1

2

3

4

5

6

7

8

9

10

11

12

LSDP_TXRX

SC_TX_OUT

SC_RX_IN

COMMAND_SEL

IRQ#

RESET#

SLAVE_SEL

VDD

VDD

VSS

VSS

VSS

XMDTIC

42

38

I2S_DATA

I2S_SCLK

I2S_LRCLK

I2S_OCLK

SAII_CLK

SAII_DATA

SAII_EN

VDD

VDD

VSS

VSS

VSS

48

47

46

45

44

43

41

40

39

37

OSC_OUT

OSC_IN

TEST

HSDP_DATA

HSDP_CLK

VDD

VDD

VSS

VSS

VSS

34

33

32

31

30

29

28

27

26

25

HSDP_EN

36

VSS

35

IC51 : XMDT (SR5002/U only)

Loading...

Loading...