5-1-3.

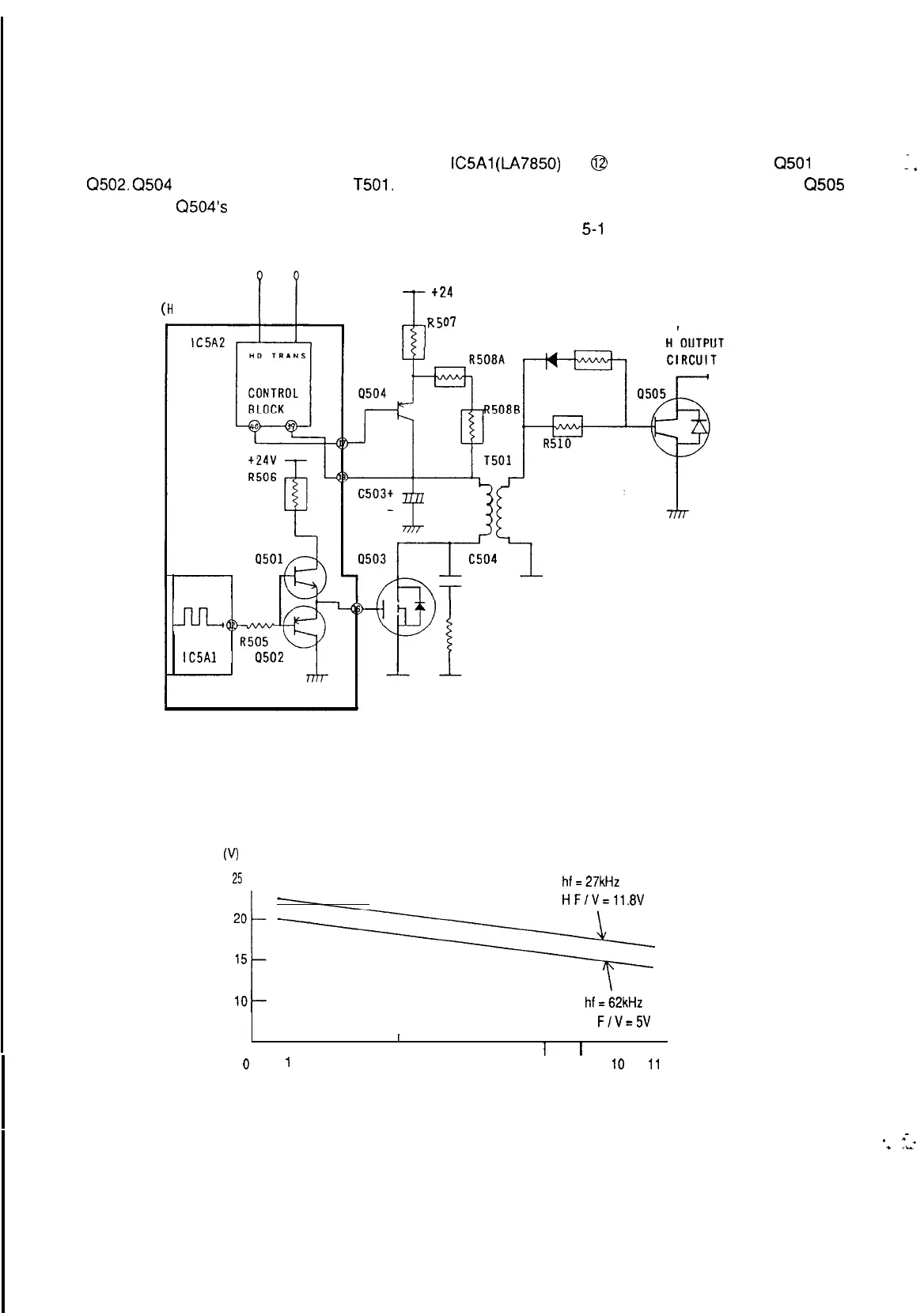

H DRIVE Circuit

The horizontal pre-drive pulse is generated from

IC5Al

(LA7850)

pin @ and input to Q503 via

Q501

and

Q502.

Q504

provides the voltage to

T501.

This voltage is regulated by Q504 to compensate for Q505

power loss. Q504’s collector voltage is controlled by both H F/V and H size voltage. The relationship of

Q504 collector voltage, H FN voltage and H size voltage is shown Fig

5-l

-6.

I

.

PWE-366A

(H

OSC UNIT)

+24

R507

TO

0501 R511

ti,

R509

IC5Al

Q502

(Fig 5-l -5) H Drive circuit

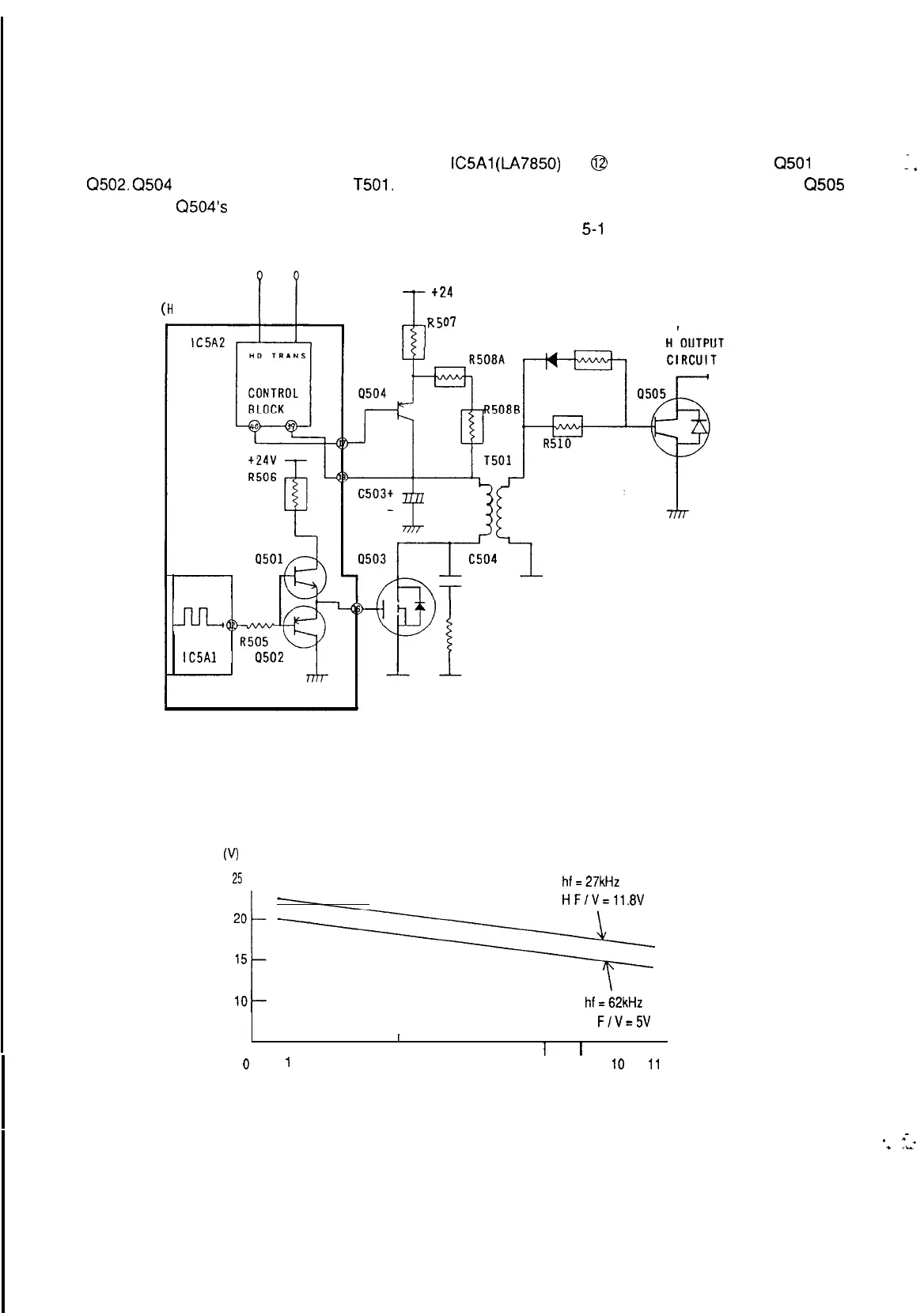

Q504

COLLECTOR

VOLTAGE

(VI

25

t

hf=27kHz

HF/V=11.8V

lOI-

hf=62kHz

H

F/V=5V

I

I I

1

I

I

I

I

I

I I

I

I

I

I

I

0

1

2

3

4 5 6

7

8

9 IO

11

(Fig 5-l-6) The Relationship Q504 collector voltage, H FN voltage and H SIZE voltage

.

--_

*

,_

61

Loading...

Loading...